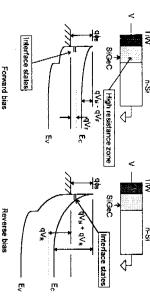

Fig. 7. Band diagrams of Schottky diode with defective SiGeC alloy. The band offset in conduction band, which is very small, is neglected.

#### है. ड्रें NOTICE: THIS MATERIAL MAY BE PROTECTEI BY COPYRIGHT LAW (TITLE 17 U.S. CODE)

### SUMMARY

C-V and I-V measurements were performed for TiW/SiGeC Schottky contacts, with various crystal quality of epitaxial SiGeC on Si. No significant difference was observed from C-V characteristics among various samples. For defective SiGeC films, large ideality factor and series resistance, and large leakage current were observed from I-V curves. This is attributed to carbon complexes which act as scattering centers in the alloy and traps in the bandgap.

### REFERENCES

- 1. S. C. Jain, H. J. Osten, B. Dietrich, and Hrücker, Semicond. Sci. Technol. 10, 1289 (1995).

- J. Mi, P. Warren, P. Letourneau, M. Judelewicz, M. Gailhanou, M. Dutoit, C. Dubois, and J. C. Dupuy, Appl. Phys. Lett. 67, 259 (1995).

- 3. L. D Lanzerotti, A. St. Amour, C. W. Liu, J. C. Sturm, J. K. Watanabe, and N. D. Theodore, IEEE Electron Device Lett. 17, 334 (1996).

- 4. S. K. Ray, S. John, S. Oswal, and S. K. Banerjiee, 1996 IEDM Tech. Digest, p. 261

- F. Y. Huang, S. G. Thomas, M. Chu, and K. L. Wang, 1996 IEDM Tech. Digest, p. 665.

R. A. Soref, Z. Atzman, F. Shaapur, M. Robinson, and R. Westhoff, Optics Lett. 21,

- 6. R. A. Soref, Z. Atzman, F. Shaapur, M. Robinson, and R. Westhoff, Optics Lett. 21, 345 (1996).

- 7. S. S. Iyer, K. Eberl, M. S. Groorsky, F. K. LeGoues, and T. C. Tsang, Appl. Phys. Lett. 60, 356 (1992).

- 8. J. Mi, P. Warren, P. Letourneau, M. Jedelewicz, M. Gailhanou,, M. Dutoit, C. Dubois, and J. C. Dupuy, Appl. Phys. Lett. 67, 259 (1995)

- Annual Book of ASTM Standards (ASTM, Philadelphia, 1981) F 120, p. 543

- 10 W. G. Spitzer, Phys. Rev. 113, 133 (1959).

- 11. J. Candelaria, J. K. Watanabe, N. D. Theodore, R. B. Gregory, D. K. Schroder, L. M. Stout, and N. G. Cave, Mat. Res. Soc. Symp. Proc. 321, 473 (1994).

- 12. J. Mi, P. Warren, M. Gailhanou, J.-D. Ganiere, M. Dutoit, P.-H. Jouneau, and R. Houriet, J. Vac. Sci. Technol. B 14, 1660 (1996).

- 13. S. M. Sze, Physics of Semiconductor Devices (Wiley, New York, 1981), Chap. 5

- 14. F. D. Auret, M. Nel, and N. A. Bojarczuk, J. Vac. Sci. Technol. B 4, 1168 (1986).

- 15. G. Davis and R. C. Newman, *Carbon in Monocrystalline Silicon*, in <u>Handbook on Semiconductor</u>, Vol. 3, edited by T. S. Moss (Elsevier, New York, 1994).

# The Growth of $\beta$ -SiC on Si and Poly-Si on $\beta$ -SiC by Rapid Thermal Chemical Vapor Deposition

C. W. Liu\* and J. C. Sturm\*

\*National Taiwan University, Dept. of Electrical Engineering, Taipei, Taiwan \*Princeton University, Dept. of Electric Engineering, Princeton, New Jersey

### ABSTRACT

The growth properties of  $\beta$ -SiC on (100) Si grown by rapid thermal chemical vapor deposition, using a single precursor (methylsilane) without an initial surface carbonization step, were investigated. An optimun growth temperature at 800°C was found to grow single crystalline SiC. The single crystalline SiC films were used to be the buffer layers for the growth of subsequent poly Si films. For the poly Si grown at low temperature (625°C), the (110) Si diffraction was found to be the dominant peak in the X-ray diffraction spectra at the initial growth stage, while the poly Si grown on oxide was dominated by (111) texture. A small average misfit (4 %) between (110) Si planes and (100) SiC planes was proposed to explain this effect. To apply the Si/SiC/Si multilayers, SiC/Si heterojunction bipolar transistors (HBT's) were fabricated and compared to Si bipolar junction transistors.

### INTRODUCTION

Despite the success with Si/SiGe/Si heterojunction bipolar transistors(HBT's), there is still a strong desire for a widegap emitter material on Si. Such a widegap emitter on a Si base could yield devices with better high temperature performance than Si/SiGe HBT's (due to higher bandgap) and might be easier to be integrated[1]. Recently, the Si<sub>1-x</sub>C<sub>x</sub> alloys have been studied to serve this purpose[2]. However, only a small fraction of C ( $\leq 2\%$ ) can be incorporated into Si to form device quality materials and as a result, very limited band offset can be obtained. A large band offset can be used, if  $\beta$ -SiC (bandgap 2.2 eV)/Si heterostructures can be fabricated, despite of 20 % mismatch of lattice constants and 8 % mismatch of thermal expansion coefficients between  $\beta$ -SiC and Si. We, therefore, performed the Si/ $\beta$ -SiC heterostructural growth on (100) Si substrates by rapid thermal chemical vapor deposition, and applied this technology to fabricated Si/SiC HBT's.

### β-SiC GROWTH on Si

The SiC films were deposited on tilted (4° towards < 110 >) and non-tilted Si substrates (within 1° off) with a diameter of 100 mm by Rapid Thermal Chemical Vapor Deposition (RTCVD) at a growth temperature of 700-1100°C. The growth pressure was 1 torr with a 1.5 sccm methylsilane (SiCH<sub>8</sub>) flow and a 500 sccm hydrogen flow. The growth temperature(700-800°C) was accurately determined by the infrared transmission technique[3]. Growth temperatures higher than 800°C were controlled by the tungsten-balogen lamp power which was previously calibrated with a thermocouple welded onto a Si wafer. The SiC thickness was measured by fitting the optical reflection spectra from 500 to 700 nm with the SiC index of refraction of 2.6. The growth rate in the range 700-800°C varied exponentially with the inverse of temperature and the activation energy for this surface-reaction-limited growth was 3.6 eV. This is higher than that of pure silicon growth using silane as a precursor (~ 1.7 eV)[4] and may reflect the strong C II bonding energy.

At a higher growth temperature (800: 1100°C), the growth rate had a weak temperature dependence, indicating mass-transport-limited growth.

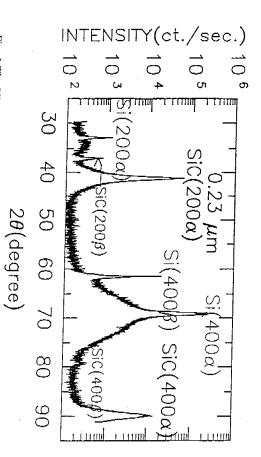

(400) peak was as small as 0.75°, which was similar to the value  $(0.65-0.7^{\circ})$  of 0.3  $\mu m$ indicates the poor crystallinity of the 750 °C films. The crystallinity can be improved by some slightly in-plane rotated textures and very fine spots in the < 110 > direction. This about 1.6°). But the TEM diffraction pattern of the same sample showed evidence of unresolved  $CuK_{a1}$  and  $CuK_{a2}$  (400) peak (Full Width Half Maximum, FWHM, of 20 is (transmission electron microscope). For the films grown at 750°C, the XRD spectrum of cm<sup>-1</sup> and a sharp peak 510 cm<sup>-1</sup>. The 510 cm<sup>-1</sup> peak is associated with the Si substrates, an absorption peak at 796 cm<sup>-1</sup> (TO phonon absorption) with a FWHM of 50 cm<sup>-1</sup>, which transform infrared spectra of a  $0.23~\mu m$   $800^{\circ}\mathrm{C}$  grown film on non-tilted substrates displayed similar thickness grown by conventional high temperature growth techniques. The Fourier also showed very high densities of stacking faults and dislocations, similar to the films of The TEM diffraction pattern also displayed a well-defined single crystalline feature. TEM commercial (100) SiC on Si[5], which was grown at a much higher temperature ( $\geq 1300^{\circ}$ C) film grown at 800 °C on non-tilted substrates showed that the FWHM of unresolved  $CuK_o$ increasing the growth temperature to 800° ( . The XRD spectrum (Fig. 1) of a 0.23  $\mu$ m SiC a 80nm film on non-tilted substrates exhibited a single crystalline feature with a broad optimum growth temperature for the single crystalline 3-SiC. The 800 °C-grown films were spectrum of the films grown at 1000 °C and 1100 °C, however, reveals extra (111) and phonon scattering ( $\sim 970~{\rm cm}^{-1}$ ) and interface defects between SiC and Si[6]. The XRD not SiC epilayers. The peak near 960 cm<sup>-1</sup> is probably due to a combination of the LO is similar to that of the film grown by conventional high temperature growth methods. The Raman spectrum of the same sample showed a broad peak at 960 cm<sup>-1</sup> with FWHM of 60 used to fabricated Schottky diodes with reverse breakdown voltage of 59 V[7]. (220) peaks, indicating the growth of polycrystalline material. Therefore, the 800 °C is the The crystallinity of the films was studied by XRD (X-ray diffraction) and TEM

### Poly-Si GROWTH on SiC

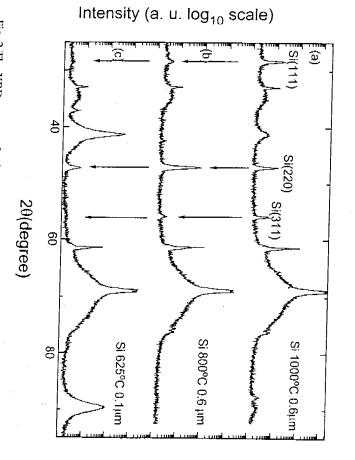

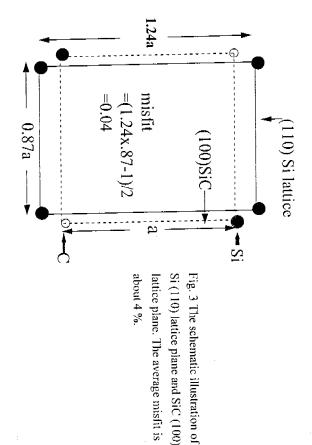

The poly Si films were deposited on the 800°C-grown SiC buffers at the temperature of 625 – 1000°C at 6 torr using dichlorosilane(26 secm) or silane(2 secm) with hydrogen flow rate of 3 slpm. The same growth conditions on Si substrates yield to single crystalline Si layers. At high growth temperature (800 – 1000°C), the (110), (111), and (311) textures of 0.6 µm poly Si grown by dichlorosilane have been observed by XRD(Fig. 2), and the relative contents of (311) and (111) decrease as the growth temperature decreases, very similar to the poly Si growth on oxide with similar thickness[8]. For poly Si grown on oxide at low temperature (\$700°C), the 0.6 µm poly Si film was dominated by (111) textures[8]. However, the poly Si with a thickness of 0.1 µm grown at 625°C on the SiC buffer using the silane precursor exhibits only (110) texture without diffraction peaks from other textures such as (111) and (311) in the XRD spectrum, but the (400) peak might be hidden behind the (400) Si peak of the substrate. The dominating diffraction of (110) texture in thin play Si on SiC can be understood by the small misfit of 4% (area average of two transverse direction) between (110) Si plane and (100) SiC plane as shown in Fig. 3, which makes it possible to grow single crystalline Si. However, due to the (100) Si substrate interference, the single crystalline growth of the epitaxial Si can not be confirmed. The poly grown Si

Fig. 1 The XRD spectrum of a 0.23  $\mu m$  single crystalline SiC film grown on (100) Si at 800 °C.

Fig. 2 The XRD spectra of poly Si films grown on (100) SiC at (a) 1000, (b) 800, and (c) 625 °C.

on SiC will be used as the obmic contact material in SiC/Si IIBT's

## SiC/Si HETEROJUNCTION APPLICATIONS

with  $SiO_2$  deposited by plasma deposition at 350 °C. Before contact metallization, the  $8\%O_2$  in CF<sub>4</sub> for SiC). The devices were isolated by plasma-etched mesas and passivated process, which was detailed in [10]. The base contact was established by boron implant thus should increase the current gain. The transistors were fabricated using a simple mesa n-Si emitter and the n<sup>+</sup>-Si emitter. The poly n<sup>+</sup> Si emitter on the SiC layer grown at 800°C there is an additional 2000  $\Lambda$  unintentionally doped SiC layer (n =  $10^{18} \mathrm{cm}^{-3}$ ) between the a Si control device (Si bipolar junction transistors) and a SiC/Si HBT. In the SiC/Si HBT, the wide bandgap emitter material of Si/SiC HBT's. Fig. 4 displays the layer structures of devices. The single crystalline  $\beta$ -SiC grown at 800 °C on (100) Si substrates was used for technique at 1000 °C on (111) Si substrates[9]. However, the high temperature process of emitter size was  $60\mu m$  x  $60\mu m$  for both HBT's and BJT's. wafers were given a RCA clean, and annealed at 700°C for 30 min in a forming gas. The Before base implantation, the emitter mesas were formed by plasma etching (SF $_6$  for Si and layers. The n-SiC emitter should block back-injected hole current (base current) ideally and in the SiC/Si HBT structure was used to form better ohmic contacts than directly on SiC 1000 °C would produce excessive back diffusion and prevent the integration with other Si A current gain of 800 has been obtained by Si/J-SiC-HBT's grown by a special

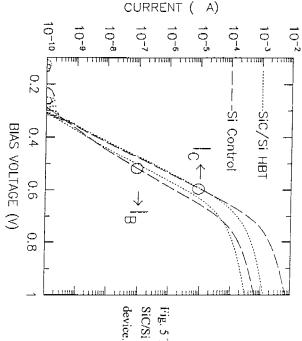

structures. The base currents also showed near-ideal behavior with ideality factors of 1.2 of the HBT's. This is thought to result from the SiC layer in the emitter. Furthermore, of being the barrier to stop the hole currents. Note also the apparent high series resistance recombination centers for back-injected holes and thus increased the hole currents, instead the Si BJT's, was probably due to the interface defects between Si and SiC, which acted as than thoses of Si BJT's. The increase of base currents in the SiC/Si HBT's, compared to current gain  $(I_c/I_b)$  was not observed. because the base currents of SiC/Si HBT's was higher and 1.1 for Si BJT's and SiC/Si HBT's, respectively. However, the desired enhancement of same absolute magnitude. This result is expected, because both devices have the same base for both devices showed same voltage  $(V_{be})$  dependence with ideality factor of 1.0 and the voltage (Gummel plot). The collector-base voltage is fixed at 2 V. The collector currents gam, a passivation technology of the interface will be desired in the future. emitter region. To reduce the defect density at the interface and to increase the current (surface). This is further evidence that the base current is occurring within the n-type is occurring in a neutral device region, and not in a space charge region or a device edge the improvement in the ideality factor in the HBT's indicates that the excess base current Fig. 5 shows the base current and collector current as a function of the emitter-base

## SUMMARY AND ACKNOWLEDGMENTS

Si/ $\beta$ -SiC heterostructure has been grown at 800°C on Si. The growth temperature of 800 °C was optimum for single crystalline SiC layers on Si (100) substrates. The thin (0.1  $\mu$ m) poly Si grown on SiC at 625°C has dominating (110) textures, in contrast to the growth on oxide, where (111) textures dominate. The SiC/Si HBT's has been fabricated,

Si BJ

| $n^{+}(10^{19} cm^{-3}) - Si collector \sim 2\mu m$ | $n(10^{17} cm^{-3}) - Si collector \sim 3000 /$ | $p^{+}(10^{19} cm^{-3}) - Si base \sim 600 \text{ Å}$ | $n(10^{17} cm^{-3}) = Si \text{ emitter} \sim 3000 \text{ Å}$ | $n^{+}(10^{18} cm^{-3})$ — Si emitter ~ 2000 Å |

|-----------------------------------------------------|-------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|

| (1000°C)                                            | (800°C)                                         | (700°C)                                               | (800 °C)                                                      | (800°C)                                        |

Fig. 4 Layer structures of a Si bipolar transistors and a SiC/Si HBT. There is an additional SiC layer between the n-Si emitter and the n'-poly Si emitter in the SiC/Si HBT.

< 100 > non-tilted a Si substrates

### SiC/Si HBT

| (1000°C) | $n^{+}(10^{19}cm^{-3}) - Si collector \sim 2\mu m$                |

|----------|-------------------------------------------------------------------|

| (800°C)  | $n(10^{17} cm^{-3})$ – Si collector $\sim 3000 \text{ Å}$         |

| (700°C)  | $p^{+}(10^{19}cm^{-3}) - Si base \sim 600 \text{ Å}$              |

| (800°C)  | $n(10^{17} cm^{-3}) - Si emitter \sim 3000 \text{ Å}$             |

| (800°C!) | $n^{+}(10^{18}cm^{-3}) - SiC \text{ emitter} \sim 2000 \text{ Å}$ |

| (800°C)  | $n^{+}(10^{18} cm^{-3}) - Si cmitter \sim 2000 \text{ Å}$         |

< 100 > non-tilted n Si substrates

Fig. 5 The Gummel plots of a SiC/Si HBT and a Si control

but the density of interface defects should be further reduced for desired SiC/Si HBT performance. The TEM assistance of Dr. E.A. Fitzgerald of ATT Bell Labs, and Prof. P. Pirouz and Dr. J. W. Yang of Case Western Reserve University are gratefully appreciated. The support of the US office of Naval Research (N000121-90-J-1316) is gratefully acknowledged. One of the authors (C. W. Liu) would like to thank the support of National Science Council of ROC (NSC 86-2221-E-002-089).

### REFERENCES

- T. K. Ning and D. D. Tang, Proc. IEEE, 74, p.1669 (1986).

- 2. C. Y. Lin and C. W. Liu, to be published in Appl. Phys. Lett., Mar., (1997).

- 3. J. C. Sturm and P. V. Schwartz, E. J. Prinz, and H. Manoharan, J. Vac. Sci. Technol. B 9 p. 2014 (1991)

- 3, **9**, p. 2011 (1991)

- J. L. Regolini, D. Bensahel, J. Mercier, and E. Scheid, Appl. Phys. Lett., 54, p.658 (1989).

- 5. I. Golecki, F. Reidinger, and J. Marti, Appl. Phys. Lett., 60, p.1703(1992).

- Z. C. Feng, A. J. Mascarenhas, W. J. Choyke, and P. A. Powell, J. Appl. Phys., 64, p. 3176 (1988).

- 7. C. W. Liu and J. C. Sturm, submitted to J. Appl. Phys., Feb. (1997)

- 8. T. I. Kamins and T. R. Class, Thin Solid Films, 16, p. 147(1973)

- 9. T. Sugii, T. T. Ito, Y. Furunnura, M. Doki, F. Mieno, and M. Maeda, IEEE Electron Device Lett., 9, p. 87(1988)

- 10. J. C. Sturm and E. J. Prinz, IEEE Electron Device Lett., 12, p. 303(1991)

# HIGH PERFORMANCE HIGH DIELECTRIC CONSTANT FILMS DEPOSITED BY DUAL SPECTRAL SOURCE RAPID ISOTHERMAL ASSISTED METALORGANIC CHEMICAL VAPOR DEPOSITION (MOCVD)

Y. Chen\*, R.Singh\*\*, S.DeBoer and R.P.S. Thakur\*\*\*

- \*Department of Electrical and Computer Engineering, Clemson University, Clemson, SC 29634

- \*\* Department of Electrical and Computer Engineering, and Material Science and Engineering Program, Clemson University, Clemson, SC 29634, singh@ces.clemson.edu

- \*\*\* Micron Technology Inc., Boise, ID 83706

### ABSTRACT

Dual spectral source assisted MOCVD is an ideal technique for the deposition of high dielectric constant materials as well as other electronic and optical materials. Tungsten halogen lamps and a deuterium lamp are used as the sources of optical and thermal energy. Ta<sub>2</sub>O<sub>5</sub> films were deposited at 200°C for 30 minutes and annealed at 600°C for 30 minutes have shown leakage current densities as low as 10° o A/ cm² for gate voltage under 5V. To the best of our knowledge, these are the best results reported to date by other researchers. The high energy photons used in the in-situ cleaning and deposition process play an important role in obtaining high quality films of Ta<sub>2</sub>O<sub>5</sub>.

### I. INTRODUCTION

For the development of next generation of Si ICs, there is a need for the development of high dielectric constant materials that can be used as the gate dielectric material as well as the dielectric of the DRAM capacitor. From the device performance and reliability point of view, the high dielectric materials used in future Si ICs must meet several requirements. Any new material must show low leakage current and high dielectric constant values. The process should provide materials with low microscopic defects, low thermal and residual stress. Additionally, low processing temperatures must be used in the deposition of the new dielectric materials. A number of high dielectric materials have been investigated throughout the world [1,2].  $Ta_2O_5$  films deposited by chemical vapor deposition (CVP) techniques are promising candidates (the bulk dielectric constant of  $Ta_2O_5$  is 25). However, because leakage current densities in  $Ta_2O_5$  are higher than those in conventional dielectrics such as silicon nitrides or silicon dioxides, it is difficult to use these materials for Si IC applications. In this paper, we report the results of  $Ta_2O_5$  films with low leakage currents deposited by dual spectral source rapid isothermal processing (DSSRIP) assisted metalorganic chemical vapor deposition (MOCVD) on Si and conducting