To be published, Proc. Symp. Mat. Res. Soc, Vol. 525, 1998.

# Polycrystalline Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> for Suppression of Boron Penetration in PMOS Structures

C.L. Chang and J.C. Sturm, Department of Electrical Engineering, Center for Photonics and Optoelectronic Materials, Princeton University, Princeton, NJ 08544. clchang@ee.princeton.edu

## **ABSTRACT**

We have fabricated polycrystalline  $Si_{1-x-y}Ge_xC_y$  by Rapid Thermal Chemical Vapor Deposition and used it as part of a polycrystalline gate structure for PMOS devices. The results showed that the use of carbon in polycrystalline  $Si_{1-x-y}Ge_xC_y$  suppressed boron penetration across the gate oxide. No effects of gate depletion with the use of poly- $Si_{1-x-y}Ge_xC_y$  were observed. Our work suggests that the addition of carbon reduced the chemical potential of boron in  $Si_{1-x-y}Ge_xC_y$ , which deterred boron from diffusing across the underlying gate oxide.

## INTRODUCTION

In a traditional complementary metal-oxide-semiconductor (CMOS) technology, heavily doped n-type (n<sup>+</sup>) polycrystalline silicon gates are used for both n- channel (NMOS) and p- channel (PMOS) devices. In order to achieve a high drive current and an optimal logic-gate performance, it is desirable that both n- and p- channel devices have small and opposite threshold voltages (V<sub>T</sub>) with comparable magnitudes. The n<sup>+</sup> polycrystalline silicon gate yields a reasonable threshold voltage for n-channel devices, but the threshold voltage of the p-channel devices has a much higher magnitude. As a result, boron is implanted into the device channel to adjust threshold voltage, forming a buried-channel PMOS device.

Even though buried-channel devices generally exhibit a higher carrier mobility than typical surface-channel devices by moving carriers away from  $SiO_2/Si$  interface, the advantage is outweighed by other short-channel effects, such as threshold voltage lowering, higher subthreshold currents and higher susceptibility to punchthrough<sup>1</sup>. Furthermore, buried channels are not suitable for low temperature operation due to a dopant freeze-out problem<sup>2</sup>. As a result, as devices are scaled down in size to below 0.35  $\mu$ m in gate length, "dual-gate" devices are desirable to create both PMOS and NMOS surface-channel devices with better short-channel characteristics.

In dual-gate CMOS devices, n<sup>+</sup> polycrystalline silicon is used as the gate for NMOS devices and p<sup>+</sup> polycrystalline silicon for PMOS devices. A single undoped polycrystalline silicon layer is deposited, which is then doped n<sup>+</sup> or p<sup>+</sup> by the source/drain implantation process of the n-channel and p-channel devices, respectively. For a p<sup>+</sup> polycrystalline silicon gated device, the gate is implanted with boron or boron difluoride (BF<sub>2</sub>) at the same time as are source and drain. Unfortunately, boron has been observed to penetrate across the thin gate oxide during post-implant anneal, resulting in a threshold voltage instability<sup>3</sup>. Moreover, even though gate oxides with the presence of fluorine have been shown to increase the resistance to hot-carrier effects, enhanced boron penetration has been reported due to the presence of fluorine in gate oxide<sup>4</sup>. Fluorine increases the boron diffusion constant in oxide<sup>5</sup> and it has been shown that the boron diffusivity increases approximately as the square root of the fluorine dose.

In this paper, we propose using polycrystalline  $Si_{1-x-y}Ge_xC_y$  as part of a polycrystalline gate to improve the problem of boron penetration. Our work was motivated by the recent interest in using substitutional carbon in single crystalline  $Si_{1-y}C_y$  or  $Si_{1-x-y}Ge_xC_y$  to dramatically suppress boron diffusion due to thermal annealing in nitrogen<sup>6</sup>, oxidation-

enhanced diffusion<sup>7</sup>, or transient-enhanced diffusion<sup>8</sup>. Polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub>-based gates have been studied due to the following advantages. First, it is possible to adjust the work function of polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub> by varying the amount of germanium incorporation to adjust the flatband voltage (or threshold voltage)9. Second, the sheet resistance of polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub> is lower than that of the polycrystalline silicon due to a larger grain size which reduces carrier scattering<sup>10</sup>. Here we report that by incorporating carbon into polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub>, the problem of boron penetration can be greatly minimized.

## **EXPERIMENTS**

Samples were fabricated by first thermally oxidizing n-type silicon wafers in dry oxygen at 900°C for ~ 15 minutes, resulting in 80-90 Å oxides. Polycrystalline gates were deposited on top of gate oxides by rapid thermal chemical vapor deposition (RTCVD). Polycrystalline silicon was deposited at 700°C using silane, and polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> layers were deposited at 625°C with silane, germane and methylsilane flow, all with H<sub>2</sub> as a carrier gas at 6 torr. Diborane was used for p-type doping if samples were in-situ doped. Ion-implantation was performed with 5x10<sup>15</sup>/cm<sup>2</sup> BF<sub>2</sub><sup>+</sup> doses at 60 keV, resulting in ~ 100nm deep implantation damage. BF<sub>2</sub><sup>+</sup> was used because it has been widely used in industry for gates as well as source/drain shallow implants of MOSFET devices. Fluorine-enhanced boron diffusion will also make the effect of boron penetration significant in this study even with a relatively thick oxide. Samples were annealed in nitrogen after implantation. To study boron penetration across the gate oxide, metal-oxide-semiconductor (MOS) capacitors were fabricated. The capacitor size was 320 μm x 180 μm.

## RESULTS

The first set of samples contain three different gate structures. The first sample A(1) is similar to a traditional MOS structure, with a ~ 400nm polycrystalline silicon on a 90Å gate oxide. In the second sample A(2), a ~ 20nm thick polycrystalline Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> was inserted between the gate oxide and polycrystalline silicon while keeping the total gate thickness unchanged. Crystalline Si<sub>1-x-v</sub>Ge<sub>x</sub>C<sub>v</sub> grown under identical conditions contains 20% germanium and 0.6% substitutional carbon. The third sample is similar to A(2) except polycrystalline Si<sub>1-x-v</sub>Ge<sub>x</sub>C<sub>v</sub> was replaced by polycrystalline Si<sub>1-x</sub>Ge<sub>x</sub> to single out the effect of substitutional carbon. All layers were initially undoped and subsequently doped by BF2+ implants.

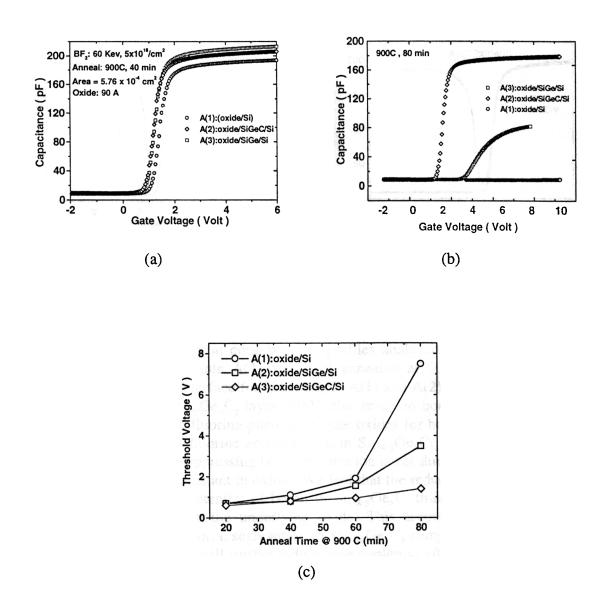

Figure 1 shows high-frequency (1 MHz) capacitance-voltage (C-V) curve of BF2+ implanted samples annealed at 900°C for 40 and 80 minutes. After a 40 minute anneal, there is no pronounced change in the threshold voltage and C-V curves behave normally. As the annealing time was increased to 80 minutes, however, C-V curves shifted by a few volts for samples A(1) and A(3), an indication of boron penetration. A much lower shift is observed in sample A(2), indicating that Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> suppresses the boron penetration. Figure 1(c) shows the threshold voltage as a function of annealing time. It is concluded that polycrystalline Si<sub>1</sub>. <sub>x</sub>Ge<sub>x</sub> slightly improves the problem of boron penetration while carbon in Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> greatly suppresses boron penetration.

Figure 1: (a) High-frequency C-V curves of implanted samples annealed at 900°C for 40 minutes. (b) C-V curves after 80 minutes of annealing. (c) Threshold voltage as a function of annealing time.

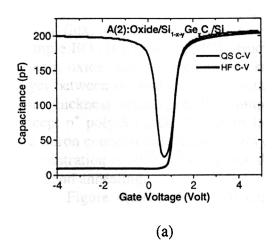

Although the  $Si_{1-x-y}Ge_xC_y$  layer suppressed boron penetration, it is crucial that boron still diffuse through the  $Si_{1-x-y}Ge_xC_y$  so that the entire gate is heavily doped. This is necessary to avoid gate depletion effects for negative gate bias (inversion) which would reduce the charge in the inversion layer (and the transistor drive current). Quasi-static C-V curve of sample A(2) annealed at 40 minutes, shows the same capacitance in inversion and accumulation, so that we conclude no gate depletion effect occurs with the  $Si_{1-x-y}Ge_xC_y$  layer. A smaller reverse-biased capacitance is observed in sample A(1), which could be the result of boron penetration and not gate depletion effects.

Figure 2: Quasi-Static Capacitance-Voltages curves of sample A(1) and A(2) annealed at 900°C, 40 minutes.

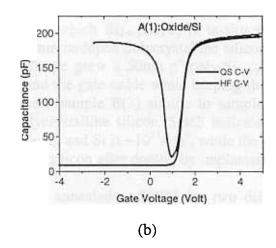

Figure 3 shows the boron concentration profiles analyzed by Secondary Ion Mass Spectroscopy (SIMS) for sample A(1) and A(2) annealed at 900°C, 80 minutes. Boron reached down to top oxide interface for both sample A(1) and A(2), an indication that boron indeed diffused through Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> layer. SIMS also revealed boron penetration in sample A(1). We also observed that fluorine piled up in gate oxides for both sample A(1) and A(2) and there is no evidence of fluorine accumulation in Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub>. Therefore, we concluded that the effect of carbon on suppressing boron penetration is not due to trapping of fluorine to reduce the boron diffusion constant in oxide. We feel that the reduction in boron penetration is due to a lower chemical potential of boron in Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> than in Si, which suppresses boron from diffusing through the underlying oxide. This argument is supported by the observation of a preferential boron segregation in Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> compared to Si, as in figure 3. A higher boron concentration will further reduce gate depletion effect, which shows another advantage of using polycrystalline Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> as part of a gate structure. Note that the apparent ability of boron to diffuse through poly-Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> as opposed to single crystalline Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> may be due to grain boundary diffusion in the polycrystalline film.

Figure 3: Boron profiles in sample A(1), A(2) by SIMS. Samples were  $BF_2^+$  implanted and annealed at 900°C for 80 minutes.

To test our argument and further eliminate the possibility that poly-Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> suppressed boron penetration through the underlying gate oxide by blocking the incoming boron flux, we designed another set of samples in which Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> is in-situ doped. Sample B(1) is a typical PMOS structure with ~300nm undoped polycrystalline silicon on a ~8nm oxide, used as a controlled sample. In B(2), we grew a 50nm p<sup>+</sup> poly-Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> layer between the undoped polycrystalline silicon and the gate oxide while keeping the total gate thickness unchanged. For comparison, we grew sample B(3) similar to sample B(2) except p<sup>+</sup> poly-Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> was replaced by p<sup>+</sup> polycrystalline silicon. SIMS indicated that the boron concentration in the in-situ doped Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> and Si is ~10<sup>21</sup>/cm<sup>3</sup>, while the boron concentration is  $10^{20}$ /cm<sup>3</sup> in the initially undoped polysilicon after doping by implantation of BF<sub>2</sub><sup>+</sup> and annealing.

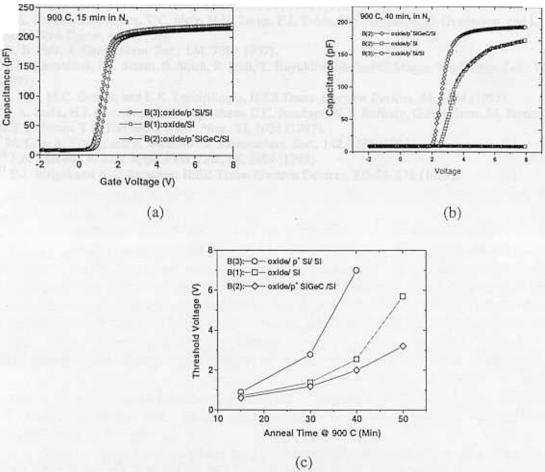

Figure 4(a)(b) show C-V curves of samples annealed at 900°C for two different annealing times. It is interesting that even with  $10^{21}$ /cm³ boron at the p⁺ Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> /oxide interface, sample B(2) has a smaller threshold voltage shift than that of sample B(1), which has only  $10^{20}$ /cm³ boron in the polycrystalline silicon after implantation and annealing. Also, for boron to penetrate across the gate oxide in sample B(1), it has to first travel through the polysilicon gate (via grain boundaries) and reach the top oxide interface. Both lower doping and a longer distance would seem to warrant less boron penetration in sample B(1), which is opposite from what was observed. This is further evidence that Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> suppresses boron penetration by lowering the chemical potential of boron in the gate.

Figure 4: (a) High-frequency C-V curves of implanted samples annealed at 900°C for 15 minutes. (b) C-V curves of 40 minutes anneal. (c) Threshold voltage as a function of annealing time.

### CONCLUSION

In summary, we have used polycrystalline  $Si_{1-x-y}Ge_xC_y$  as part of a polycrystalline gate structure to study the effect on boron penetration across gate oxide. The existence of carbon in polycrystalline  $Si_{1-x-y}Ge_xC_y$  suppressed boron penetration. We also found a preferred accumulation of boron in  $Si_{1-x-y}Ge_xC_y$  which is advantageous in reducing the gate depletion effect. Both observations suggest that carbon reduces the chemical potential of boron.

#### **ACKNOWLEDGEMENTS**

The authors like to acknowledge the support by ONR, DARPA, and the Sandia National Laboratory. C.L. Chang also acknowledges useful feedback from the silicon group of Bell Laboratory, Lucent Technologies, Murray Hill, NJ.

## **REFERENCES**

<sup>&</sup>lt;sup>1</sup> G.J. Hu and R.H. Bruce, *IEEE Trans. Electron Devices*, ED-32, 584 (1985).

<sup>&</sup>lt;sup>2</sup> J.Y.C. Sun, Y. Taur, R.H. Dennard, and S.P. Klepner, *IEEE Trans. Electron Devices*, ED-34, 19 (1987).

<sup>&</sup>lt;sup>3</sup> J.R. Pfiester, F.K. Baker, T.C. Mele, H.H. Tseng, P.J. Tobin, J.D. Hayden, J.W. Miller, C.D. Gunderson, and L.C. Parrillo, *IEEE Trans. Electron Devices*, **ED-37**, 1842 (1990).

L.C. Parrillo, *IEEE Trans. Electron Devices*, **ED-37**, 1842 (1990).

<sup>4</sup> F.K. Baker, J.R. Pfiester, T.C. Mele, H.H. Tseng, P.J. Tobin, J.D. Hayden, C.D. Gunderson, and L.C. Parrillo, *IEDM Tech Digest*, 443 (1989).

<sup>&</sup>lt;sup>5</sup> R. B. Fair, J. Electrochem. Soc., 144, 708 (1997).

<sup>&</sup>lt;sup>6</sup> L.D. Lanzerotti, J.C. Sturm, E. Stach, R. Hull, T. Buyuklimanli, and C. Magee, *Appl. Phys. Lett.*, **70**, 3125 (1997).

<sup>&</sup>lt;sup>7</sup> I. Ban, M.C. Ozturk, and E.K. Demirilioglu, *IEEE Trans. Electron Devices*, 44, 1544 (1997).

<sup>&</sup>lt;sup>8</sup> P.A. Stolk, H.J. Gossmann, D.J. Eaglesham, D.C. Jacobson, C.S. Rafferty, G.H. Gilmer, M. Jaraiz, J.M. Poate, H.S. Luftman, T.E. Haynes. J. Appl. Phys., 81, 6031 (1997).

<sup>&</sup>lt;sup>9</sup> M. Cao, A. Wang, and K. Saraswat, J. Electrochem. Soc., 142, 1566 (1995).

<sup>&</sup>lt;sup>10</sup> J.A. Tsai and R. Reif, Appl. Phys. Lett., 66, 1809 (1995).

<sup>&</sup>lt;sup>11</sup> P.J. Wright and K.C. Saraswat, IEEE Trans. Electron Devices, ED-36, 879 (1989).