## P-channel Thin Film Transistor of Microcrystalline Silicon Directly Deposited at 320°C

Y. Chen, K. Pangal, J.C. Sturm and S. Wagner

Department of Electrical Engineering, Princeton University, Princeton, NJ 08544

Phone 609-258-5902, Fax 609-258-1840, E-mail <a href="mailto:yuc@ee.princeton.edu">yuc@ee.princeton.edu</a>

We report the first p-channel thin-film transistor made in directly-deposited microcrystalline silicon ( $\mu$ c-Si). The channel silicon is made by plasma-enhanced vapor deposition (PECVD) in a process similar to the deposition of hydrogenated amorphous silicon (a-Si:H). The deposition temperature for the  $\mu$ c-Si is 320°C and the highest post-deposition TFT process temperature is 280°C. The p-channel TFT is made possible by the low-temperature deposition of  $\mu$ c-Si with near-intrinsic properties. Because making p-channel TFTs of a-Si:H has not been possible to date, the p-channel  $\mu$ c-Si TFT represents a breakthrough in low-temperature Si TFT technology.

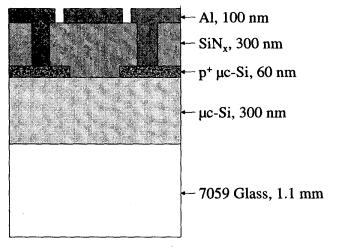

The TFTs were fabricated in the top-gate configuration on unpassivated Corning 7059 glass substrates. The  $\mu$ c-Si layer was deposited by plasma enhanced CVD using a mixture of SiH<sub>4</sub>, SiF<sub>4</sub> and H<sub>2</sub>. A four-level mask process with specially designed masks was used in the TFT fabrication. The schematic cross section of the TFT structure is shown in Figure 1. First the 300 nm thick  $\mu$ c-Si layer and a 60 nm p<sup>+</sup> $\mu$ c-Si layer were grown without breaking vacuum. Next we patterned (1) the intrinsic layer island and (2) the p<sup>+</sup> $\mu$ c-Si source and drain using reactive ion etching (RIE). After depositing 300nm thick SiN<sub>x</sub> by PECVD at 280°C as the gate insulator, we patterned the SiN<sub>x</sub> gate and opened contact holes to the p<sup>+</sup> source and drain using RIE. Then we thermally evaporated Al, and in a last step patterned the gate, source and drain electrodes using an Al wet-etchant. The fabricated TFTs were annealed in H<sub>2</sub> + N<sub>2</sub> at 200 °C for 1 hour.

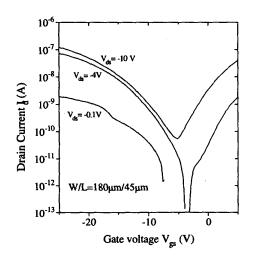

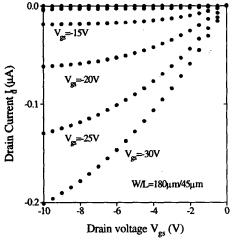

Figure 2 and Figure 3 show the transfer and output characteristics of the p-channel TFT. In Figure 2 the drain current  $I_d$  is plotted against gate voltage  $V_{gs}$  for drain voltage  $V_{ds}$  at -0.1 V, -4 V and -10 V. In Figure 3 the drain current is plotted against the drain voltage for gate voltage from 0 to -30 V. In Figure 2 for  $V_{ds}$  = -10 V the ON/OFF current ratio is 2.5 x  $10^3$  when  $V_{gs}$  varies from -5 V to -25 V and for  $V_{ds}$  = -4 V the ON/OFF current ratio is >  $10^5$ . The threshold voltage is -13 V, and the subthreshold slope S = 2.8 V/dec. The linear and saturated hole mobilities of the TFT are 0.026 and 0.041 cm<sup>2</sup>/Vs respectively. While these mobilities are low, they demonstrate p-channel operation. We are analyzing the TFT characteristics and experimenting with fabrication to improve TFT performance.

This work is supported by DARPA, EPRI and NJCST.

Figure 1. Schematic cross section of the p-channel TFT

Figure 2. TFT transfer characteristics

Figure 3. TFT output characteristics