## Large-Grain Polysilicon Films with Low Intragranular Defect Density by Low-Temperature Solid-Phase Crystallization

Xiang-Zheng Bo, Nan Yao<sup>†</sup>, and J. C. Sturm Center for Photonics and Opti-Electronic Materials, Department of Electrical Engineering, Princeton University, Princeton, New Jersey 08544, U.S.A. <sup>†</sup> Princeton Materials Institute, Princeton University, Princeton, New Jersey 08544, U.S.A.

### ABSTRACT

Solid phase crystallization (SPC) of *a*-Si: H at 600 °C was investigated by transmission electron microscopy (TEM) and Raman spectroscopy in a cantilever structure, where the underlying SiO<sub>2</sub> was removed prior to the crystallization. The absence of the underlying oxide leads to both a higher grain size and a lower intragranular defect density. The grain size increases from 0.6  $\mu$ m in regions with the underlying oxide to 3.0  $\mu$ m without the underlying oxide, and the intragranular defect density decreases one order of magnitude from ~ 10<sup>11</sup> cm<sup>-2</sup> to ~ 10<sup>10</sup> cm<sup>-2</sup>. The improvements in material quality without the lower *a*-Si/SiO<sub>2</sub> interface are thought to be due to a lower nucleation rate and a lower tensile stress with an easier silicon atomic rearrangement at the lower silicon interface.

### **INTRODUCTION**

Polysilicon thin film transistors (TFTs) are used in active-matrix-liquid-crystal displays (AMLCD) [1] and as upper-layer devices for three-dimensional VLSI [2]. For such active layers of TFTs, polycrystalline silicon crystallized from amorphous silicon by solid-phase crystallization (SPC) has attracted much interest. The electrical characteristics of polysilicon TFTs are strongly dependent on the polysilicon microstructure. The electron carrier mobility in polysilicon TFTs is typically < 100 cm<sup>2</sup>/Vs, which is much less than that in single-crystalline silicon MOSFETs. Grain boundaries and intragranular defects (microtwins and dislocations) are electrical potential barriers and scattering sites, which decrease the mobility. Polysilicon films with a larger grain size and lower intragranular defect density have been a continual goal [3-6].

To date, there are two methods to decrease the density of intragranular defects of polysilicon films crystallized from *a*-Si: high-temperature (>750 °C) annealing [7] and laser crystallization [8]. However, high-temperature processing cannot be used in AMLCD TFTs, which are fabricated on glass substrates with a strain point less than 650 °C. Compared with the furnace annealing, laser crystallization has the potential disadvantages of high-cost and poor film uniformity. This paper examines how removing the underlying oxide before crystallization step can increase grain size and reduce defect density within grains, while maintaining the process temperature  $\leq 600$  °C.

### **EXPERIMENT AND RESULTS**

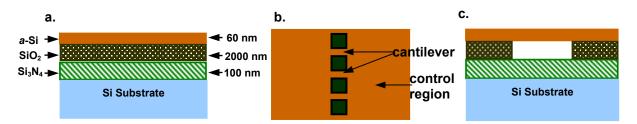

Figure 1 shows the fabrication process of the cantilever structure of suspended *a*-Si. After depositions of 100nm-thick Si<sub>3</sub>N<sub>4</sub> and 2 $\mu$ m-thick SiO<sub>2</sub> on a <100> silicon substrate, *a*-Si was

A16.4.1

**Figure 1.** Fabrication process: (a) layer structure; (b) top view of cantilever structure after optical lithography and dry etching; (c) underlying oxide etch through the holes between the cantilevers. The cantilever width and length are  $\sim 5 \,\mu\text{m}$  and  $\sim 20 \,\mu\text{m}$ , respectively.

deposited at 150 °C by plasma-enhanced chemical-vapor-deposition (PECVD). The amorphous silicon was then patterned into islands with cantilever structures [Fig. 1(b)], and subsequent oxide etching in diluted HF through the holes created the *a*-Si cantilevers [Fig. 1(c)]. Furnace annealing at 600 °C transformed the film into polycrystalline. SEM observations confirmed the cantilevers did not collapse onto the substrate before or after furnace anneal. The microstructure of the polysilicon films was investigated by TEM and Raman scattering spectra, with the cantilever region (without underlying oxide) compared with the control region (with underlying oxide) in the same sample. The grain size of polysilicon was defined by the formula of  $d = \sqrt{4A/\pi}$ , where *A* is the area of a grain. The intragranular defect density was defined as the reciprocal of the defect-free area within a polysilicon grain.

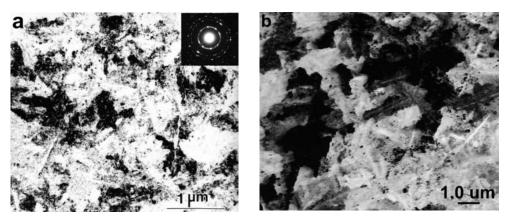

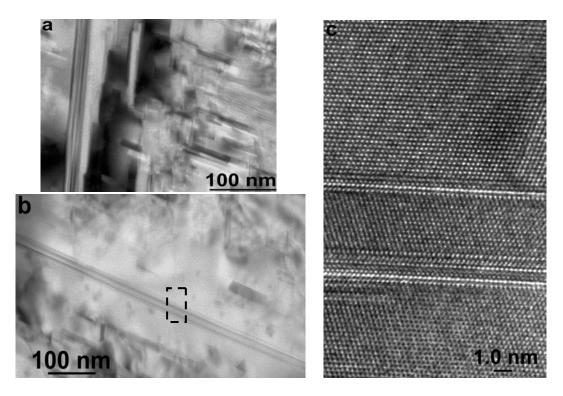

TEM observations in Fig. 2 show the grain size of fully-crystallized polysilicon in (a) the control area with underlying oxide and (b) the cantilever area without underlying oxide after annealing at 600 °C for 24 hr. The average grain size increases from ~ 0.6  $\mu$ m to ~ 3.0  $\mu$ m. Comparison of the intragranular defect density in the control area with the cantilever area was also made by high-magnification TEM observations. Both of the grains in Fig. 3(a) and (b) have <110> crystal orientation. Defects from diffraction contrast are clearly seen in the control area [Fig. 3(a)]. Though the film in the cantilever area [Fig. 3(b)] is not defect free, the average

**Figure 2.** TEM micrograph of fully crystallized polysilicon films in (a) the control region with underling SiO<sub>2</sub> (grain size ~ 0.6  $\mu$ m) and (b) the cantilever region without underlying SiO<sub>2</sub> (grain size ~ 3.0  $\mu$ m) after furnace anneal at 600 °C for 24 hr.

**Figure 3.** Microstructure of polysilicon grains oriented with <110> to show the defect density in (a) the control region and (b) the cantilever region. High-resolution TEM observation of (c) is from the marked area in (b) to show the perfect atomic arrangement on both sides of the microtwins.

defect-free area increases from ~ 25 nm [Fig. 3(a)] to ~ 100 nm in diameter, and the defect density is correspondingly reduced from ~  $10^{11}$  cm<sup>-2</sup> to ~  $10^{10}$  cm<sup>-2</sup>. The high-resolution TEM image [Fig. 3(c)] from the area marked by the dash line in Fig. 3(b) shows silicon atom periodic arrangements without any defect on both sides of the microtwins.

## DISCUSSION

#### **Nucleation Density and Grain Size**

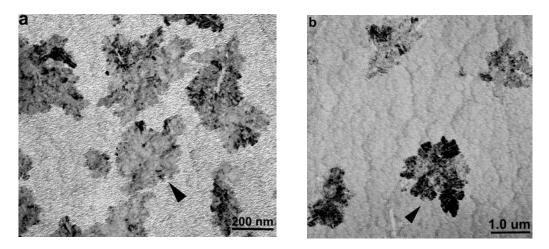

The SPC of *a*-Si involves two steps: nucleation and growth. The final grain size of polysilicon is related to the nucleation rate *N* and growth velocity  $v_g$ , expressed by the formula  $d \propto \begin{bmatrix} v_g \\ N \end{bmatrix}^{1/3}$ , where *d* is the grain size [9]. It has been found that the lower *a*-Si/SiO<sub>2</sub> interface is the preferred nucleation site of SPC [10]. High nucleation rate at the *a*-Si/SiO<sub>2</sub> interface in the control area of silicon films results in many grains and thus a small size. By removing the *a*-Si/SiO<sub>2</sub> interface in the cantilever region, the nucleation density decreases. This can be observed before full crystallization (Fig. 4), where films were annealed at 600 °C for 14 hr *vs.* 24 hr in

**Figure 4.** Plan-view TEM observation of polysilicion grain in (a) control region and (b) the cantilever region after annealing at 600 °C for 14 hr before complete crystallization, showing the grain density ( $\sim 10^8$  cm<sup>-2</sup> vs.  $\sim 10^7$  cm<sup>-2</sup>) and grain size ( $\sim 0.4 \text{ }\mu\text{m} \text{ }vs. \sim 1.0 \text{ }\mu\text{m}$ ).

Figure 2. The nucleation density in the cantilever area [Fig. 4(b)] is ~ 10 times lower than that in the control area [Fig. 4(a)] (~ $10^7$  cm<sup>-2</sup> vs. ~ $10^8$  cm<sup>-2</sup>). This lower nucleation rate in the free-standing films leads to larger grain size.

#### **Stress during Solid-Phase Crystallization**

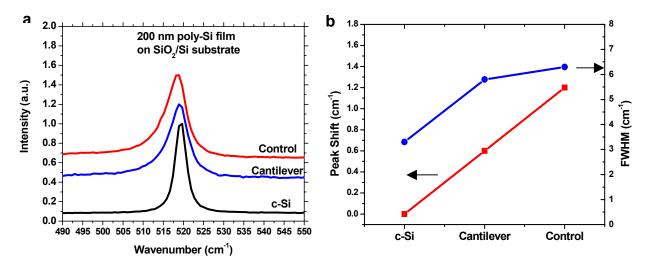

It should also be noted that the grain size in Fig. 4(b) is ~ 1.0 µm, larger than the grain (~ 0.4 µm) in Fig. 4(a). This means the crystalline grains in the cantilever area have a higher growth rate than in the control area. Grain growth is driven by the Gibbs free energy difference between *a*-Si phase and crystalline phase. It is known (and we will show) that the crystallization leads to stress in the crystallization films [5]. The high stress accumulated during SPC decreases the driving force for grain growth. The stress in the polysilicon films can be measured by Raman scattering, in which tensile stress leads to Raman peak shifting to a smaller wave number. Higher stress leads to a larger peak shift, calculated by the formula [11]  $\sigma$  (MPa) = -250  $\Delta \omega$  (cm<sup>-1</sup>), where  $\Delta \omega = \omega - \omega_0$  with  $\omega_0 = 519.5$  cm<sup>-1</sup>. Figure 5 (a) shows Raman spectra of 200nm-thick polysilicon films (annealed at 600 °C for 24 hr) in control region and cantilever regions, and a single crystalline silicon substrate, along with the Raman shifts and FWHMs in Fig. 5(b). Note that both of the polysilicon films are under tensile stress. The stress in the cantilever polysilicon films is half of the ~ 300 MPa in the control area. This may be the reason for the higher growth rate leading to larger grain size in the cantilever films [6].

The stress during SPC is due to inability of silicon atoms to freely rearrange near the a-Si/SiO<sub>2</sub> interface due to the bonding of *a*-Si atoms to the oxide, or due to volume contraction during *a*-Si to poly-Si phase transition [5]. The stress is largest at the *a*-Si/SiO<sub>2</sub> interface, where the nucleation preferably starts, as the silicon atoms in the *a*-Si are strongly bound to the surface atoms of the underlying SiO<sub>2</sub> layer after deposition. To relieve this tensile stress, crystalline defects (microtwins, dislocations, etc) develop during the nucleation and growth. When the

**Figure 5.** (a) Raman spectra of 200nm-thick fully crystallized polysilicon films in control and cantilever regions, and a (100)- orientated single-crystalline silicon substrate. (b) Raman peak shift and FWHM by fitting curve in (a).

underlying oxide is removed, silicon atoms can freely move themselves to form a crystalline lattice. As shown in Fig. 5(b), there is less stress in free-standing polysilicon films than in ascontrolled films with an underlying oxide, leading to a lower intragranular defect density in the cantilever samples. It is also well known that small crystallites and high defect densities in polysilicon films cause asymmetry and broadening of the Raman spectrum due to phonon scattering from the microcrystallite boundaries and intragranular defects [12]. The defect scattering destroys the lattice translational symmetry and relaxes the momentum conservation rule during phonon-photon interaction, so that smaller size of the defect-free crystallite increases the Raman FWHM [13]. In Fig. 5(b), the values of FWHM of Raman spectra in various regions are: cantilever polysilicon region, 5.8 cm<sup>-1</sup>; control polysilicon region, 6.3 cm<sup>-1</sup>; and single-crystalline silicon substrate, 3.3 cm<sup>-1</sup>. This narrower peak in the cantilever region suggests a lower density of intragranular defects compared with that in the control region in qualitative agreement with our TEM observations.

#### CONCLUSIONS

By removing the underlying oxide before annealing, the quality of polysilicon films crystallized from *a*-Si at 600 °C was greatly improved, with a 5× increase in the grain size and a  $10\times$  reduction in the intragranular defect density compared to a silicon film with underlying SiO<sub>2</sub>. We hypothesize that this improvement is because the removal of the *a*-Si/SiO<sub>2</sub> interface results in a lower grain nucleation rate and an easier release of stress accumulated at the interface during SPC.

## ACKNOWLEDGEMENTS

This work was supported by the ARO (DAA655-98-0270) and DARPA/ONR (N66001-00-1-8957). The authors are indebt to Prof. Wagner for the help of PECVD depositions.

# REFERENCES

- [1] T. Morita, S. Tsuchimoto, and N. Hashizume, Mater. Res. Soc. Symp. Proc. 345: 71 (1994).

- [2] S.D.S. Malhi, H. Shichijo, S.K. Banerjee, R. Sundaresan, M. Elahy, G.P. Pollack, W.F. Richardson, A.H. Shah, L.R. Hite, R.H. Womack, P.L.Chatterjee, and H.W. Lam, IEEE Trans. Electron Devices, 32: 258 (1985).

- [3] M.-K. Ryu, S.-M. Hwang, T.-H. Kim, K.-B. Kim, and S.-H. Min, Appl. Phys. Lett. 71: 3063 (1997).

- [4] F. Petinot, F. Plais, D. Mencaraglia, P. Legagneux, C. Reita, O. Huet, and D. Pribat, J. Non-Crystalline Solids, **227-230**: 1207 (1998).

- [5] Y. Morimoto, Y. Jinno, K. Hirai, H. Ogata, T. Yamada, and K. Yoneda, J. Electrochem. Soc. 144: 2495 (1997).

- [6] X.-Z. Bo, N. Yao, S. R. Shieh, T. S. Duffy, and J. C. Sturm, J. Appl. Phys. 91: 2910 (2002).

- [7] L. Haji, P. Joubert, J. Stoemenos, and N. A. Economou, J. Appl. Phys. 75: 3944 (1994).

- [8] T. Serikawa, IEEE Trans. ED 36: 1929 (1989).

- [9] R.B. Iverson and R. Reif, J. Appl. Phys. 62: 1675 (1987).

- [10] C. Spinella, and S. Lombardo, J. Appl. Phys. 84: 5383 (1998).

- [11] S. Boultadakis, S. Logothetidis, and S. Ves, J. Appl. Phys. 72: 3648 (1992).

- [12] J. Gonzalez-Hernandez, G. H. Azarbayejani, R. Tsu, and F. H. Pollak, Appl. Phys. Lett. 47: 1350 (1985).

- [13] I.H. Campbell, and P.M. Fauchet, Solid State. Commun. 58: 739 (1986).