Nanocrystalline Silicon Thin Film Transistors on Optically Clear Polymer Foil Substrates Alex Kattamis, I-Chun Cheng, Ke Long, James C. Sturm, Sigurd Wagner

## **Abstract**

We have fabricated TFTs of nanocrystalline silicon (nc-Si) at 150°C on clear polymer substrates (coefficients of thermal expansion,  $\alpha$ ~45 to 55ppm/K), on Kapton® 200E ( $\alpha$ =17ppm/K), and on Corning 1737 glass ( $\alpha$ =3ppm/K) for comparison. Because thermally stable polymers, such as Kapton® 200E polyimide, have glass transition temperatures as high as 325°C, they are candidates for direct substitution of display glass. The stresses developed in the substrate and device layers, due to  $\alpha$ , are reduced by decreasing the thickness of the active layers, by cutting the layers into islands separated by exposed substrate, and by designing stresses, via plasma conditions, into the SiN<sub>x</sub> passivating layers. By using these three techniques we have made nc-Si TFTs on high  $T_g$ , and high  $\alpha$ , clear polymer foils with electron mobilities of up to  $18\text{cm}^2/\text{Vs}$ . When integrated with bottom-emitting organic light emitting diodes, such devices will allow for a 10x reduction in pixel TFT areas, compared to TFTs of amorphous silicon.

### Introduction

Flexible displays are the next technology generation for flat-panel displays. Therefore interest is growing in building high-performance TFT backplanes on flexible substrates. Flexible polymer foils are attractive for large area displays, because they are lightweight and allow for the possibility of roll-able displays. Ideally, a flexible backplane will be made using fabrication processes that already have been developed for glass with only minor changes. Nanocrystalline silicon (nc-Si) TFTs are capable of both n- and p-type operation, have at least ten times the nchannel ON current of amorphous silicon (a-Si) TFTs, and can be plasma deposited at temperatures upwards of 150°C. This makes them CMOS capable and good candidates for pixel circuits in active-matrix organic light emitting diode (AMOLED) displays. There is growing interest in AMOLED displays because active-matrix addressing allows for high pixel count and long OLED life [1]. For AMOLED displays with TFT pixel drivers and bottom-emitting OLEDs mounted on the same plane, the substrate must be optically clear. When polymer substrates are heated that high though, the thermal expansion mismatch between silicon TFT materials and the polymer substrate becomes a challenge. The effects of mismatch become more pronounced as process temperature is increased and this mismatch, and built-in stresses in the device films, can combine to fracture TFT structures during processing.

Today pixel circuits for AMOLED displays on polymer substrates are conceived with hydrogenated amorphous-silicon thin film transistors (a-Si TFTs)  $^{[2,3]}$ . a-Si TFTs have been fabricated at temperature as low as ~100°C  $^{[4]}$  and have been produced on clear polymers such as poly-ethylene terephthalate (PET)  $^{[5]}$ . However since PET has a glass transition temperature ( $T_g$ ) <100°C, the maximum process temperature is limited and the TFTs exhibit low electron mobilities of up to  $0.12\text{cm}^2/\text{Vs}$   $^{[5]}$ . Hydrogenated nanocrystalline silicon (nc-Si) TFTs, on the other hand, can be fabricated at temperatures as low as 150°C, exhibit ten times the ON current as a-Si TFTs, and are build using similar techniques to those of a-Si on glass. nc-Si TFTs on glass exhibit hole and electron mobilities of  $0.35\text{cm}^2/\text{Vs}$  and  $40\text{cm}^2/\text{Vs}$  respectively  $^{[6]}$ . The p-

channel operation promises CMOS integration and all its advantages vis à vis power consumption and system-on-panel design <sup>[6]</sup>. In fact CMOS inverters of nc-Si with hole and electron mobilites of  $0.35 \text{cm}^2/\text{Vs}$  and  $30 \text{cm}^2/\text{Vs}$  respectively, have been fabricated on flexible, DuPont<sup>TM</sup> Kapton® 200E polymer foil <sup>[7]</sup>. Polymers such as Kapton® 200E have a  $T_g$  high enough for quality TFT deposition, but are absorbing in the blue and therefore cannot be used with bottom-emitting OLEDs. Also nc-Si TFTs are currently limited by the poor quality of the SiO<sub>2</sub> gate dielectric made at low temperatures. The SiO<sub>2</sub> is a strong motivation for processing at "glass temperatures." This temperature requirement rules out PET, for its  $T_g$ , and rules out Kapton ® 200E, for its color. Hence we are working with experimental clear polymers (CP), which have a  $T_g \sim 325$ °C. This group of polymers also has a large  $\alpha \sim 45-50 \times 10^{-6}/\text{K}$ .

The high  $\alpha$  of these CP substrates introduces a new challenge to TFT fabrication on flexible polymer substrates. When the  $\alpha$  of the substrate is much greater than that of the device films ( $\alpha_{\text{device films}}$ ~2-3ppm/K) a high thermal mismatch strain ( $\varepsilon_{TH}$ ) is introduced into the structure according to:

$$\varepsilon_{TH} \cong (\alpha_{substrate} - \alpha_{film}) \cdot (T_{room} - T_{depositiom})^{[8]}. \tag{1}$$

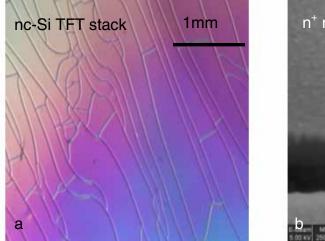

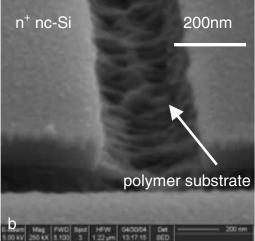

This formulation assumes that the structure is free of strain at growth and the strain develops as the sample is cooled from process temperature down to room temperature. For all our films a deposition temperature of 150°C is used to keep  $\varepsilon_{TH}$  low while allowing for reasonable TFT characteristics. As the sample cools the polymer substrate contracts more than the device thin films. This causes high compressive stresses (~1GPa) in the thin films and high tensile stresses in the polymer substrate. The nc-Si device films can only be strained to a critical value, beyond which the films and substrate crack, as shown in Figure 1. It is know that for a-Si thin films compressive failure occur at strains of 2% [9], whereas for nc-Si the number is unknown. By using various stress compensation techniques, we have fabricated n-channel nc-Si TFTs on the CP. Figure 2 displays a batch of these devices.

**Figure 1**. a) Optical image of a cracked TFT stack, on a clear polymer substrate with a large  $\alpha$ . b) The micrograph, of the same layers, shows that the cracks penetrate into the polymer substrate.

**Figure 2**. A batch of n-channel nc-Si TFTs on CP substrate over a 25cm<sup>2</sup> area.

# **Techniques for Stress Compensation and Reduction**

Since  $\alpha_{CP} >> \alpha_{film}$ , as the substrate cools from the deposition temperature down to room temperature the substrate contracts more than the films. This places a compressive strain on the films and a tensile strain on the substrate. The total strain in the thin films is: [8]

$$\varepsilon_{M} = \varepsilon_{0} + \varepsilon_{TH} + \varepsilon_{CH}, \tag{2}$$

where  $\varepsilon_0$  is the built-in strain,  $\varepsilon_{TH}$  is the strain due to  $\Delta\alpha$ , and  $\varepsilon_{CH}$  is the strain due to moisture absorption by the polymer substrate. Since  $\Delta\alpha$  is large for the CP, we observe that the thermal strain dominates. We employ three techniques to help reduce stress and build crack-free structures.

The first technique we use is to decrease the thickness of the device layers. The stress in the thin film is dependent on the temperature excursion during deposition ( $\Delta T$ ),  $\Delta \alpha$ , and thickness of the film <sup>[10]</sup>. For a *rigid* thin film on a *rigid* substrate, and in the absence of built-in stress, the total stress is: <sup>[10]</sup>

$$\sigma_f \propto (\alpha_{substrate} - \alpha_{film}) \cdot (T_{room} - T_{deposition}) \cdot \sqrt{d_{film}},$$

(3)

where  $d_{film}$  is the thin film thickness. The exact relation for compliant substrates like CP and Kapton ® 200E is yet unknown, but it is known that films under stress fracture more easily as their thicknesses are increased. Therefore, we minimize the device film thicknesses until the electrical performance of the TFT is affected.

By building the TFTs on  $SiN_x$  islands the compliant substrate is allowed to strain beneath and between the rigid  $SiN_x$  islands. Therefore the large average stress across the substrate is reduced <sup>[11]</sup>. This in turn reduces the probability of crack formation. The concept of island patterning to reduce the effects of the stress has been used on devices built on externally deformed substrates <sup>[11]</sup>.

The final method makes use of controlled stress in the  $SiN_x$  passivation layers. These layers serve to chemically isolate the substrate and act as adhesion promoters for the device layers. The  $SiN_x$  can be deposited with a range of built-in strains depending on the plasma power density [8]. The built-in strain is used to partially compensate the thermal strain, decreasing the

total stress according to equation 2. We use a low plasma power density to deposit a tensile  $SiN_x$  layer on the front-side of the substrate. This serves to compensate part of the compressive stress in the device films due to the  $\Delta\alpha$ , according to equation 1.

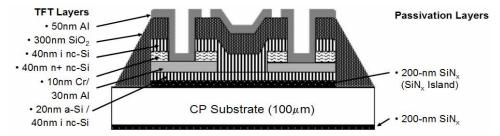

## nc-Si TFT Process

We made nc-Si TFTs at  $150^{\circ}$ C on a clear polymer ( $\alpha = 45$  to 55ppm/K), on Kapton® 200E ( $\alpha = 17$ ppm/K), and on Corning 1737 glass ( $\alpha = 3$ ppm/K) for comparison. The n-channel nc-Si TFTs were built in a staggered top gate, bottom source drain structure, Figure 3. No passivation layers or SiN<sub>x</sub> islands were used on the glass substrate.

**Figure 3**. Cross-section schematic of the  $n^+$  nc-Si TFT built onto a SiN<sub>x</sub> island.

200nm of SiN $_x$  is deposited by PECVD at 150°C on the backside and then on the front-side of the substrate. This is followed by an i nc-Si seed layer. The seed layer is used to introduce nucleation sites and produce good crystallinity in very thin channel layers <sup>[7]</sup>. It is deposited by VHF-PECVD from  $H_2$  and SiH $_4$ . Dichlorosilane (DCS) is included to compensate native oxygen donors and lower the conductivity and thereby the TFT OFF current <sup>[12]</sup>. The source / drain metal is deposited by thermal evaporation, 30nm of Al and 10nm of Cr on the CP substrate. 50nm Cr is substituted on the Kapton® 200E and glass substrates. Etching down to the substrate defines the SiN $_x$  islands. Next the  $n^+$  nc-Si, source / drain contact layer is deposited by VHF-PECVD using PH $_3$  dopant gas. Patterning the source / drain exposes the seed layer upon which the channel layer will be deposited. The i nc-Si channel layer is deposited by VHF-PECVD from  $H_2$ , SiH $_4$ , and DCS. This is immediately followed by a 150°C SiO $_2$  deposited by PECVD from a He diluted N $_2$ O and SiH $_4$  source <sup>[13]</sup>. Next source / drain contact holes are patterned and 50nm Al is thermally evaporated on the CP sample, whereas 200nm Al is used on the Kapton® 200E and glass samples. Finally the top Al is patterned to define the gate and the devices are complete. Table 1 displays the layer thicknesses used on the three different substrates.

| Table 1. Thicknesses in nm of the nc-Si 1F1 | layers on the three types of substrate. |

|---------------------------------------------|-----------------------------------------|

|---------------------------------------------|-----------------------------------------|

| TFT Layers      | Material                   | Corning 1737 Glass | Kapton® 200E | CP  |

|-----------------|----------------------------|--------------------|--------------|-----|

| Passivation     | backside SiN <sub>x</sub>  | -                  | 200          | 200 |

| Passivation     | frontside SiN <sub>x</sub> | -                  | 200          | 200 |

| Seed            | i nc-Si                    | 60                 | 60           | 50  |

| S/D contact     | Al                         | -                  | -            | 30  |

| S/D contact     | Cr                         | 50                 | 50           | 10  |

| S/D doped       | n <sup>+</sup> nc-Si       | 50                 | 50           | 40  |

| Channel         | i nc-Si                    | 50                 | 50           | 40  |

| Gate dielectric | $SiO_2$                    | 300                | 300          | 300 |

| Gate metal      | Al                         | 200                | 200          | 50  |

## **Results**

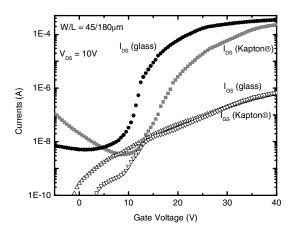

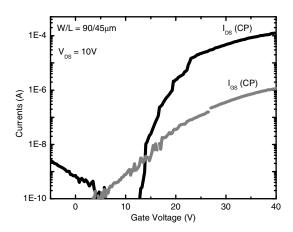

The transfer characteristics of the nc-Si TFTs are evaluated using a HP4155A parameter analyzer. The devices measured have the following dimensions W=90 $\mu$ m (CP), W=180 $\mu$ m (Kapton® 200E and glass) and L=45 $\mu$ m. An SiO<sub>2</sub> dielectric constant of 3.7 was measured by C-V at 1MHz on Al/SiO<sub>2</sub>/n-type Si wafer. Figure 4 displays the drain current (I<sub>DS</sub>) versus the gate-source voltage (V<sub>GS</sub>) for a drain-source voltage (V<sub>DS</sub>) of 10V, for a nc-Si TFT on glass and on Kapton® 200E. The transfer characteristics for the n-channel nc-Si TFT on the CP were measured in a similar manner, and are displayed in Figure 4.

**Figure 4.** Transfer characteristics for n-channel nc-Si TFTs on glass and Kapton® 200E (left). Transfer characteristics for n-channel nc-Si TFTs on CP (right).

**Table 2.** Results for n-channel nc-Si TFTs fabricated on glass, Kapton® 200E, and CP.

| Substrate          | α (ppm/K) | I <sub>ON</sub> /I <sub>OFF</sub> | $\mu_{\text{h-sat}}$ (cm <sup>2</sup> /Vs) | $\mu_{e-sat}$ (cm <sup>2</sup> /Vs) |

|--------------------|-----------|-----------------------------------|--------------------------------------------|-------------------------------------|

| Corning 1737 Glass | 2.5       | $10^{5}$                          | 0.35                                       | 40                                  |

| Kapton ® 200E      | 17        | $10^{5}$                          | 0.35                                       | 30                                  |

| CP                 | 45-55     | $10^{5}$                          | -                                          | 18                                  |

Table 2 shows the results for the devices on the 3 types of substrate. All the TFTs have an  $I_{ON}/I_{OFF} \sim 10^5$ . The nc-Si TFT on the glass has slightly lower  $V_T$  and a higher  $\mu_e$  than that of the nc-Si TFT on Kapton® 200E. This is probably due to fluctuations in chamber conditions rather than a fundamental difference in the devices from a substrate effect. The TFT on the CP exhibits characteristics similar those on the glass and Kapton® 200E. It has a  $V_T\sim 12V$  and  $\mu_e\sim 18\text{cm}^2/V_S$ . The lower mobility may be due to the fact that thin device films were used on CP, see Table 1. The thin S/D metal may cause an increase in the contact resistance. The gate leakage, though still large, has been reduced from previous results by use of He dilution during deposition, but further improvements are necessary [13]. A higher quality SiO<sub>2</sub> gate dielectric and improvements in the SiO<sub>2</sub> / i nc-Si interface must be made to reduce gate leakage current,  $V_T$ , and  $V_T$  drift.

#### **Conclusions**

We have produced nc-Si TFTs on a clear polymer substrate after adjusting the process to deal with the large  $\alpha$  of the substrate. By building the devices on SiN<sub>x</sub> islands and by carefully controlling the plasma conditions we have been able to reduce the effects of stress and prevent cracking. The TFTs on clear polymer perform similarly to those on the glass and Kapton® 200E. Such TFTs may become useful in AMOLED displays where both TFTs and bottom-emitting OLEDs are fabricated on the same plane and where high fill factors and drive currents are necessary.

# Acknowledgments

We would like to thank The DuPont Company and The New Jersey Commission on Science and Technology for research support, along with the Princeton Plasma Physics Laboratory (PPPL) for a PPST Fellowship.

#### References

- 1. M. Hack, J.J. Brown, J.K. Mahon, R. Kwong, R. Hewitt. *J. Soc. for Info. Disp. (SID)*, **18.2**, pp.191-195 (2000).

- 2. J-C. Goh, H-J. Chung, J. Jang. IEEE Elec. Dev. Lett., 23 9, pp. 544-546 (2002).

- 3. K. Sakariya, P. Servati, A. Nathan. *IEEE Trans. on Elect. Dev.*, **51** 12, pp. 2019-2025 (2004).

- 4. A. Sazonov, A. Nathan. J. Vac. Sci. Technol., A, 18, pp. 780-782 (2000).

- 5. C.-S. Yang, L. L. Smith, C. B. Arthur, and G. N. Parsons. *J. Vac. Sci. Technol. B.*, **18**, pp. 83 689 (2000).

- 6. I-C. Cheng, S. Wagner. *Thin Solid Films*, **427**, pp. 56–59 (2003).

- 7. I-C. Cheng, S. Wagner. *Mat. Res. Soc. Symp. Proc.*, **808**, pp. A4.6.1- A4.6.6 (2004).

- 8. I.-C. Cheng, A. Kattamis, K. Long, J. C. Sturm, S. Wagner. J. Soc. Info. Disp., submitted.

- 9. S. Wagner, H. Gleskova, I.-C. Cheng, J. C. Sturm, Z. Suo, <u>Flexible Flat Panel Displays</u>, G. P. Crawford, Ed. *Wiley* (2005), in press.

- 10. Z. Suo, Encyclopedia of Materials: Science and Technology, Elsevier, pp. 3290-3296 (2001).

- 11. P. I. Hsu, M. Huang, Z. Xi, S. Wagner, Z. Suo, J. C. Sturm. *J. App. Phys.*, **95**, pp. 705-712 (2004).

- 12. R. Platz, S. Wagner. *App. Phys. Lett.*, **73**, pp. 1236-1238 (1998).

- 13. A. Kattamis, I-C. Cheng, S. Allen, S. Wagner. *Mat. Res. Soc. Symp. Proc.*, **814**, pp. I10.14.1-I10.14.6 (2004).

Kapton® is a registered trademark of The DuPont Company.