J.C. STURM and J.F. GIBBONS

Stanford Electronics Labs, Stanford University, Stanford, CA 94305

# ABSTRACT

The minority carrier properties of shaped-beam laser-recrystallized polysilicon films have been studied, leading to the successful fabrication of vertical bipolar transistors in these films and to the demonstration of a novel three-dimensional merged vertical bipolar-MOS device. Experiments with lateral transistors established a minority carrier diffusion length of 4 µm in p-type recrystallized films. Vertical bipolar npn transistors with a base-width of 0.2 µm were fabricated in 0.75-µm-thick films using a polysilicon emitter technology. The strong dependence of the gain of the transistors on hydrogen annealing steps is described. With an Ar:H plasma anneal base-emitter space-charge region recombination, a common-emitter current gain of 100 was possible.

The bipolar transistor technology was then used to develop a 3-D four-terminal merged vertical bipolar-MOS device in a recrystallized film. It consists of the three terminals of a bipolar transistor plus a fourth under-lying terminal which serves to switch the collector current on or off. A simple model for the device is presented.

## INTRODUCTION

Laser-recrystallized polysilicon films have long been of interest for silicon-on-insulator and three-dimensional integration applications [1]. Because of the lateral nature of the MOSFET structure, nearly all device applications of recrystallized films have involved MOSFET's. However, there are many potential uses for minority carrier devices in recrystallized films. Bipolar transistors can source more current and sense lower currents than their majority carrier counterparts. To this end, several merged CMOS-bipolar processes have been developed [2,3]. Bipolar devices are also useful for the conversion of light into electrical signals.

To date, there has been only scattered work with minority carrier properties and devices in laser-recrystallized silicon [4,5,6]. In this paper, the minority carrier properties of silicon are investigated, leading to the successful fabrication of high-gain vertical bipolar transistors in recrystal-lized films. Finally, the bipolar technology is used to demonstrate a merged MOS-bipolar device.

# MINORITY CARRIER PROPERTIES

P-n junction diodes are the simplest minority carrier devices. Both lateral and vertical n<sup>+</sup>-p diodes were fabricated in laser-recrystallized films to qualitatively evaluate the material quality. The films were recrystallized from deposited polysilicon on thermally oxidized silicon substrates. The film thickness was ~0.75  $\mu$ m and a scanning argon ion laser was used for the recrystallization. The laser beam was elliptically shaped to a spot of roughly 200  $\mu$ m x 15  $\mu$ m. No seeding technique was used, and the typical resulting grain size was 200  $\mu$ m x 50  $\mu$ m with a subgrain boundary spacing within each grain of a few microns. An oxide cap, rather

Author's name O. L. Survey po

than a nitride cap, was used during the recrystallization to avoid interface states on the bottom of the recrystallized film [7]. Such interface states can act as recombination centers and affect the performance of minority carrier devices.

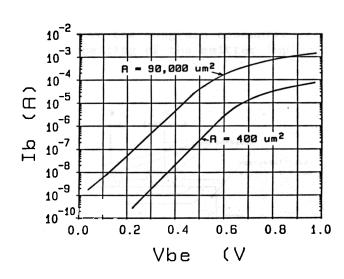

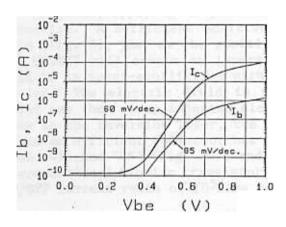

Both the lateral and vertical diodes appeared well-behaved when measured on a curve-tracer, but low current measurements in forward bias showed a non-ideal current-voltage slope of ~100 mV/decade (diode quality factor n = 1.7). (See fig. 1.) The current in vertical diodes scaled as the junction area, ruling out parasitic surface effects. In an ideal diode the dominant current in forward bias results from the recombination of carriers in neutral regions, leading to a current-voltage slope of 60 mV/decade of current (n = 1.0). The non-ideal slope of the diodes in the recrystallized films indicates excessive recombination in the space-charge region, characteristic of material with a low minority carrier lifetime. A seeding technique was then used to eliminate grain boundaries (but not the subgrain boundaries). No improvement in the diode performance was seen. Thus, it appears that grain boundaries were not the dominant recombination centers in the unseeded material, leaving subgrain boundaries or some unknown defects as the main recombination centers.

Fig. 1. Current-voltage characteristics for vertical diodes.

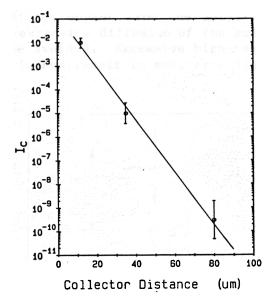

Fig. 2. Dependence of collector current on the emitter-collector spacing in lateral transistors.

Lateral bipolar npn transistors were then fabricated in unseeded films and annealed in forming gas to quantifiably measure the electron minority carrier diffusion length. According to simple theory, the collector current should decrease exponentially with the emitter-collector spacing. From the observed data (fig. 2), a minority carrier diffusion length of 3.9  $\mu m$  was found. Surprisingly, this diffusion length is not much lower than the observed diffusion lengths of 5-10  $\mu m$  in strip-heater recrystallized films [8, 9], even though the subgrain boundary spacing in strip-heater recrystallized films is typically 10-100  $\mu m$  [10], over an order of magnitude larger than the subgrain boundary spacing in our laser-recrystallized films. This hints that there is some unknown defect in addition to the subgrain boundaries responsible for the carrier recombination in recrystallized polysilicon.

If one assumes a minority carrier diffusion coefficient of  $20~\rm cm^2/s$  for the minority carrier electrons, the diffusion length of 4 µm translates to a recombination lifetime  $\tau_r$  of 7.5 ns. This is not a very long lifetime,

6 /

S

Sturm page

Author's name\_\_\

but a diffusion length of 4  $\mu m$  should be adequate for high-performance narrow-base transistors. According to elementary bipolar transistor theory, for a base width of 0.2  $\mu m$  and a diffusion length of 4  $\mu m$ , transport of electrons across the neutal base region would limit the current gain of the transistor to "only" 750.

#### VERTICAL BIPOLAR TRANSISTORS

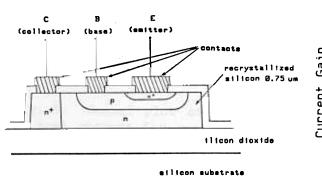

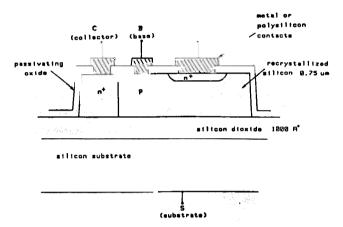

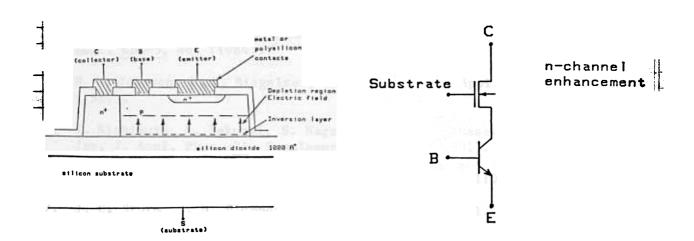

To see if high-performance bipolar transistors were indeed possible, vertical bipolar npn transistors were fabricated directly in recrystallized films 0.75 µm thick. 0.75 µm is very thin for a typical bipolar structure, but it was desired to keep the film thin to remain compatible with thicknesses\_ desirable for CMOS processing. The recrystallization was performed indentically to that described earlier. The emitter size of the transistors was 20 μm x 20 μm, large enough so that all emitters contained several subgrain boundaries, but small enough so that few devices contained grain boundaries. A cross section of the transistor structure is shown in fig. 3 [11]. The base width of the transistors was 0.2 µm. Because a very shallow emitter was required to make a vertical transistor in the thin film, a polysilicon emitter technology was used to maintain a high emitter efficiency. By carefully controlling the diffusion of the emitter dopant from the polysilicon emitter layer into the recrystallized film, excessive diffusion of the emitter\_ dopant down the subgrain boundaries could be avoided. Excessive high-temperature annealing of the emitter implant did indeed result in emitter-collector shorts.

Fig. 3. Cross section of the vertical bipolar transistor structure.

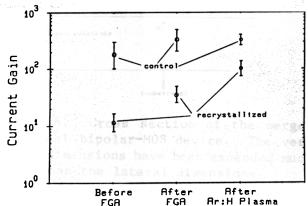

Fig. 4. Dependence of current gain on hydrogen annealing.

The current gain of the transistors, as measured on a curve tracer,—increased with hydrogen annealing after the fabrication. The current gain—measured about 10 without annealing, increased to near 40 after a 450 °C—forming gas anneal, and increased still further to about 100 after an Ar:H—plasma anneal at 350 °C. The results are depicted graphically in fig 4.—By driving off hydrogen from annealed transistors (450 °C, N<sub>2</sub> ambient), it—was possible to reduce the gain of the anneal transistors back to ~10 and—then repeat the process. The gain of control transistors fabricated in—single crystal substrates was rather independent of the hydrogen annealing.—

An explanation for the effect of the hydrogen annealing can be found by considering the physics of bipolar transistors and examining the low current measurements of the collector and base currents as a function of the base-emitter bias (Gummel plots). Before annealing, the collector current showed an inverse slope of 60 mV/decade (as it must in a true bipolar transistor), but the base characteristics were rather poor (~100 mV/decade). The poor base-

Author's name Q L Aurun page

characteristics were similar to the characteristics of the  $n^+$ -p diodes seen earlier. The current gain in the unannealed transistors increased with the current level to  $\sim \! 10$  at the current levels seen on the curve tracer. The non-ideal slope of the base current means that recombination in the base-emitter space-charge region was the primary source of base current and the limit to the current gain.

The hydrogen annealing in the SOI transistors was seen to reduce the base current but to leave the collector current unchanged, leading directly to an increase in the current gain of the device (fig. 5). The improvement (reduction) in the base current is presumably due to the hydrogen passivation of defects in the base-emitter space-charge region and the corresponding decrease in recombination. Even after the plasma annealing, however, the improved base characteristics were still not ideal (~85 mV/decade), implying that base emitter space-charge region recombination was still the limit to the transistor gain. While such non-ideal characteristics may rule out low current or analog applications, the high current gain of 100 is ample for digital or current driver applications.

Fig. 5. Gummel plot of collector and base current for a plasma-annealed transistor.

# MERGED 3-D VERTICAL BIPOLAR-MOS DEVICE

The new device was created by fabricating the bipolar structure of fig. 3 in a p-type film rather than in an n-type film. The device as fabricated has no collector underneath the emitter to collect electrons injected into the base by the emitter (fig. 6). Because the lateral transistor is very inefficient, operating the device with zero substrate bias results in essentially zero collector current, independent of the base current; electrons injected into the base from the emitter will recombine before reaching the collector contact on the side (fig. 7a).

Author's name  $\mathcal{G}$

Stern

\_page\_\_\_\_\_

Ö

Author's name

7a

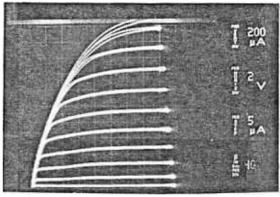

Fig. 7. Bipolar curve-tracer characteristics of the merged device for a substrate-emitter voltage of 0 V (a) and for 20 V (b).

However, applying a positive bias to the substrate will change the—

situation. A sufficient positive bias will invert the bottom of the p-type—

film (fig. 8), just as the positive bias on the gate of a conventional n-chan—

nel MOSFET will create an inversion layer of electrons. The inversion layer—

will be in quasi-equilibrium with the n+ collector contact on the side of the—

device. The electric field in the space-charge region above the inversion—

layer can then sweep injected electrons from the base to the inversion layer.—

Once in the inversion layer, the electrons can flow to the collector contact.—

Since an efficient collector has now been created, the bipolar transistor has—

been switched "ON" (fig. 7b), and the E, B, and C terminals now function as in—

a conventional bipolar transistor. With a 5-V swing on the fourth terminal, an—

ON/OFF current ratio of 105 has been observed.

Fig. 8. Collector layer formation with positive substrate bias.

Fig. 9. First order model for the merged bipolar-MOS device.

The collector of the conventional vertical bipolar transistors was described earlier as a depletion mode n-channel MOSFET gated by the substrate. In this merged bipolar-MOS device, the depletion mode MOSFET-collector has been replaced with an enhancement mode MOSFET; i.e. the substrate bias must be above some positive threshold voltage to turn the device "ON". As a first order model for the device, one may consider an npn bipolar transistor in series with an enhancement mode MOSFET (fig 9). At low substrate voltages, the

collector current is limited by the MOS transistor (fig. 7a), whereas at larger gate voltages the collector current is limited by the base current (fig. 7b).

MRS NIATERIAL RESEARCE SOCIETY

Author's name.

Chierr

L

## SUMMARY

Minority carrier devices in laser-recrystallized films are indeed limited by recombination at defects in the films. Whether these limiting defects are subgrain boundaries or other defects is not known. However, with proper hydrogen passivation, the effect of these defects can be reduced to the point such that high-gain vertical bipolar transistors are possible. The operation of the merged vertical bipolar-MOS device demonstrates that the influence of underlying layers on vertical devices in thin films can be very important.

The ability to fabricate useful minority carrier devices, such as optical detectors, for example, in a material suitable for three-dimensional integration should make exciting new device structures and circuit concepts possible.

\* ted | 1 33

#### ACKNOWLEDGEMENTS

The authors wish to thank R. A. Reynolds for his continued interest and appreciate the support of DARPA (contract no. N00014-84-K-0077). The authors also appreciate helpful discussions with the members of the Swanson and Gibbons groups.

## REFERENCES

- See, for example, D. A. Antoniadis, Energy Beam-Solid Interactions and Transient Thermal Processing, J.C.C. Fan and N. M. Johnson, eds. (North-Holland, New York, 1984) p. 587, and other papers in part VII.

- O. Minato, T. Masuhara, T. Sasaki, Y. Sakai, and T. Hayashida, Tech. Dig. of the 1982 Int. Elec. Dev. Mtg., San Francisco, 1982, p. 256.

- 3. B-Y. Tsaur, R. W. Mountain, C. K. Chen, and J.C.C. Fan, IEEE Electron Dev. Lett. EDL-5, 461 (1984).

- 4. N. M. Johnson, D. K. Biegelsen, and M. D. Moyer, Appl. Phys. Lett. 38, 900 (1981).

- 5. T. Nishimura, H. Sakurai, S. Nagao, T. Isu, Y. Akasaka, and N. Tsubouchi, Jap. J. Appl. Phys. 21, Supplement 21-1, 169 (1981).

- 6. N. M. Johnon and A. Chiang, Appl. Phys. Lett. 45, 1102 (1984).

- 7. J. C. Sturm, J. D. Plummer, and J. F. Gibbons, Appl. Phys. Lett. 46, 1171 (1985).

- 8. M. Rodder and D. A. Antoniadis, IEEE Electron Dev. Lett. EDL-4, 193 (1983)

- 9. B-Y. Tsaur, D. J. Silversmith, J.C.C. Fan, and R. W. Mountain, IEEE Electron Dev. Lett. EDL-4, 269 (1983).

- 10. M. W. Geis, H. I. Smith, B-Y. Tsaur, J.C.C. Fan, E. W. Maby, and D. A. Antoniadis, Appl. Phys. Lett. 40, 158 (1982).

- 11. J. C. Sturm and J. F. Gibbons, IEEE Electron Dev. Lett. EDL-6, 400 (1985)