## Semi-Insulating Oxygen-Doped Crystalline Silicon by Low Temperature CVD

J.C. Sturm, P.V. Schwartz\*, and Z. Lilienthal-Weber\*\*

Dept. of Electrical Engineering

Princeton University, N.J. 08544, USA

\*\*Center for Advanced Material Lawrence Berkeley Laboratory 62/203 Berkeley, CA 94720 ,USA

\*present address: Dept. of Elec. and Comp. Eng'g, Univ. of Iowa, Iowa, 52242, USA

The convential means of the production of SOI wafers, such as SIMOX, wafer-bonding, SOS, beam recrystallization, etc, all suffer from the problems of cost and large diameter wafers. In this work, initial experiments towards the direct production of SOI structures by a complete silicon-based epitaxial process are described. The work is based on the growth of crystalline semi-insulating layers of oxygen-doped silicon by low-temperature CVD. Through high levels of oxygen layers of silicon which are crystalline but with resistivities approaching  $10^6 \ \Omega$ -cm at room temperature have been achieved, and single cystalline silicon layers (without oxygen doping) with bulk mobility have been grown on top of these films.

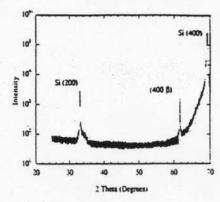

If high levels of oxygen are present during silicon epitaxy at convential (>900 °C) growth temperatures, it is well known that extended crystalline defects (giving rise to a hazy surface) or even polysilicon layers will result. Such polysilicon layers can result before the oxygen level in the samples reaches 10<sup>19</sup> cm<sup>-3</sup>. At growth temperatures under 800 °C, however, high oxygen levels may be achieved without destroying the crystallinity of the layers. For example, in the range of 700 to 750 °C, oxygen levels as high as 10<sup>20</sup> cm<sup>-3</sup> have been achieved in layers which exhibit nearly ideal X-ray diffraction patterns and electron-channeling patterns, and at 625 °C these oxygen levels have been achieved without any visible extended defects by TEM. Layers have been grown with both silane and dichlorosilane sources, although at low temperature high oxygen levels drastically reduce the growth rate with dichlorosilane.

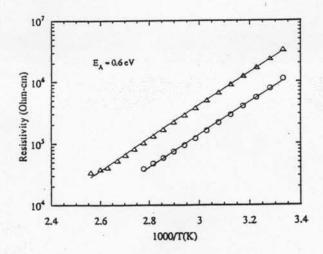

Layers grown at 700-750 °C were characterized electrically by the vertical transport of electrons and holes through the films by the growth of thick layers (several microns) followed by a top metal contact. The layers exhibited the classical shape of space charge limited current in a insulator with traps. From the low current portion of the curve where ohmic characteristics were observed, room temperature resistivities in the range of  $10^5$  to  $10^6$   $\Omega$ -cm were observed. The temperature dependence of the conductivity in the linear range indicated that the Fermi level was pinned near midgap, explaining the high resistivities. The exact physical microstructure created by the oxygen which gives rise to the Fermi-level pinning is not known, however.

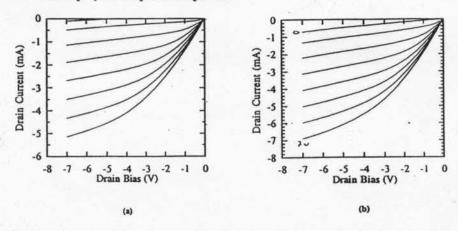

Because these layers are crystalline, single-cyrstalline silicon layers without oxygen doping may be grown on top of the semi-insulating layers. Both n and p-channel MOSFET's fabricated in these overlying layers have channel mobilities similar to those of FET's simultaneoulsy fabricated in bulk control samples.

- 1. P.V. Schwartz, C.W. Liu, and J.C. Sturm, Appl. Phys. Lett. 62, 1102 (1993).

- 2. Z. Lilienthal Weber, et al, J. Vac. Sci. Tech. to be publ., (1994).

- 3. M.A. Lampert and P. Mark, Current Injection in Solids (Academic Press, NY 1970).

Fig 1. Resistivity of Si:O layers vs. inverse temperature through vertical tranport measurements of forward biased Schottky diodes.

Fig. 2. X-ray diffraction of a Si:O layer with an O level of 5 x  $10^{19}$  cm<sup>-3</sup> grown on a (100) Si substrate. Note no polysilicon peaks are present.

Fig. 3. P-channel MOS I-V curves of FET's fabricated in (a) undoped Si on top of 1.5  $\mu m$  of Si:O and (b.) control bulk substrates.