# ADVANCED SILICON-BASED MATERIALS AND DEVICES USING CHEMICAL VAPOR DEPOSITION

**XIANG-ZHENG BO**

A DISSERTATION PRESENTED TO THE FACULTY OF PRINCETON UNIVERSITY IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE BY THE DEPARTMENT OF ELECTRICAL ENGINEERING

November 2004

© Copyright by Xiang-Zheng Bo, 2004.

All rights reserved.

The fear of the LORD is the beginning of knowledge.

Proverb 1:7

### ABSTRACT

Novel silicon-based materials (*a*-Si, poly-Si, SiGe) based on chemical vapor deposition have been used to fabricate poly-Si thin film transistors (TFTs), and Si three-dimensional photonic bandgap crystals, and SiGe single-hole transistors.

Polysilicon films created by solid-phase crystallization of *a*-Si are of great interest. The low transport mobility of poly-Si TFTs relative to single-crystalline Si MOSFETs is due to scattering from grain boundaries and intragranular defects in poly-Si films. To remove grain boundaries, we used a hydrogen plasma treatment of an *a*-Si film through an opening hole ( $\leq 0.6 \mu$ m in diameter). Subsequent anneals at 600 °C lead to a single-grain silicon film in the hole. By removing the underlying SiO<sub>2</sub> of *a*-Si film, the intra-grain defect density in poly-Si was reduced by one-order of magnitude from ~10<sup>11</sup> cm<sup>-2</sup> to ~10<sup>10</sup> cm<sup>-2</sup>. These improvements are thought to be able to improve the electrical performance of poly-Si TFTs.

Photonic crystals prohibit light propagation in a specific wavelength range. 3-D periodic face-centered-cubic structures made of SiO<sub>2</sub> spheres by self-assembly cannot form a photonic bandgap. We used *a*-Si chemical vapor deposition and wet chemical etching to successfully invert the periodic structures from SiO<sub>2</sub>/air into air/Si with a relatively higher refractive index contrast. The key deposition condition is the extremely low partial pressure of SiH<sub>4</sub> gas, which leads to a long mean free path of Si atoms and conformal growth on silica spheres. Unity reflectance occurs at a wavelength of 1.3  $\mu$ m in <100> and <111> directions.

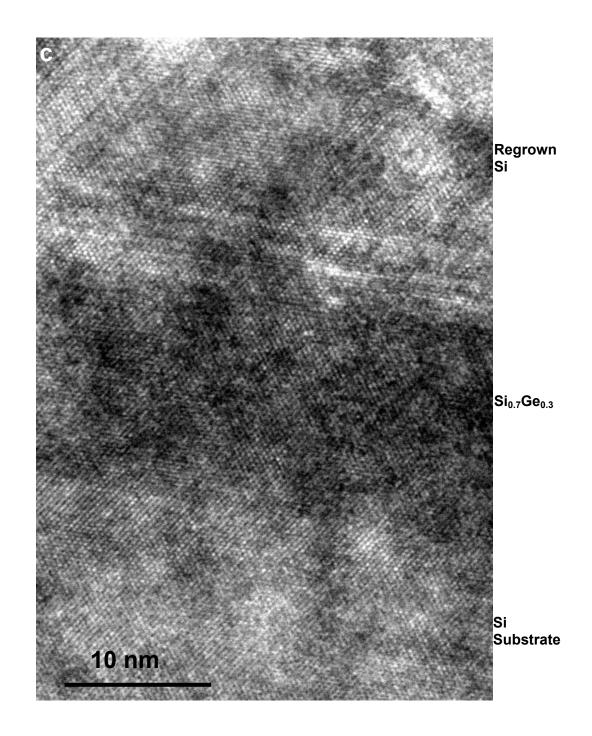

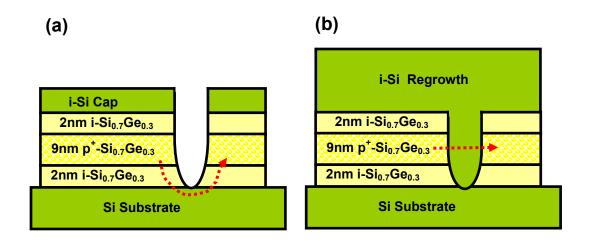

The usefulness of Si-based quantum dot devices is limited by the existence of defect states related to the  $SiO_2$  passivation, resulting in irreproducible and undesired characteristics. A new nanopatterning technique of Si/SiGe heterostructures based on the AFM local oxidation and selective wet etching has been developed to fabricate SiGe quantum dot devices. To remove the negative effects of SiO<sub>2</sub>, the surface of patterned SiGe dots was passivated by silicon epitaxial regrowth with in-situ hydrogen pre-baking

at  $T \le 800$  °C. The regrowth interface was epitaxial, characterized by SIMS, photoluminescence, and cross-section TEM. In contrast with the unpassivated SiGe quantum dot device, the passivated SiGe single-hole transistor exhibits reproducible Coulomb blockade oscillations.

### ACKNOWLEDGEMENTS

First of all, I would like to thank my advisor, Prof. James Sturm, for his guidance and support of this research. His aggressive optimism, deep insight, and passionate attitude to both research and teaching always inspire me and whole group. I feel very lucky to be able to work with such a professor.

Acknowledgements are specially given to Prof. Daniel Tsui who not only allowed me to use low-temperature measurement facility in his group, but also helped me to clarify the basic concept in physics. I want to thank Prof. Sigurd Wagner for allowing me to use his group's PECVD equipment and many helpful discussions. That he and Prof. Mansour Shayegan took their cost time in reading my thesis is also appreciated. Dr. Nan Yao helped me for high-resolution TEM observations and crosssection TEM sample preparation. At the beginning of QD research, Dr. Leonid Rokhinson (now at Purdue University) showed me how to do AFM nanolithography and low-temperature measurements. The collaborators of NEC research Labs at Princeton, Dr. David Norris (now at University of Minnesota) and Dr. Yuri Vlasov (now at IBM), provided state-of-art self-assembly samples. They are all cordially appreciated.

I would like to thank the colleagues in our group (Prof. Sturm) and Prof. Tsui's group for their help and discussions. Among them, special thanks go to Dr. Kiran Pangal, who showed me the fabrication process of poly-Si TFTs at the beginning. Dr. Eric Stewart showed me how to operate RTCVD. Rebecca Peterson maintains the good condition of our RTCVD and also proofread my thesis draft. Troy Graves-Abe upgrades our group computer and software and read my thesis. Dr. Gabor Csathy, Wangli Li, and Keji Lai helped my low-temperature measurements. Dr. Iris Hsu, Dr. Malcolm Carroll, Dr. Richard Huang, Haizhou Yin, Ke Long, and Kun Yao spent many time with me together in the lab. They make the lab a wonderful environment and a lot of fun.

vi

I feel really fortunate to be surrounded with the talented faculty and students of Princeton University, who create a friendly and instructive research atmosphere. Special mention goes to Dr. Helena Gleskova and Joseph Palmer who keeps the instruments in the cleaning room well operated. I am also indebt to Karen Williams and Carolyn Amesen for their kind help during my study.

Finally, I want to thank my parents. It's their love, encouragement, and sacrifice that bring me, a little boy in Northeast of China, up to Princeton University. I also want to express my deepest appreciation to my wife, Qingjuan. Her constant love, support, patience and sacrifice helped me through the difficult time and make this thesis to be real. This thesis is dedicated to them.

# CONTENTS

| Abst | tract  |           |                                             | iv |

|------|--------|-----------|---------------------------------------------|----|

| Ack  | nowled | gements   |                                             | vi |

| I.   | Intr   | oduction  |                                             | 1  |

|      | 1.1    | Motiva    | tion                                        | 1  |

|      | 1.2    | Si-Base   | ed Thin Films                               | 2  |

|      |        | 1.2.1     | CVD Growth of <i>a</i> -Si and Poly-Si      | 3  |

|      |        | 1.2.2     | Crystallization of <i>a</i> -Si             | 4  |

|      |        | 1.2.3     | Epitaxial Growth of Si and SiGe             | 4  |

|      | 1.3    | Si-Base   | ed Quantum Devices                          | 6  |

|      | 1.4    | Thesis    | outline                                     | 6  |

|      | Refe   | rences    |                                             | 8  |

| II.  | Solie  | l Phase ( | <b>Crystallization of Amorphous Silicon</b> | 9  |

|      | 2.1    | Introdu   | iction                                      | 9  |

|      |        | 2.1.1     | Why Poly-Si TFTs?                           | 9  |

|      |        | 2.1.2     | Solid-Phase Crystallization of <i>a</i> -Si | 10 |

|      |        | 2.1.3     | Fabrication of Polysilicon TFTs             | 11 |

|      |        | 2.1.4     | Microstructure of SPC Polysilicon           | 14 |

|      | 2.2    | Single-   | Grain Silicon Film at Designed Locations    | 16 |

|      | 2.2.1    | Motivation                                              | 16     |

|------|----------|---------------------------------------------------------|--------|

|      | 2.2.2    | Experimental Details                                    | 17     |

|      | 2.2.3    | Results and Discussion                                  | 19     |

| 2.3  | Polysil  | icon Film with Large Grain Size and Low Intragranular I | Defect |

|      | Density  | y by Removal of Underlying Oxide                        | 22     |

|      | 2.3.1    | Introduction                                            | 22     |

|      | 2.3.2    | Experimental Details                                    | 23     |

|      | 2.3.3    | Effects of Underlying Oxide Removal on Grain Size       |        |

|      |          | Enhancement                                             | 25     |

|      | 2.3.4    | Effects of Underlying Oxide Removal on Intragranular    | Defect |

|      |          | Density                                                 | 30     |

| 2.4  | Summa    | ary                                                     | 34     |

| 2.5  | Future   | Work                                                    | 35     |

|      | 2.5.1    | Gate-All-Around TFTs                                    | 35     |

| Refe | rences   |                                                         | 37     |

|      |          |                                                         |        |

| A-Si | Deposit  | ion for 3-D Silicon Photonic Bandgap Crystals           | 41     |

| 3.1  | Introdu  | iction                                                  | 41     |

| 3.2  | Self-As  | ssembled Opals                                          | 43     |

| 3.3  | Infiltra | tion of a-Si by CVD                                     | 44     |

|      | 3.3.1    | A-Si Deposition by PECVD                                | 44     |

|      | 3.3.2    | Si Film Deposition by LPCVD                             | 46     |

| 3.4  | Inversi  | on of Opal Structures                                   | 52     |

| 3.5  | Optical  | Characteristics of Inverted Opals                       | 53     |

| 3.6  | Pattern  | ing Inverted Opals                                      | 55     |

III.

| 3.7  | Summary | 56 |

|------|---------|----|

| Refe | rences  | 58 |

| IV. | <b>Review of AFM Nanolithography</b> |                              | 60 |

|-----|--------------------------------------|------------------------------|----|

|     | 4.1                                  | History and Development      | 60 |

|     | 4.2                                  | Instrumentation Issues       | 65 |

|     | 4.3                                  | AFM Nanolithography Examples | 68 |

|     | 4.4                                  | Summary                      | 72 |

|     | Refe                                 | rences                       | 73 |

| V. | AFN                                             | <b>NFM Lithography Nanopatterning of Si/SiGe Heterostructures and</b> |    |  |  |  |

|----|-------------------------------------------------|-----------------------------------------------------------------------|----|--|--|--|

|    | Epit                                            | Epitaxial Silicon Regrowth                                            |    |  |  |  |

|    | 5.1                                             | Introduction                                                          | 76 |  |  |  |

|    | 5.2 Experimental Details of AFM Local Oxidation |                                                                       |    |  |  |  |

|    | 5.3                                             | AFM Local Oxidation of SiGe Alloy                                     | 78 |  |  |  |

|    | 5.4                                             | Nanopatterning of Si/SiGe Heterostructures                            | 83 |  |  |  |

|    | 5.5                                             | SiGe Quantum Dot Device                                               | 87 |  |  |  |

|    | 5.6                                             | Motivation for Hetero-Epitaxial Dot Passivation 9                     |    |  |  |  |

|    | 5.7                                             | Planar Regrowth Process of Epitaxial Silicon on SiGe and Materia      | ıl |  |  |  |

|    |                                                 | Characterization                                                      | 94 |  |  |  |

|    |                                                 | 5.7.1 Cleaning and Epitaxial Condition                                | 94 |  |  |  |

|    |                                                 | 5.7.2 SIMS Ananlysis                                                  | 94 |  |  |  |

|    |                                                 | 5.7.3 Photoluminescence                                               | 96 |  |  |  |

|    | 5.8                                             | Epitaxial Regrowth of Silicon on Nanopatterned Surfaces               | 98 |  |  |  |

|    |                                                 | 5.8.1 Growth Procedure                                                | 98 |  |  |  |

|       | 5.8.2 Cross-Section TEM Observation                              | 99  |

|-------|------------------------------------------------------------------|-----|

| 5.9   | Electrical Characteristics of Nanolines after Epitaxial Regrowth |     |

|       |                                                                  | 105 |

| 5.10  | Summary                                                          | 107 |

| Refer | rences                                                           | 108 |

| VI.                                        | Elec                                                                                                                      | Electrical Characteristics of SiGe Single-Hole Transistors Fabricated by |                                                            |     |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|-----|--|

|                                            | AFN                                                                                                                       | 1 Local (                                                                | <b>Oxidation and Silicon Epitaxial Regrowth</b>            | 110 |  |

|                                            | 6.1                                                                                                                       | Introdu                                                                  | iction                                                     | 110 |  |

|                                            | 6.2                                                                                                                       | 2 Theoretical Background                                                 |                                                            | 113 |  |

|                                            | <ul><li>6.2.1 Coulomb Blockade Effect</li><li>6.2.2 Energies in QD System</li><li>6.2.3 Estimate of QD Energies</li></ul> |                                                                          | Coulomb Blockade Effect                                    | 113 |  |

|                                            |                                                                                                                           |                                                                          | Energies in QD System                                      | 116 |  |

|                                            |                                                                                                                           |                                                                          | Estimate of QD Energies                                    | 118 |  |

| 6.2.4 Period of Coulomb Blockade Oscillati |                                                                                                                           | Period of Coulomb Blockade Oscillations                                  | 120                                                        |     |  |

|                                            |                                                                                                                           | 6.2.5                                                                    | Lineshape of Coulomb Blockade Oscillations                 | 121 |  |

|                                            |                                                                                                                           | 6.2.6                                                                    | Conductance Dependence on Drain Voltage                    | 123 |  |

|                                            | 6.3                                                                                                                       | Device                                                                   | Fabrication Process                                        | 125 |  |

|                                            | 6.4                                                                                                                       | Calcula                                                                  | ation of Tunnel Barriers and Capacitances of Fabricated QI | Ds  |  |

|                                            |                                                                                                                           |                                                                          |                                                            | 129 |  |

|                                            |                                                                                                                           | 6.4.1                                                                    | Tunnel Barriers at Narrow Regions                          | 129 |  |

|                                            |                                                                                                                           | 6.4.2                                                                    | Capacitance in QD Device                                   | 134 |  |

|                                            | 6.5                                                                                                                       | Electric                                                                 | cal Characteristics of SiGe QD Devices                     | 136 |  |

|                                            |                                                                                                                           | 6.5.1                                                                    | Quantum Dot Device without Top Gate                        | 136 |  |

|                                            |                                                                                                                           | 6.5.2                                                                    | Quantum Dot Device without Top Gate                        | 140 |  |

|                                            | 6.6                                                                                                                       | Discus                                                                   | sion                                                       | 145 |  |

|                                                                       | 6.7    | Summary                                                   | 147  |  |

|-----------------------------------------------------------------------|--------|-----------------------------------------------------------|------|--|

|                                                                       | 6.8    | Future Work                                               | 148  |  |

|                                                                       |        | 6.8.1 QD in Si/SiGe 2DHG                                  | 148  |  |

|                                                                       |        | 6.8.2 QD in Si/SiGe 2DEG                                  | 150  |  |

|                                                                       | Refe   | erences                                                   | 151  |  |

|                                                                       |        |                                                           |      |  |

| VII.                                                                  | Cone   | clusions                                                  | 154  |  |

|                                                                       |        |                                                           |      |  |

| Appe                                                                  | ndix A | A. Recipe of a-Si PECVD Growth                            | 157  |  |

| Appe                                                                  | ndix B | <b>3. Example Script Program of AFM Nanolithography f</b> | or   |  |

|                                                                       |        | a QD Device                                               | 158  |  |

| Appe                                                                  | ndix C | C. Medici Simulation of Potential Barrier and Capacita    | nces |  |

|                                                                       |        | in QD                                                     | 160  |  |

| Appendix D. Publications and Presentations Resulting From This Thesis |        |                                                           |      |  |

# **LIST OF TABLES**

Table 1-1.

Semiconductor materials in IC market.

1

**Table 2-1.** Electrical characteristics of polycrystalline silicon n-channel and p-channelTFTs (W/L =  $50\mu m/2\mu m$ ) with gate oxides of  $250^{\circ}$ C PECVD oxide and  $1000^{\circ}$ Cthermal oxide.13

**Table 3-1.** Semiconductor materials and their refractive index and absorption edge.

45

# **LIST OF FIGURES**

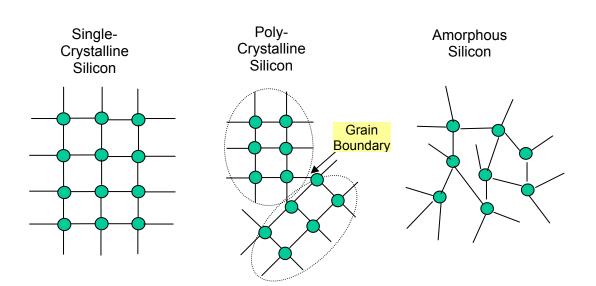

Figure 1-1. Crystalline structure of c-Si, poly-Si and *a*-Si.

2

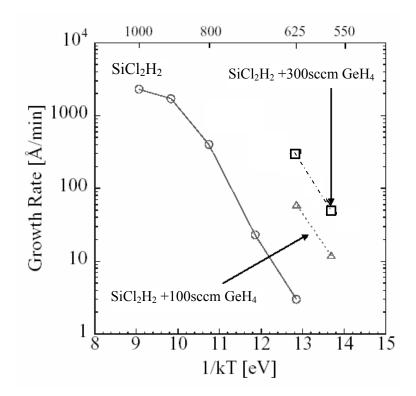

**Figure 1-2.** Growth rates of single-crystalline Si and Si<sub>1-x</sub>Ge<sub>x</sub> vs. inversed growth temperatures. Si growth parameters include a gas flow of 26 sccm DCS and 3 lpm H<sub>2</sub> at a pressure of 6 torr. GeH<sub>4</sub> (0.8% in H<sub>2</sub>) is added for Si<sub>1-x</sub>Ge<sub>x</sub> growth. 5

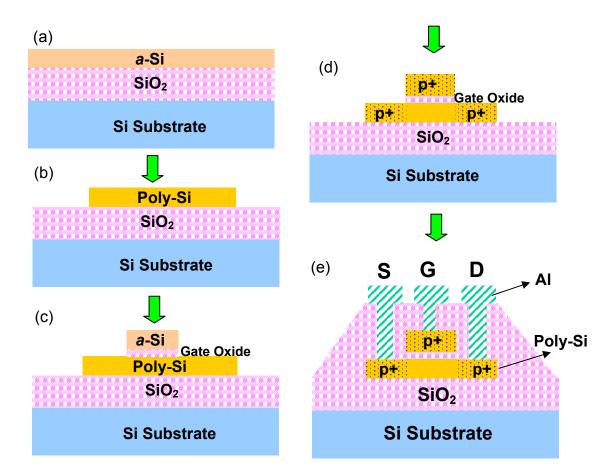

**Figure 2-1.** Fabrication process of p-channel poly-Si TFTs. (a) a-Si film deposition; (b) SPC of a-Si and active island patterning; (c) gate oxide and *a*-Si gate deposition and patterning; (d) boron ion implantation and activation; (e) passivation oxide deposition with subsequent hole opening and aluminum metal contact. 11

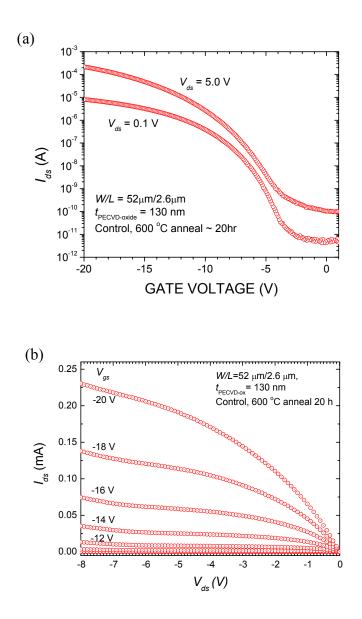

Figure 2-2.Electrical characteristics of (a) drain current vs. gate voltage and (b) draincurrent vs. drain voltage for p-channel TFTs.12

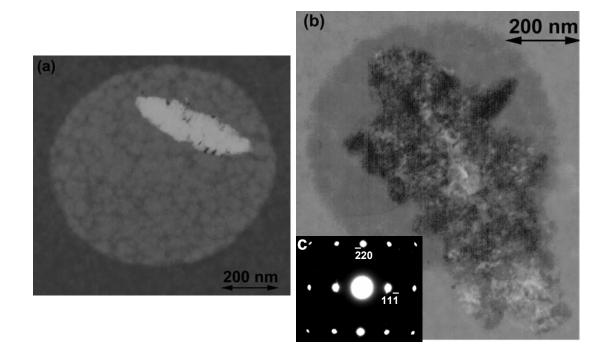

**Figure 2-3.** (a) TEM observation of polysilicon films after anneal at 600 °C for 16 hr without hydrogen plasma treatment (control sample) shows grain size  $0.3-0.8 \mu m$ . Inset is the diffraction pattern. (b) Schematic of poly-Si microstructure composed of grain boundaries and intragranular defects. 15

**Figure 2-4.** Potential barriers in poly-Si, which are due to the charge trapping at the grain boundaries. 15

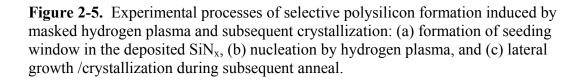

**Figure 2-5.** Experimental processes of selective polysilicon formation induced by masked hydrogen plasma and subsequent crystallization: (a) formation of seeding window in the deposited  $SiN_x$ , (b) nucleation by hydrogen plasma, and (c) lateral growth /crystallization during subsequent anneal. 17

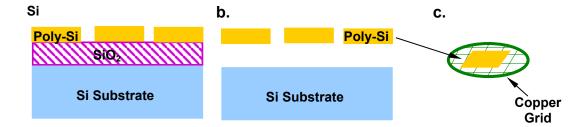

**Figure 2-6.** TEM sample preparation: (a) active island patterning, (b) film lift off by selective wet etching, and (c) film after pick-up by copper grids.

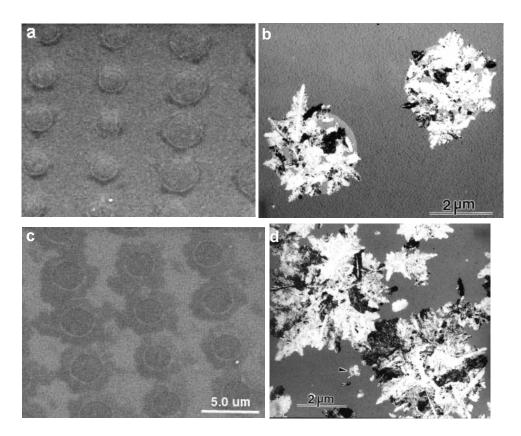

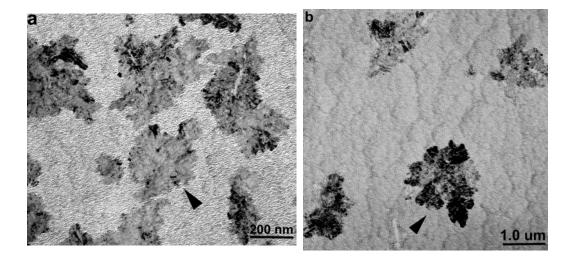

**Figure 2-7.** SEM (a & c) and TEM (b & d) micrographs of lateral growth from the nucleation sites induced by hydrogen plasma treatment after 600 °C annealing for (a) (b) 6 hr and (c) (d) 10 hr. 19

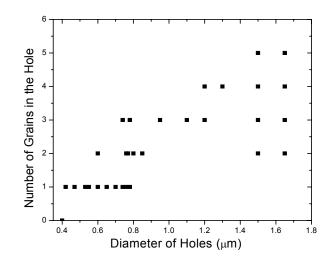

**Figure 2-8.** The relationship between the number of nuclei and the hole size, after hydrogen plasma treatment and annealing at 600 °C for 3 hr. 20

**Figure 2-9.** TEM micrograph of a single nucleus in a hole with a diameter of 0.55(m, induced by hydrogen-plasma exposure and then annealing at 600 (C for (a) 3.0 hr, (b) 8.0 hr, and (c) the SADP of the grain of (b). 21

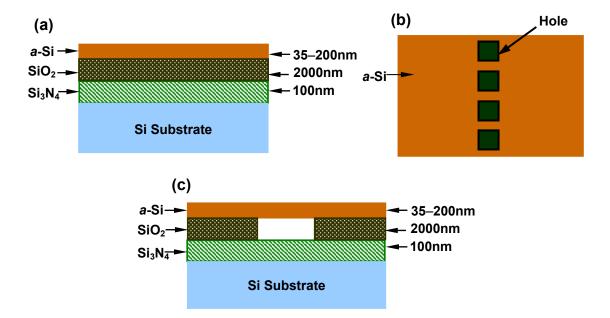

**Figure 2-10.** Fabrication process of amorphous silicon cantilever structure: (a) layer structure; (b) top view before silicon dioxide etching; (c) cross section of cantilever structure after wet etching in buffered oxide etch (10:1). 24

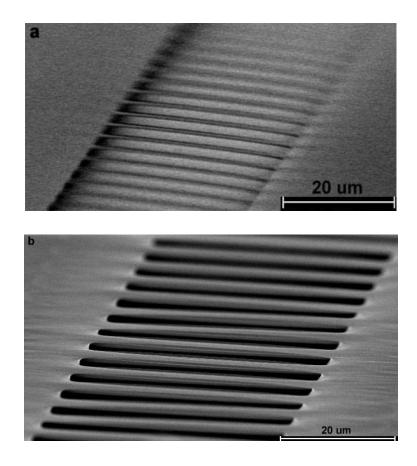

**Figure 2-11.** SEM observations to show the silicon cantilever suspended above the substrate (a) before annealing and (b) after annealing. 25

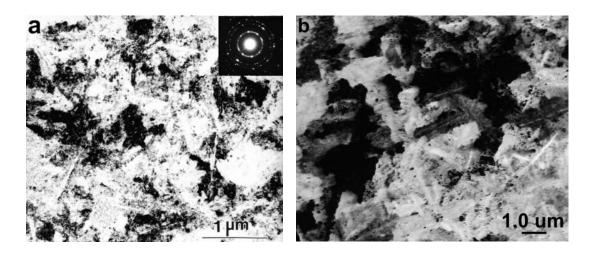

**Figure 2-12.** Plan-view TEM micrographs to show the grain size of fully-crystallized polysilicon films after annealing at 600 °C for 24 hr in (a) control region with underlying SiO<sub>2</sub> (grain size ~ 0.6  $\mu$ m) and (b) cantilever region without underlying SiO<sub>2</sub> (grain size ~ 3.0  $\mu$ m). Inset of (a) is the diffraction pattern of polysilicon films.

Figure 2-13. TEM observations of the grain density and grain size in the control areaand (b) suspended films after annealing at 600 °C for 14 hr before completecrystallization.26

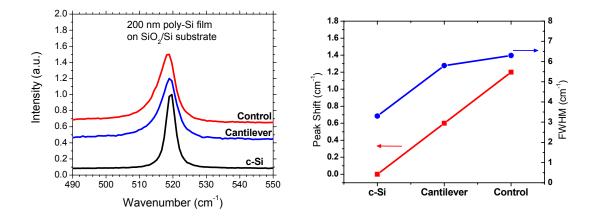

**Figure 2-14.** (a) Raman spectra and (b) absolute value of peak-shift and FWHM of polysilicon films in the control region and cantilever region, and of <100>-orientated single-crystalline silicon substrate.

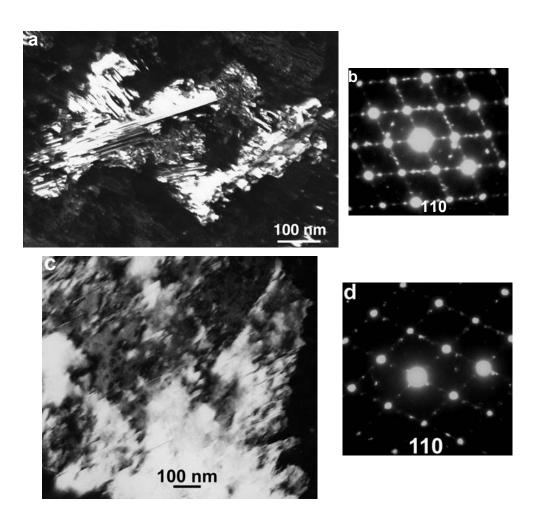

**Figure 2-15.** Dark-field TEM micrographs and their selected area (~ 300 nm in diameter) diffraction pattern in the control sample (a and b) and in the cantilever sample (c and d). Streaks and extra spots in the SADP of (b) and (d) with <110> crystallographic orientations parallel to the electron beam result from the intragranular defects. 31

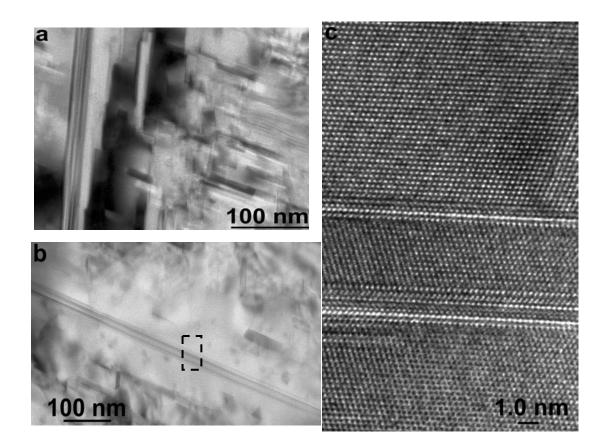

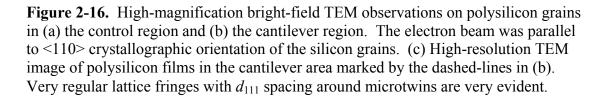

**Figure 2-16.** High-magnification bright-field TEM observations on polysilicon grains in (a) the control region and (b) the cantilever region. The electron beam was parallel to <110> crystallographic orientation of the silicon grains. (c) High-resolution TEM image of polysilicon films in the cantilever area marked by the dashed-lines in (b). Very regular lattice fringes with  $d_{111}$  spacing around microtwins are very evident.

32

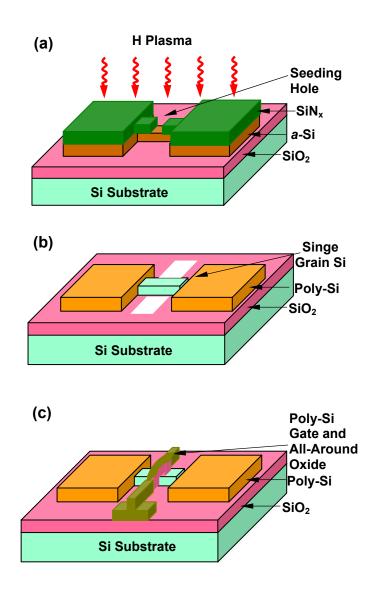

**Figure 2-17.** Fabrication process of gate-all-around TFTs with channel on a singlegrain poly-Si film with less intragranular defects. (a) Selective hydrogen plasma seeding to a small area of a-Si; (b) underlying oxide removal and furnace anneal; (c) deposition of all-around gate oxide and poly-Si gate. 36

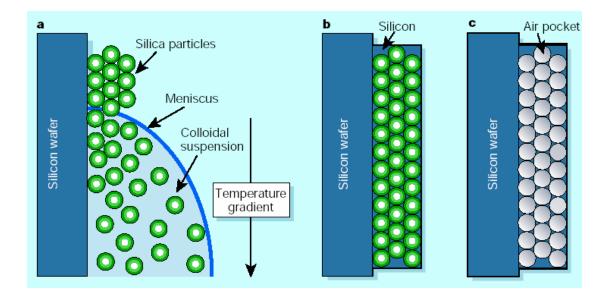

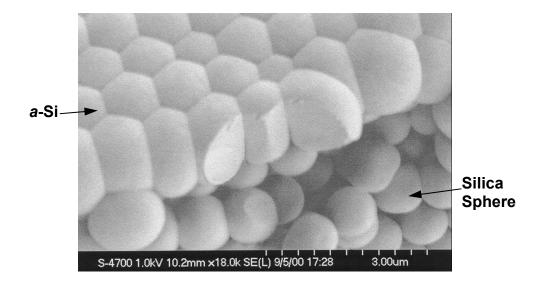

**Figure 3-1.** Fabrication process of 3-D silicon PBCs. (a) Self-assembly of synthetic opals starting from a silica colloid to an ordered 3-D template, (b) voids between silica

spheres filled with silicon by CVD, and (c) removal of the silica spheres by wet etching. 42

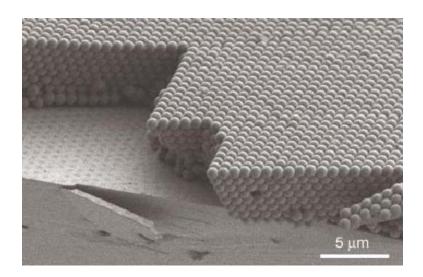

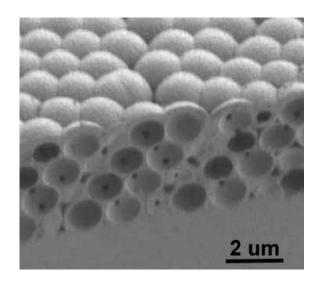

**Figure 3-2.** SEM cross-section image of thin planar opals self-assembled on silicon substrate from silica spheres with diameter of 855 nm. 44

Figure 3-3. SEM cross-section image showing PECVD *a*-Si piled up on the topsurface, blocking *a*-Si infiltration into the opal template.45

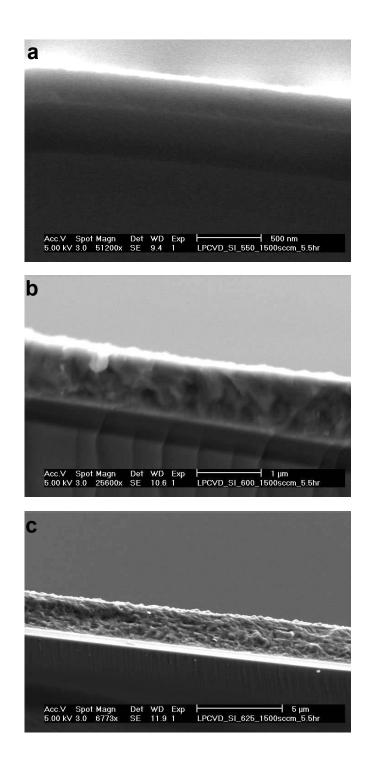

**Figure 3-4.** SEM image of Si films by LPCVD on an oxidized silicon substrate at a temperature of 550 °C in (a), 600 °C in (b), and 625 °C in (c). 47

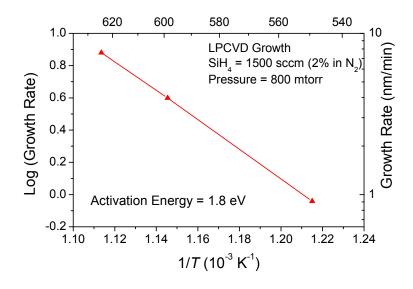

**Figure 3-5.** Growth rate of LPCVD Si films *vs.* growth temperature, keeping SiH<sub>4</sub> (2% in  $N_2$ ) flow at 1500 sccm and pressure at 800 mtorr. 48

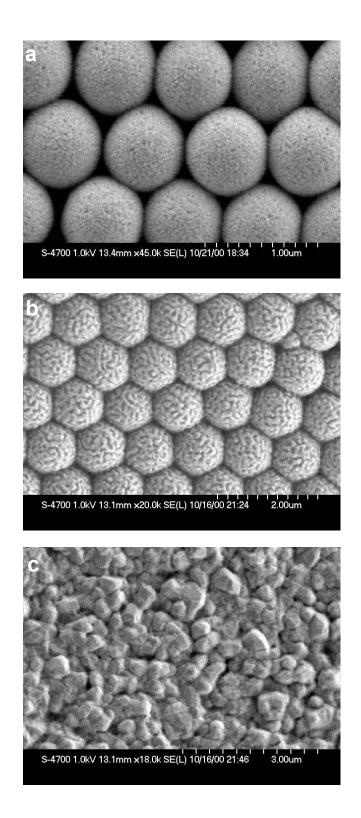

**Figure 3-6.** SEM image of Si films grown by LPCVD on opal templates at temperature of (a) 550 °C, (b) 600 °C, and (c) 625 °C. 49

Figure 3-7. SEM cross-section image of opal structure after Si CVD infiltration at 550 °C. 50

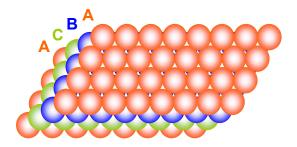

Figure 3-8. Close-packed <111> planes in *fcc* structure.50

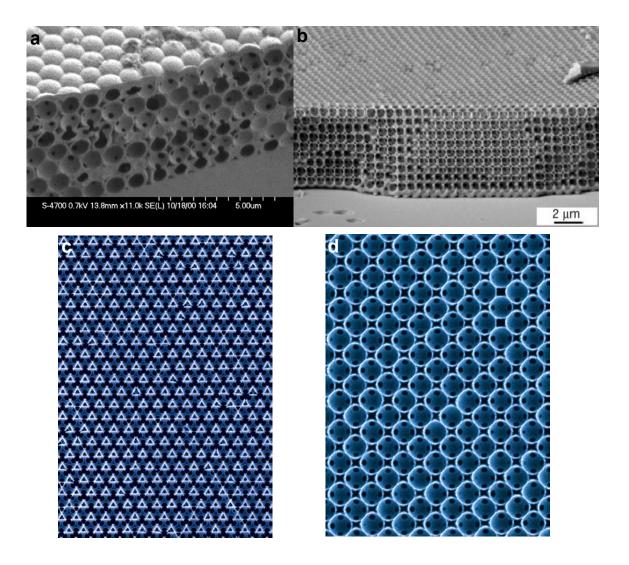

**Figure 3-9.** SEM images of silicon photonic crystals with inverted opal stuctures. (a) and (b) are cross-sections and (c) and (d) are top-views of PBCs along *fcc* [111] (a and c) and [100] (b and d) orientations. 52

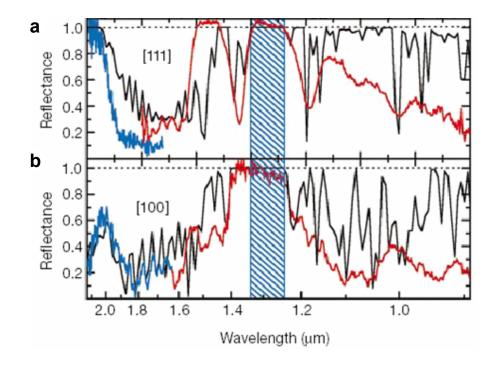

**Figure 3-10.** Optical spectra of silicon inverted opals with incident light normal to [111] in (a) and [100] in (b) directions. The red and blue lines are experimental results from *fcc* samples with a = 1040nm and a = 841nm, respectively. For comparison a calculation is shown in black for a silicon coating sphere radius of 458 nm and an air sphere radius of 354 nm. 54

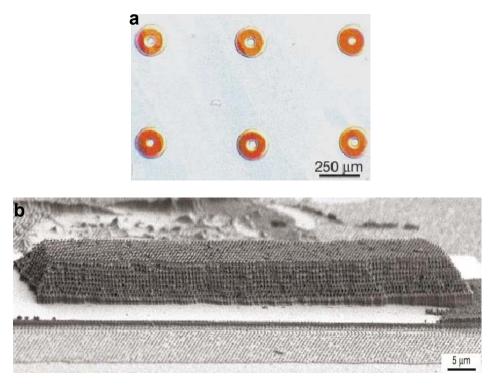

**Figure 3-11.** (a) Optical and (b) SEM cross-section images of patterned silicon photonic crystals by photolithography and RIE. Red color in (a) arises from the crystal diffraction. 55

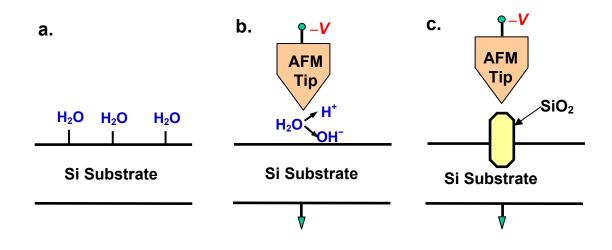

**Figure 4-1.** Process of AFM local oxidation: (a) water vapor adsorbed on silicon surface; (b) water dissociated into  $H^+$  and  $OH^-$  ions by electrical field between AFM tip and Si substrate; and (c) formation of SiO<sub>2</sub> by the reaction  $OH^-$  with Si. 61

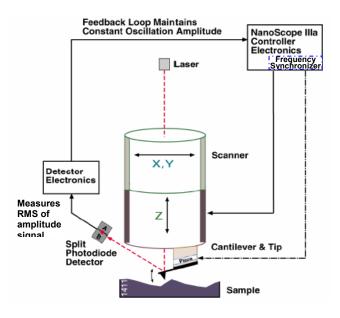

Figure 4-2.Schematic diagram of tapping-mode AFM of Digital Instruments.66

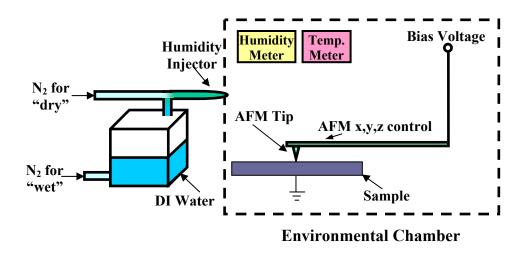

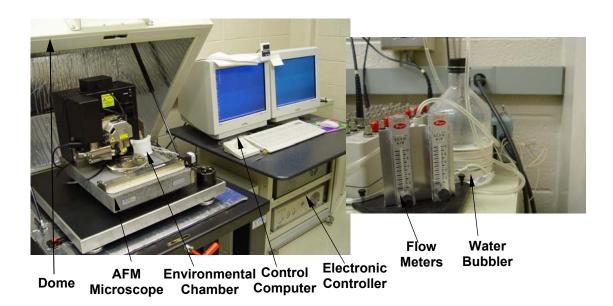

Figure 4-3. AFM set-up for local anodic oxidation.67

| Figure 4-4. Photo picture of NanoMan system and water bubbler. | 68 |

|----------------------------------------------------------------|----|

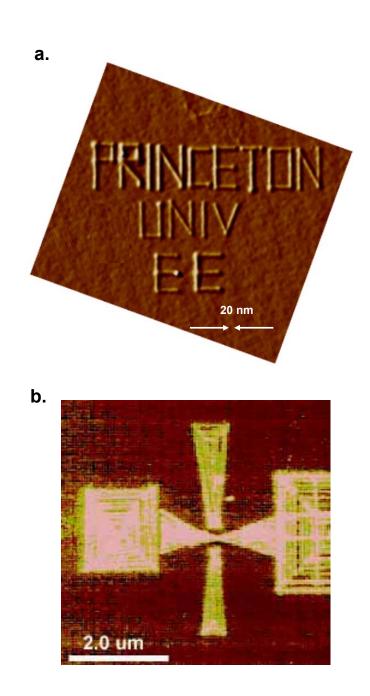

| Figure 4-5. AFM local oxidation on Si surface.                 | 69 |

Figure 4-6. AFM LAO on a Si grown on a relaxed SiGe buffer with RMS roughness  $\sim$  3.0 nm in (a) of 20×20  $\mu$ m<sup>2</sup> area. (b) A high resolution image of the bottom-left corner of (a). 70

**Figure 4-7.** AFM LAO on GaAs with oxidation height  $\sim 10$  nm. 70

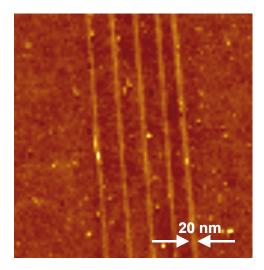

Figure 5-1. Fine oxide lines on strained  $Si_{0.8}Ge_{0.2}$  by AFM lithography at the bias voltage -12V. 78

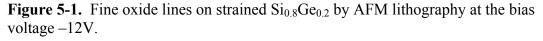

**Figure 5-2.** AFM oxidation lines of  $Si_{0.8}Ge_{0.2}$  with different bias voltages between the tip and sample. The scan speed was 2.0 µm/s, and the tapping amplitude setpoint was 0.04 V. (a) after oxidation; (b) after removing oxide by HF; (c) height profile along arrow lines in (a) and (b). 79

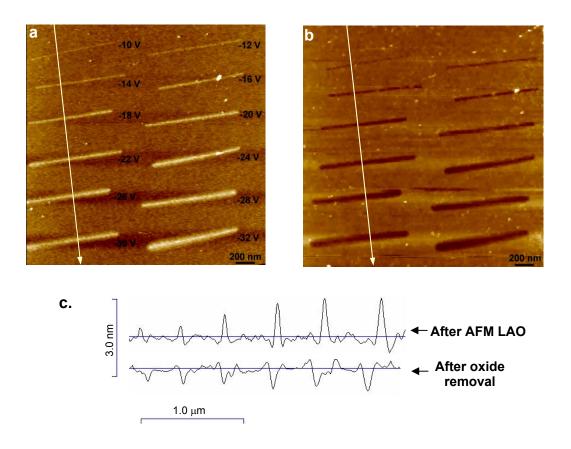

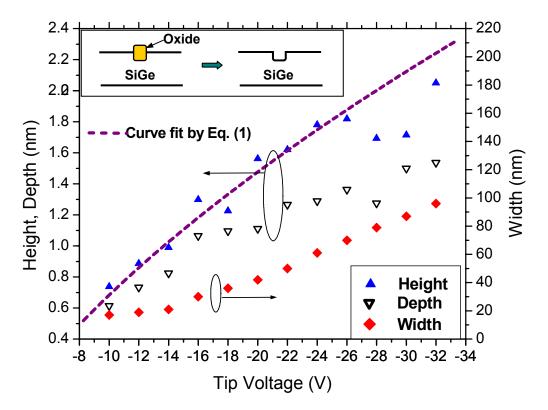

**Figure 5-3.** Height, depth (after HF etching) and FWHM of AFM oxidation lines on strained  $Si_{0.8}Ge_{0.2}$  alloys as a function of different bias voltages between the tip and sample. The writing speed was 1.6 µm/s and amplitude setpoint is 0.04 V. The dashed line is a fit of the height data using Eq. 1. The inset is a schematic of AFM oxidation and oxide removal. 80

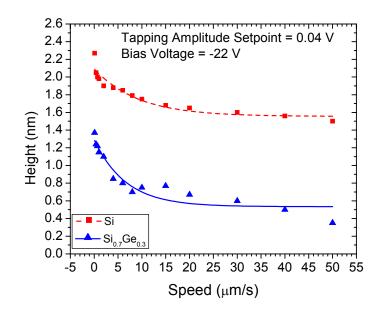

Figure 5-4. Feature height of AFM LAO on silicon and  $Si_{0.7}Ge_{0.3}$  as a function of writing speed. The scattered marks are experimental data, and the dashed and solid lines are logarithmical fitting. 82

Figure 5-5. Comparison of feature heights of AFM oxidation on Si and  $Si_{0.7}Ge_{0.3}$  as a function of the bias voltage. 82

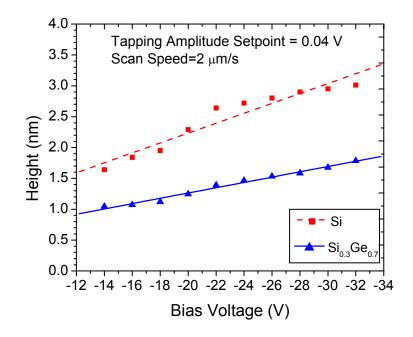

**Figure 5-6.** Process to pattern Si/SiGe nanostructure: (a) Layer structure; (b) Si cap AFM local oxidation; (c) HF dip to remove SiO<sub>2</sub>; (d) selective wet etching to transfer pattern into thick SiGe layer. The degree of lateral etching due to the isotropic wet etch is greater than shown. 84

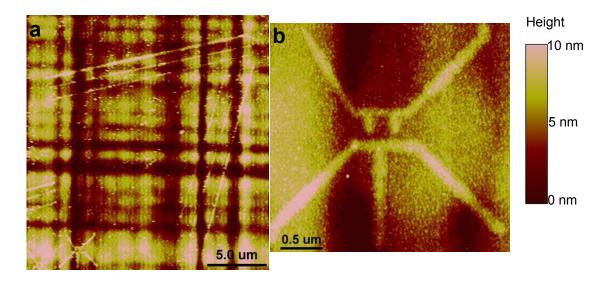

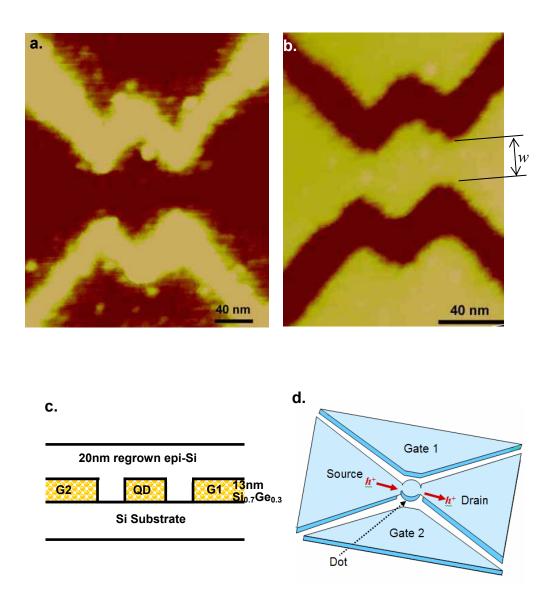

**Figure 5-7.** AFM images of a SiGe quantum dot fabricated by AFM nanopatterning approach (a) after AFM oxidation and (b) after selective wet etching. The device is discussed in Sec. 5.5.

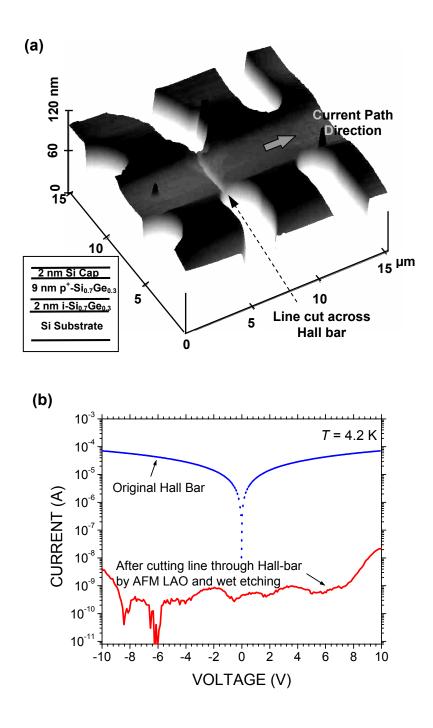

**Figure 5-8.** (a) AFM image of a line cut across Hall bar by AFM local oxidation and selective wet etching in a sample with the layer structure of Fig. 5-6. The sample was pre-patterned by optical lithography and RIE to create mesa Hall bar structure. (b) Hall bar resistance measurement at T= 4.2 K before and after line cutting the Hall bar.

86

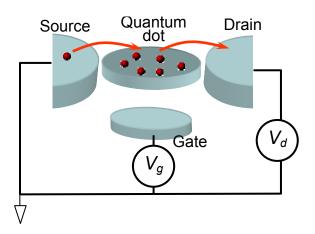

**Figure 5-9.** Schematic diagram of a QD laterally connected to source/drain contacts by tunnel junctions, and to a gate by a capacitor. 88

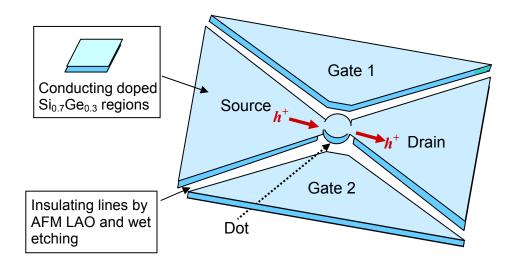

**Figure 5-10.** Schematic diagram of QD fabricated by AFM LAO and wet etching, and path of hole transport in the device. 88

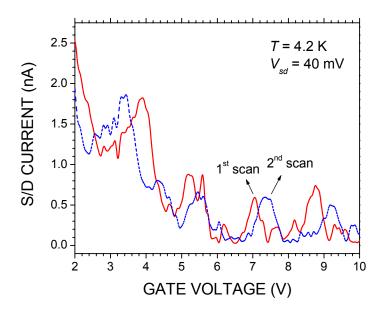

**Figure 5-11.** Source-drain current *vs.* one planar gate voltage at T = 4.2 K and  $V_{ds} = 40$  mV. The other gate was grounded. The solid line represents the electrical results for the 1<sup>st</sup> measurement scan, and the dotted line is for the 2<sup>nd</sup> scan. 90

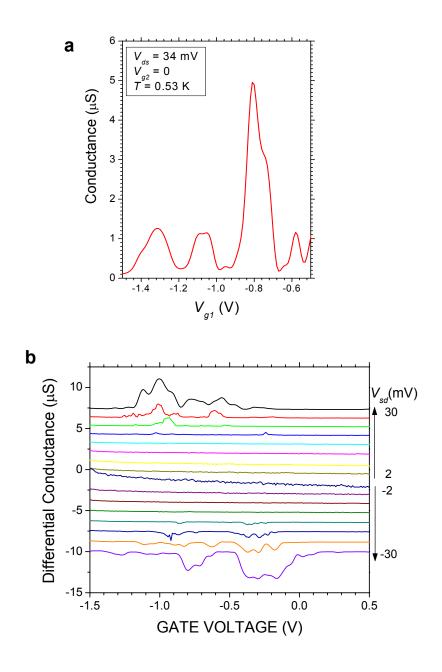

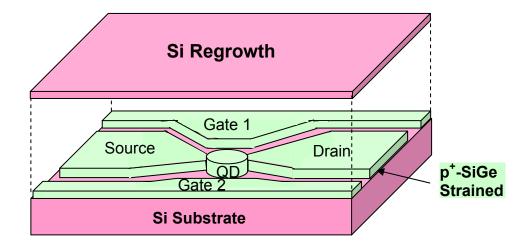

**Figure 5-12.** Electrical characteristics (differential conductance *vs.* gate voltage) of the SiGe quantum dot fabricated by AFM LAO and selective wet etching at T = 0.53 K with source-drain bias at (a) -34 mV and (b) -30 mV to +30 mV with bias step of 4 mV. In (b), all curves are offset by 1.2  $\mu$ S. 91

Figure 5-13. Schematic drawing of SiGe QD device and Si epitaxial regrowth.

93

**Figure 5-14.** Oxygen, carbon, phosphorous, boron and germanium SIMS profiles of a sample with epitaxial regrowth of silicon on strained SiGe layer. Before regrowth, an *in situ* hydrogen bake at 10 torr and 800 °C for 2 min was performed. 95

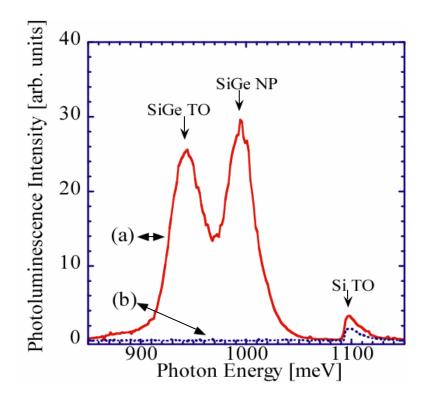

**Figure 5-15.** Photoluminescence spectra of  $Si_{0.8}Ge_{0.2}$  samples at T = 77 K with (a) a "clean" Si/SiGe interface grown without interruption, and (b) a contaminated Si/SiGe interface. The two strong peaks in (a) are from no-phonon (NP) transition and transverse optical (TO) phonon replica in SiGe layer. 97

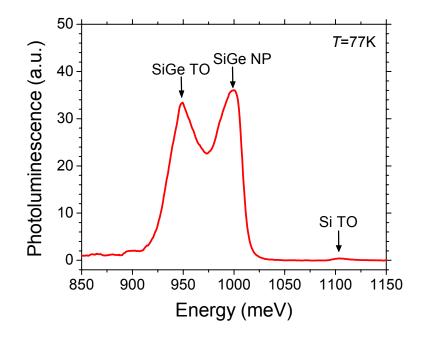

**Figure 5-16.** PL spectrum at T = 77 K of regrown silicon on strained Si<sub>0.8</sub>Ge<sub>0.2</sub>. During regrowth, *in situ* hydrogen pre-baking was at 10 torr and 800 °C for 2 min. 98

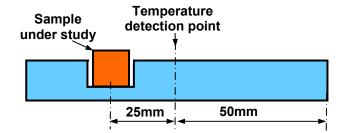

Figure 5-17.Small-piece sample position and temperature monitor position in a 100mm wafer.99

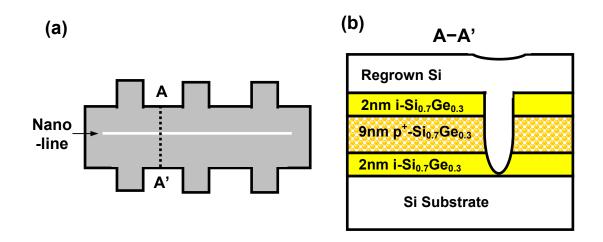

**Figure 5-18.** (a) Nanoline is patterned on a Hall bar by AFM LAO and wet etching; (b) the cross-section of the structure across the line A-A', which was imaged by TEM. 100

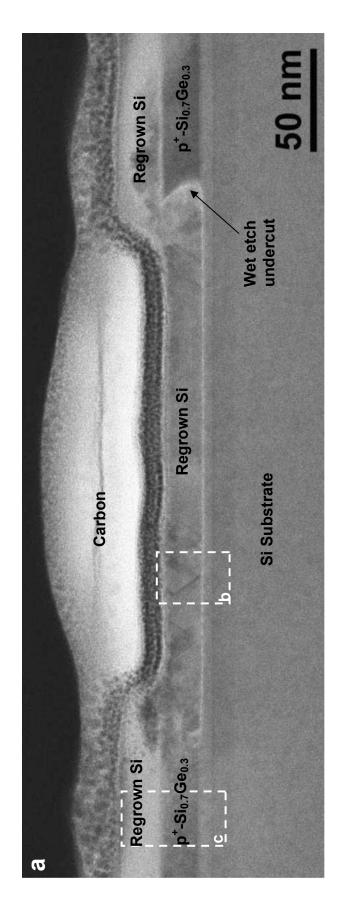

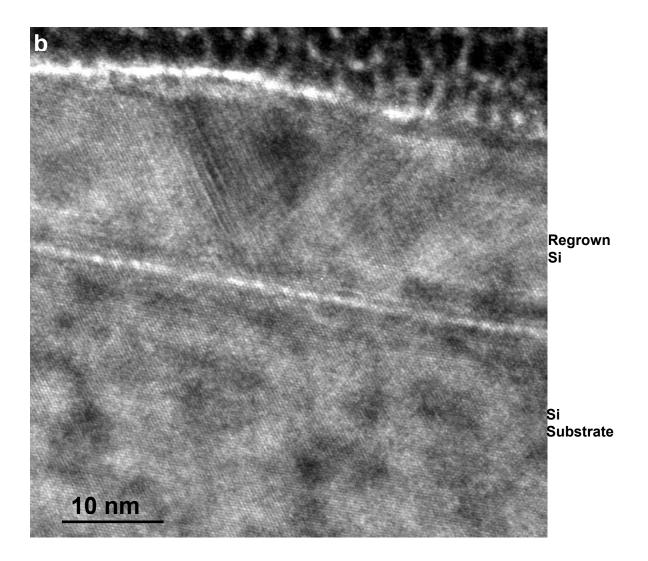

**Figure 5-19.** (a) Cross-section TEM images of regrown Si on a line trench in  $Si_{0.7}Ge_{0.3}$  layer patterned by AFM LAO and wet etching. High-resolution TEM image of (b) regrown Si on Si substrate in the trench, and (c) regrown Si on strained  $Si_{0.7}Ge_{0.3}$  layer outside of the trench. The regions of (b) and (c) are marked by the dashed-line rectangles in (a).

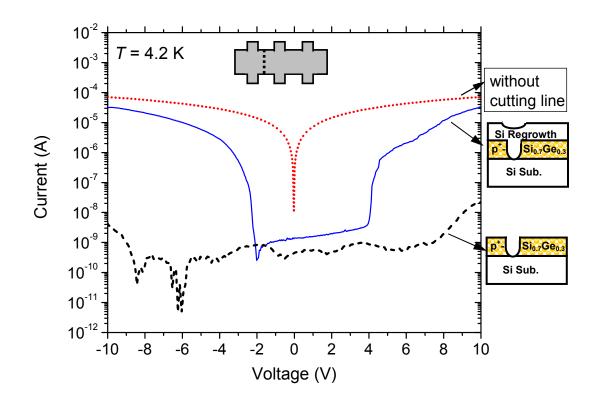

**Figure 5-20.** *I-V* curves across a nanoline in a Hall bar (inset) with and without silicon epitaxial regrowth. After regrowth, the current starts to leak at a lower bias voltage (compared to Fig. 5-8).

Figure 5-21. Current leakage path marked by dotted lines in the samples (a) before and (b) after Si epitaxial regrowth. 106

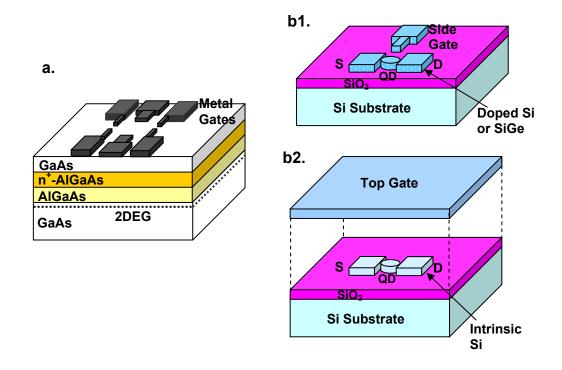

Figure 6-1. Two methods of defining QD: (a) surface depletion of 2-D gas by metal gates, and (b1) and (b2) trench isolation using patterned SOI films. In (b1), the conducting layer is doped Si or SiGe, but in (b2) the transport carriers are generated by the top gate, between which is insulator  $SiO_2$ . 111

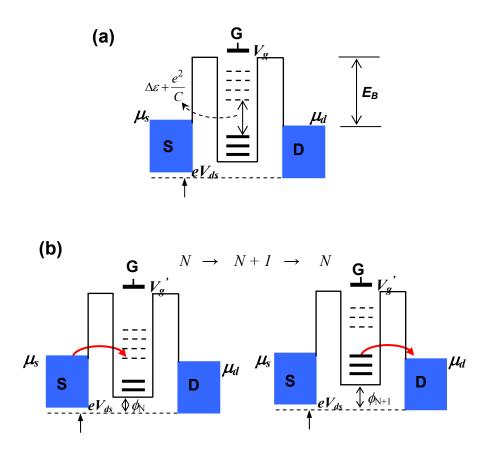

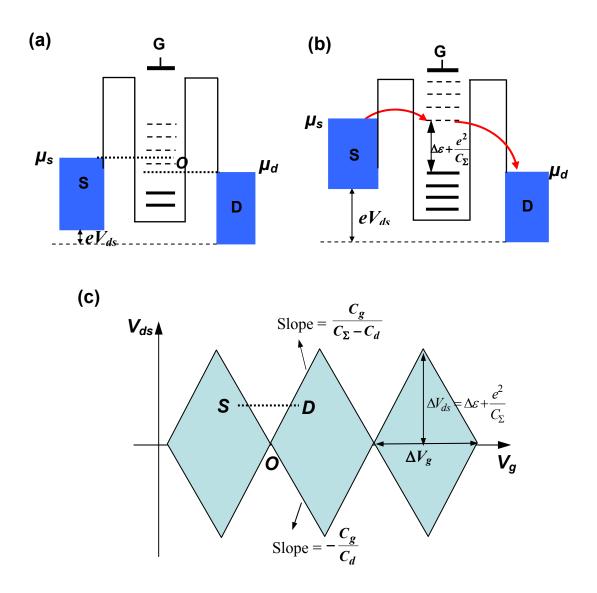

Figure 6-2. Energy diagram of a QD device, showing (a) Coulomb blockade and (b) single electron tunneling of  $N \rightarrow N + 1 \rightarrow N$ . The solid lines in QD represent the quantized energy levels that are occupied by electrons, and the dashed lines represent the energy levels that are empty.  $\Delta \varepsilon$  represents the energy level splitting due to quantum confinement, and  $\phi_N$  represents the electric potential of the dot with N electrons on it. The states in the source and drain reservoirs are filled up to the electrochemical potentials  $\mu_s$  and  $\mu_d$  which are related via the external voltage  $V_{ds} = (\mu_s - \mu_d)/e$ . The gate voltage changes from  $V_g$  in (a) to  $V_g^{3}$  in (b). The labeled 114

$E_B$  is the electron tunneling barrier.

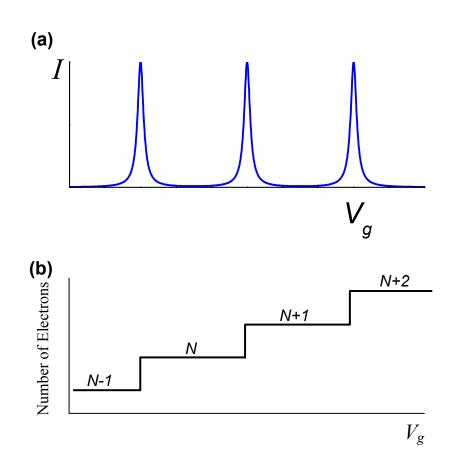

Figure 6-3. (a) Current oscillations and (b) electron number in QD as a function of gate voltage. 115

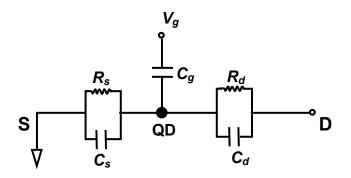

**Figure 6-4.** Equivalent electrical circuit of a single-electron transistor. The junctions of source-dot and dot-drain are made of tunnel resistors  $(R_s, R_d)$  and capacitors  $(C_s, C_d)$ . The dot is also connected to the gate through a capacitor  $C_g$ . 117

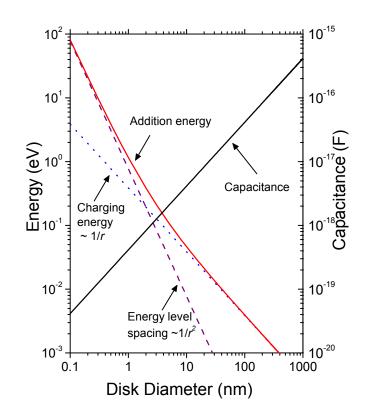

Figure 6-5. QD addition energy (solid-line) and its components: charging energy  $e^2/C$  (dot-line) and energy level spacing  $h/m^*r^2$  in QD (dash-line) vs. disk diameter. The dot is assumed as a thin disk, with  $m^* = 0.4m_0$ . The QD self capacitance  $C = 8\varepsilon_r \varepsilon_0 r$  as a function of disk diameter is also drawn. 119

Figure 6-6. Energy diagram to explain the diamond-shaped Coulomb blockade oscillations (a) at small drain-source bias and (b) at higher source-drain bias at which the Coulomb blockade region is lost, independent of gate voltages. In (c), dot parameters characterized from the diamond are marked. 124

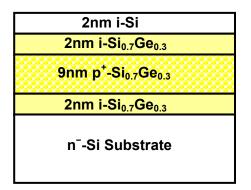

**Figure 6-7.** Layer structure of sample #3386. 125

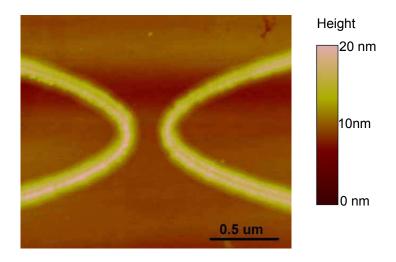

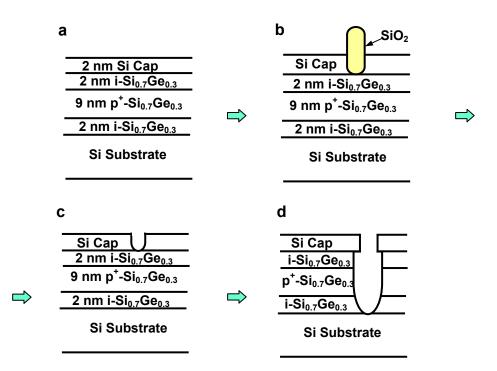

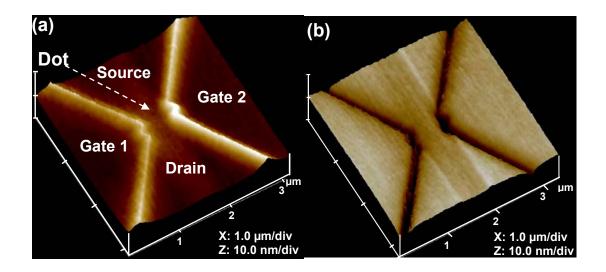

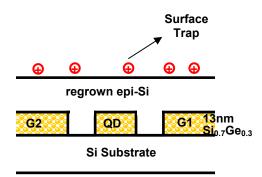

Figure 6-8. (a) AFM images of quantum dot device after AFM oxidation of the top thin Si cap, and (b) after two-step selective wet etching. The gap distance at the narrow region is marked by w. (c) Cross-section of the QD device after epitaxial regrowth. (d) Schematic diagram of a QD and the path of hole transport in the device. 126

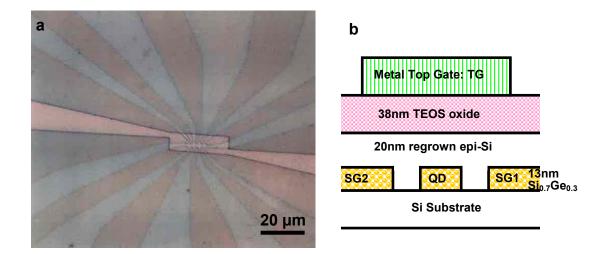

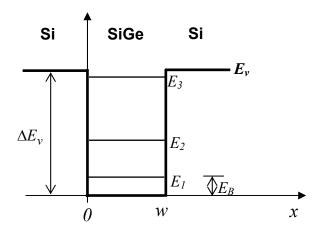

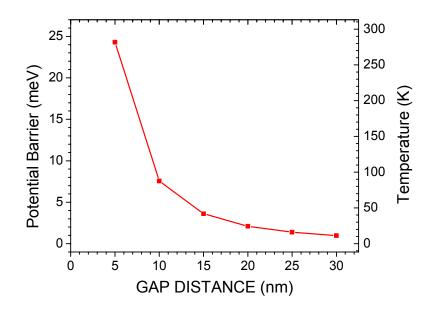

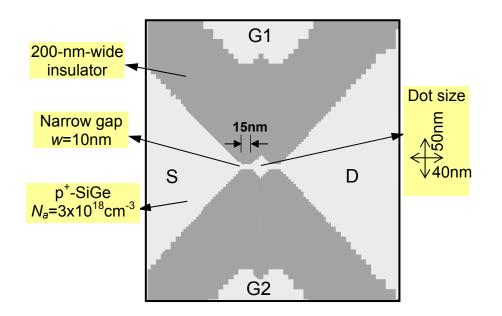

**Figure 6-9.** (a) Photograph of the Hall-bar and the top gate; (b) cross-section of a QD with the top gate. 128 **Figure 6-10.** A quantum well with height of  $\Delta E_v$  and width of w. Energies  $E_1$ ,  $E_2$  and  $E_3$  are quantized energy levels in the well. The energy barrier  $E_B$  is the distance between the  $E_1$  level and the valence band edge in the SiGe. Note the energy scale for holes has been inverted in this figure. 130

**Figure 6-11.** Potential energy barriers as a function of gap distance at the narrow regions. 130

| Figure 6-12 | • Top-view of device structure for Medici simulations. | 132 |

|-------------|--------------------------------------------------------|-----|

|-------------|--------------------------------------------------------|-----|

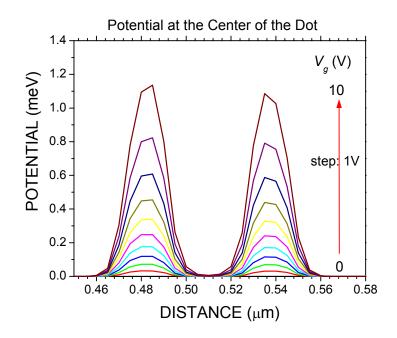

**Figure 6-13.** Potential profile along the device center line from source to drain for different voltages applied to the two planar gates. 132

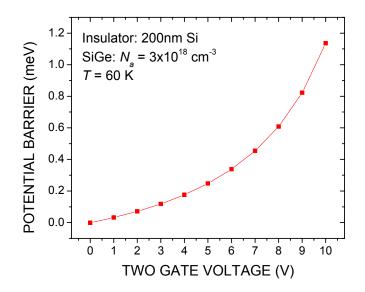

**Figure 6-14.** Medici simulation results of the potential energy barriers at the 10-nmwide gap due to applied-planar gate voltages. The same voltage is assumed on each of the two gates. 133

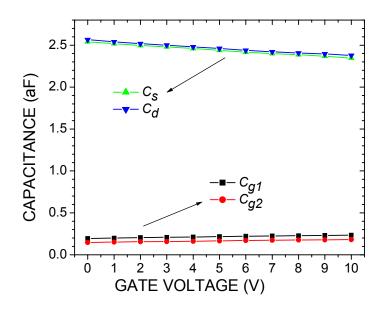

**Figure 6-15.** Capacitances of source-dot  $(C_s)$ , drain-dot  $(C_d)$ , gate1-dot  $(C_{g1})$  and gate2-dot  $(C_{g2})$  as the function of gate voltage. They slightly change with gate voltage.

135

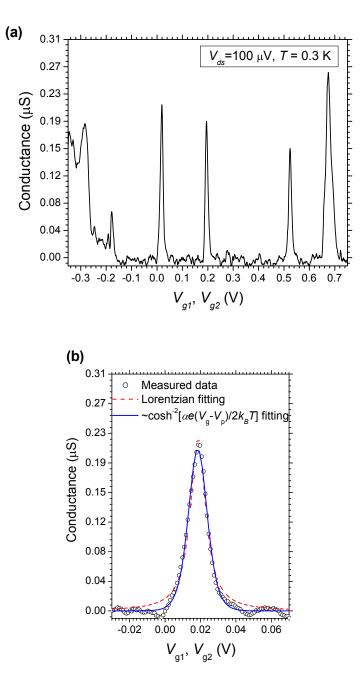

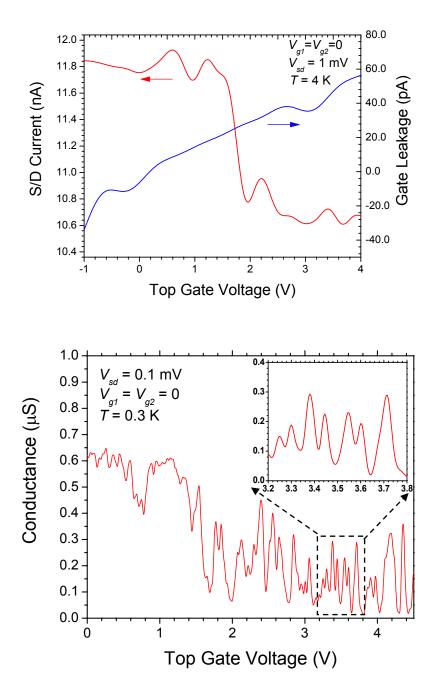

**Figure 6-16.** (a) Quantum dot conductance *vs.* two connected gate voltages at source/drain bias of 100  $\mu$ V and temperature of 0.3 K; (b) conductance peak (open circle) at  $V_g \sim 0.02$  V fitted to Lorentzian (dashed line) and a thermally broadened CB resonance (solid line).

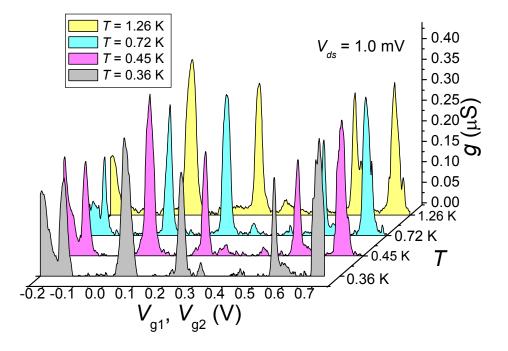

**Figure 6-17.** Coulomb blockade oscillations of the QD device measured at the different temperatures from 0.3 K to 1.3 K. The source-drain bias  $V_{ds}$  is ~ 1.0 mV. 138

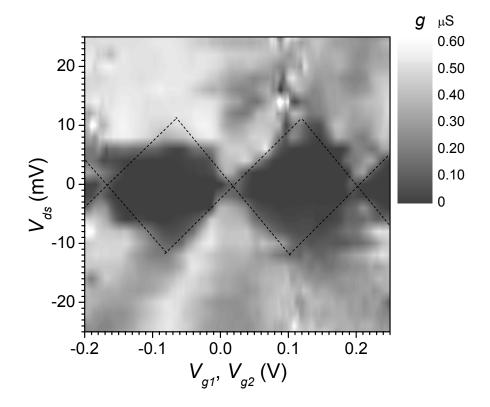

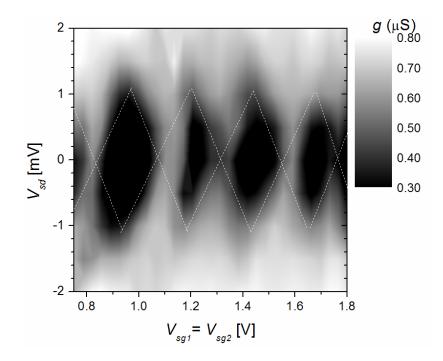

**Figure 6-18.** Differential conductance  $\partial I / \partial V_{ds}$  on a linear gray scale as a function of  $V_{g1}$ ,  $V_{g2}$  for different bias voltages of  $V_{ds}$ . Edge bluntness is thought to be due to the noise from gates voltages. The dotted lines are estimated by eye. 139

Figure 6-19. Schematic drawing of surface charges on Si passivation layer. 140

**Figure 6-20.** Conductance of the QD *vs.* top gate voltage at (a) T = 4 K and (b) T = 0.3 K. The two side-gate voltages are zero, and source-drain bias is 0.1 mV. The inset of (b) shows current oscillations at small range of top gate voltages. 141

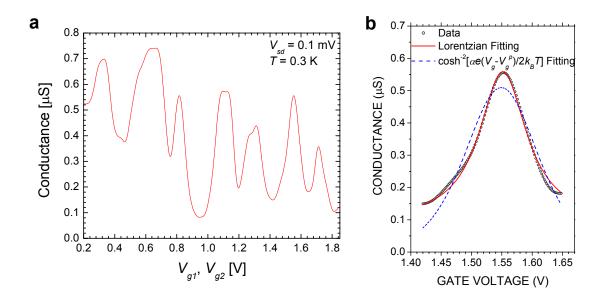

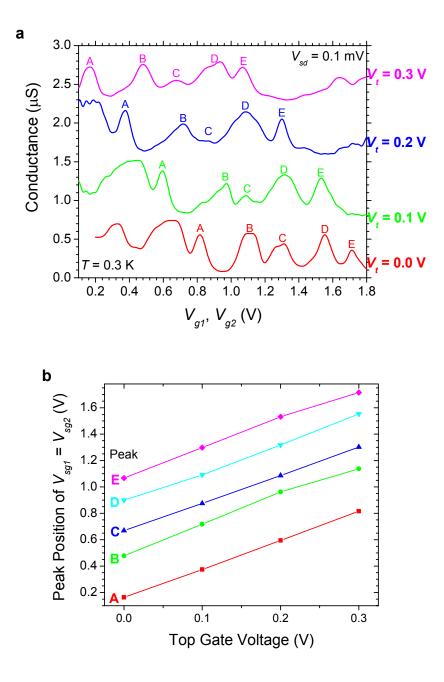

**Figure 6-21.** (a) QD conductance vs. two side-gate voltages (held equal) at T = 0.3 K.  $V_{ds} = 0.1$  mV, and top gate voltage is zero. (b) Measured conductance peak (scattered circle) fitted by a Lorentzian function (solid line) and a function

$$G \propto \cosh^{-2}[\alpha(V_g - V_g^{peak})e/2k_BT]$$

(dashed line). 142

**Figure 6-22.** Differential conductance contour of the QD with drain and two-side gate voltages at T = 0.3 K. The top gate voltage is zero. 142

**Figure 6-23.** Conductance oscillations with two side-gate voltages (held equal) for different top gate voltages. The  $V_{ds} = 0.1$  mV, and T = 0.3 K. The individual curves are offset vertically for different top gate voltages for clarity. (b) Side gate voltage positions for peak A, B, C, D, E *vs.* top gate voltage. 144

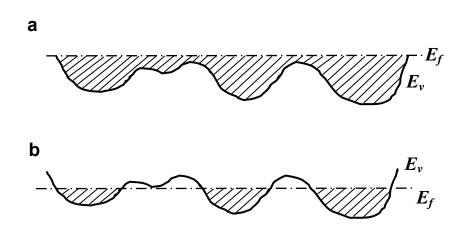

**Figure 6-24.** (a) Schematic drawing of the potential fluctuations along a heavily doped  $p^+$ -SiGe line. (b) The gate voltage pulls Fermi energy  $E_f$  down, and potential barriers for holes along the fluctuating edge of the valence band  $E_v$  define extra isolated islands (QDs). 147

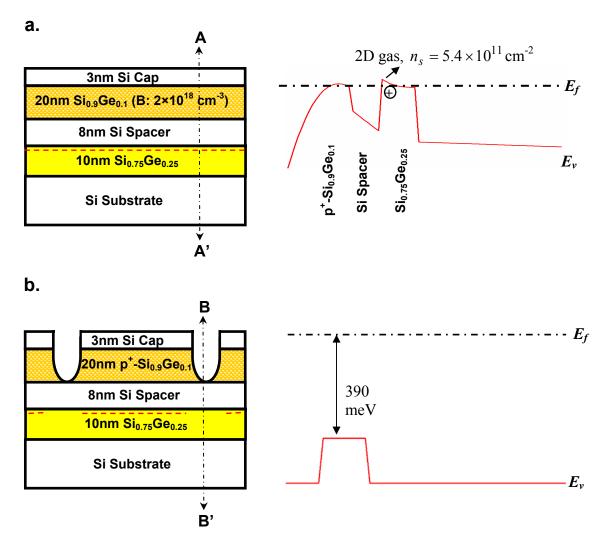

**Figure 6-25.** Layer structure and vertical energy band diagram (a) before (along A-A') and (b) after AFM nanopatterning (along B-B'), where dopant supply layer was removed. Note when the supply layer is removed, the valence band is ~ 390 meV lower than where 2-D gas is present. 149

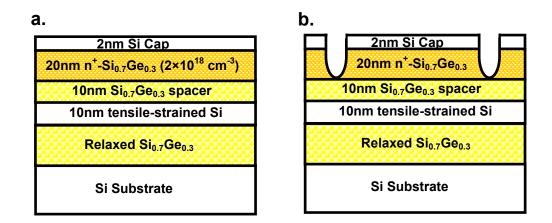

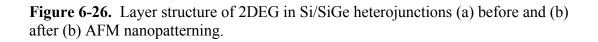

**Figure 6-26.** Layer structure of 2DEG in Si/SiGe heterojunctions (a) before and (b) after (b) AFM nanopatterning. 150

# **Chapter 1**

# INTRODUCTION

#### 1.1 Motivation

Since the electrical transistor was invented in December 1947 by John Bardeen, Walter H. Brattain and William Shockley <sup>[1]</sup>, and the 1<sup>st</sup> commercial silicon transistor was announced in May 1954 by Texas Instrument <sup>[1]</sup>, silicon-based materials have been the dominant semiconductor in the integrated circuit (IC) industry. This success is due to their relatively high temperature stability, excellent insulator interface, and low cost. In one Intel Pentium IV CPU chip there are more than 60,000,000 transistors on a silicon substrate <sup>[2]</sup>. Silicon, which is next to oxygen the most common element in Earth's crust, accounts for 98.6% of the 2002 IC market, and will continue to be the dominant semiconductor material in the near future (see Table 1-1).

| Global IC market by<br>material | 2002 IC market | Predicted<br>2007 IC market |  |

|---------------------------------|----------------|-----------------------------|--|

| Silicon                         | 98.6%          | 97.6%                       |  |

| GaAs and other III-Vs           | 1.2%           | 1.6%                        |  |

| SiGe                            | 0.2%           | 0.8%                        |  |

| Total value (\$ billion)        | 120.5          | 190.8                       |  |

Table 1-1.

Semiconductor materials in IC market <sup>[3]</sup>

Alloys of Column IV elements silicon and germanium (referred to a SiGe), have larger lattice constant and lower energy bandgap than Si. The lower energy bandgap of SiGe leads to a higher current gain in Si/SiGe heterojunction bipolar transistors (HBTs) <sup>[4]</sup>. Tensile strain in silicon, introduced by epitaxially growing Si on a relaxed SiGe layer, can enhance the electron mobility in metal-oxide-semiconductor field-effect-transistors (MOSFETs)<sup>[5]</sup>. All these may explain why SiGe is expected to be the fastest growing semiconductor material in IC industry, with a four-fold increase in IC market share from 2002 to 2007 (Table 1-1).

Therefore, the study to improve performance of Si-based materials and devices and to expand their applications to new fields is important, and will significantly benefit the IC industry. In this thesis, we will study the solid-phase crystallization (SPC) of amorphous Si (*a*-Si) for thin film transistors (TFTs), *a*-Si deposition for threedimensional photonic bandgap crystals (PBCs), and Si/SiGe heterostructure nanopatterning, leading to quantum dot devices.

#### **1.2** Si-Based Thin Films

Figure 1-1. Crystalline structure of c-Si, poly-Si and *a*-Si.

According to crystallinity, silicon materials are divided into three groups: singlecrystalline silicon (c-Si), poly-crystalline silicon (poly-Si), and amorphous silicon (*a*- Si). Their structures are schematically shown in Fig. 1-1. In c-Si, silicon atoms are periodically arranged, forming the diamond cubic lattice structure. Poly-Si has crystalline domains, called grains, which have different crystalline orientations, forming grain boundaries. In *a*-Si films, silicon atoms are randomly situated without long-range crystalline order, although most atoms are still four-fold coordinated. Silicon atom dangling bonds lead to localized states in the energy bandgap of *a*-Si, resulting in lower transport mobilities of *a*-Si films than those of poly-Si and c-Si.

All these thin films are commonly grown by chemical vapor deposition (CVD) from gas sources. Plasmas are sometimes used to enhance the generation of precursor species, and thus increase the deposition rate.

#### 1.2.1 CVD Growth of *a*-Si and Poly-Si

Silicon TFTs are widely used in active matrix liquid-crystal displays (AMLCDs) on glass substrates to address pixels. Large-area, 54-inch LCD displays <sup>[6]</sup> are an example of this technology. Flexible electronics are fabricated on thin substrates of plastic and steel. When substrates are amorphous, silicon thin films grown by CVD are *a*-Si or poly-Si, depending on the parameters of CVD processes, such as gas composition, gas flow rate, substrate temperature, chamber pressure, plasma power, etc. For example, using SiH<sub>4</sub> gas in low-pressure chemical vapor deposition (LPCVD), deposited films are *a*-Si for growth temperatures below 550 °C, and are poly-Si for growth temperatures above 625 °C, as will be shown in Chapter 3. This is because *a*-Si clusters deposited on amorphous surface crystallize to form poly-Si nuclei at temperatures above 600 °C. This is called "as-deposited" poly-Si or "direct deposition". CVD has the advantage of conformal growth compared to evaporation and other methods. Thus we can fill voids and cover complex surfaces. This will be exploited in Chapter 3 to form "inverted opals", which are 3-D PBCs in Si-based materials <sup>[7]</sup>.

#### 1.2.2 Crystallization of *a*-Si

Poly-Si can also be obtained by the crystallization of precursor *a*-Si thin films. Compared with crystallized poly-Si, poly-Si films by "direct deposition" tend to exhibit rough surfaces and smaller grain sizes <sup>[8]</sup>, thus resulting in a relatively low field-effect mobility. The crystallization of *a*-Si can be accomplished by solid-phase crystallization (SPC) or laser crystallization. During laser crystallization, substrate is kept at a low temperature, the top *a*-Si film is melted by a pulsed or continuous laser, and then crystallized in subsequent cooling. TFTs made in laser-crystallized poly-Si films have field-effect mobilities up to 640 cm<sup>2</sup>/Vs for n-channel TFTs and 400 cm<sup>2</sup>/Vs for pchannel TFTs <sup>[9]</sup>, close to those of c-Si. However, laser crystallization requires sophisticated optical instruments for beam uniformity, and has low reproducibility. SPC of *a*-Si by furnace annealing at temperatures above 600 °C is the simplest and most widespread technique. SPC poly-Si has a higher defect density (microtwins and dislocations) in grains than laser-crystallized poly-Si, resulting in lower mobilities of TFTs. The reduction of intragranular defect density and the removal of grain boundaries in poly-Si by SPC will be studied in detail later in Chapter 2.

#### 1.2.3 Epitaxial Growth of Si and SiGe

When the substrate is a single-crystalline silicon wafer, epitaxial CVD growth can occur, leading to a c-Si thin film. Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> has a greater lattice constant than that of Si. The lattice constant depends on the concentrations of Si and Ge:  $a_{SiGe} = (1-x)a_{Si} + xa_{Ge}$ . Thin pseudomorphic SiGe layers which are epitaxially grown on c-Si substrate are under compressive strain in the plane parallel to the surface of Si substrate. This results in the increase of the vertical lattice constant of the strained-SiGe,  $a_{SiGe}^{\perp}$ .

$$a_{SiGe}^{\perp}(x) = a_{Si} \cdot \left[ 1 + \frac{C_{11}(x) + 2C_{12}(x)}{C_{11}(x)} \cdot \frac{a_{SiGe}(x) - a_{Si}}{a_{Si}} \right],$$

(1.1)

where  $C_{11}(x)$  and  $C_{12}(x)$  are elastic constants of Si<sub>1-x</sub>Ge<sub>x</sub>, which can be linearly interpolated between their values for Si and Ge<sup>[10,11]</sup>.

**Figure 1-2.** Growth rates of single-crystalline Si and Si<sub>1-x</sub>Ge<sub>x</sub> vs. inversed growth temperatures. Si growth parameters include a gas flow of 26 sccm DCS and 3 lpm H<sub>2</sub> at a pressure of 6 torr. GeH<sub>4</sub> (0.8 vol.% in H<sub>2</sub>) is added for Si<sub>1-x</sub>Ge<sub>x</sub> growth <sup>[14]</sup>.

At Princeton, high-quality <100> Si and <100> SiGe epi-layers have been grown on <100> Si substrates by rapid thermal chemical vapor deposition (RTCVD) <sup>[12,13]</sup>. The reactor setup is described in Dr. Malcolm Carroll's Ph.D. thesis <sup>[13]</sup>. Typical growth conditions of epi-Si are: a hydrogen flow rate of 3 lpm, dichlorosilane (DCS) flow of 26 sccm, pressure of 6 torr, and temperature from 700°C to 1000°C. Germane (0.8 vol.% in hydrogen) is introduced to the reactor for Si<sub>1-x</sub>Ge<sub>x</sub> layer growth at a decreased growth temperature of 625 °C. The resulting growth rates are summarized in Fig. 1-2 <sup>[14]</sup>.

#### **1.3 Si-Based Quantum Devices**

To date, Moore's Law has been followed by the semiconductor industry for close to half of a century. It has now reached "90-nm technology" with transistor channel lengths equal to about 50 nm. As the semiconductor device feature size enters the sub-100-nm range, phenomena related to quantum mechanics (wave and particle duality) appear. Quantum effects in ultra-small electronic devices are unavoidable. One kind of quantum effect, which is rooted in the wave nature of the charge carriers, is resonant tunneling and quantum interference. Another is related to the quantized nature of the electronic charge, the so-called single-electron tunneling.

Single-electron devices have attracted much attention, with proposed applications of memory, logic and quantum computing in the future. Their operation relies solely on the Coulomb interaction and the quantized nature of the electron charge. Electrons tunnel in and out of a quantum dot one by one, resulting in conductance oscillations of the transistor with varying gate voltage. In the past decade, people have made extensive studies of quantum dot devices on GaAs/AlGaAs, but little on Si or Si/SiGe, though silicon is the dominant material in the IC industry. Most of the demonstrated Si-based quantum dot devices have a MOSFET structure with a Si/SiO<sub>2</sub> interface. Due to the amorphous nature of SiO<sub>2</sub>, defect states at the Si/SiO<sub>2</sub> interface can trap electrons and act as parasitic extra quantum dots, resulting in undesired electrical characteristics. Eliminating the interface states in Si-based quantum dot devices is the goal of Part II of this thesis. We first developed a low-energy technique of nanopatterning Si/SiGe heterostructures: AFM nano-lithography and selective wet etching. With silicon epitaxial regrowth to passivate the patterned quantum dot device, a SiGe single-hole transistor without Si/SiO<sub>2</sub> interface states has been demonstrated, exhibiting reproducible Coulomb blockade oscillations.

#### **1.4** Thesis Outline

This thesis is divided into two parts.

Part I focuses on improving the quality of solid-phase-crystallized poly-Si thin films and the *a*-Si chemical vapor deposition on a self-assembled opal structure to form a 3-D photonic bandgap. In <u>chapter 2</u>, SPC of *a*-Si is investigated. The electrical characteristics of poly-Si TFTs are significantly dependent on the microstructure of poly-Si: grain-boundaries and intragranular defects. First, using a hydrogen plasma exposure to *a*-Si in a selective small region, we achieved single-grain silicon film at designed locations by subsequent furnace annealing. To reduce the intragranular defect density of crystallized poly-Si films, *a*-Si cantilever structures without underlying silicon oxide were fabricated before SPC, which also enlarged the grain size of poly-Si. <u>Chapter 3</u> presents 3-D silicon PBCs fabricated from self-assembled opals inverted by *a*-Si deposition and subsequent wet etching. Different CVD deposition conditions of *a*-Si have been studied to fill the interstitial space of opals. Optical measurements indicate a near unity reflectance at the wavelength of 1.3  $\mu$ m, indicating that a true photonic bandgap has been achieved.

Part II investigates the fabrication of Si-based quantum-dot devices. <u>Chapter 4</u> outlines the history and development of local anodic oxidation (LAO) by atomic force microscopic (AFM) nanolithography. The instrumentation in our lab for AFM local oxidation is presented. In <u>chapter 5</u>, two methods of nanopatterning Si/SiGe heterostructures by AFM local oxidation are introduced. With AFM nanolithography and selective wet etching, we can electrically isolate a 10-nm-thick SiGe layer. To electrically passivate the pattered SiGe quantum devices, we studied silicon epitaxial regrowth on strained SiGe layers. With pre-baking in hydrogen at a relatively low temperature (800 °C instead of 1000 °C), Si regrowth on strained SiGe layer at 700 °C achieves an interface comparable to that without growth interruption. In <u>chapter 6</u>, we demonstrate a SiGe single-hole transistor fabricated by AFM local oxidation and silicon epitaxial regrowth. The electrical characteristics, Coulomb blockade oscillations, are reproducible over the different measurement scans and at different temperatures, in contrast with those of unpassivated SiGe quantum-dot devices.

Finally in chapter 7, we summarize our contributions.

7

#### References

<sup>1</sup> B. Donlan and D. Pricer, "Pushing the limits: looking forward...looking back", *Microelectronic Design*, **Vol. 1** (1987). <a href="http://www.icknowledge.com/history/history.html">http://www.icknowledge.com/history/history.html</a>.

<sup>2</sup> R. Chau, B. Doyle, M. Doczy, S. Datta, S. Hareland, B. Jin, J. Kavalieros, and M. Metz, "Silicon nanotransistors and breaking the 10nm physical gate length barrier", *Device Research Conference*, Salt Lake City, June (2003). <a href="http://www.intel.com/research/silicon"></a>

<sup>3</sup> http://www.compoundsemiconductor.net.

<sup>4</sup> J. C. Sturm and H. Yin, "Si/SiGe/Si heterojunction bipolar transistors", in Properties of Silicon Germanium and SiGe:Carbon, edited by E. Kasper and K. Lyutovich, p. 305-318, INSPEC Publication, 2000.

<sup>5</sup> K. Rim, J. L. Hoyt, J. Gibbons, "Fabrication and analysis of deep submicron strained-Si n-MOSFET's", *IEEE Trans. Electron Devices*, **47**: 1406-1415 (2000).

<sup>6</sup> J. Virginia, "The future looks bight for LCD TV", *Information Display*, **19**: 10-14 (2003).

<sup>7</sup> Y. A. Vlasov, X.-Z. Bo, J. C. Sturm, D. J. Norris, "On chip assembly of silicon photonic bandgap crystals", *Nature*, **414**: 289-293 (2001).

<sup>8</sup> M. Ino, J. Miyano, H. Kurogi, Y. Nagatomo, and M. Yoshimaru, "Rugged surface polycrystalline silicon film deposition and its application in a stacked dynamic random access memory capacitor electrode", *J. Vac. Sci. Techn. B*, **14**: 751-756 (1996).

<sup>9</sup> A. Kohno, T. Sameshima, N. Sano, M. Sekiya, and M. Hara, "High performance poly-Si TFTs fabricated using pulsed laser annealing and remote plasma CVD with low temperature processing", *IEEE Transactions on Electron Devices*, **42**: 251-256 (1995).

<sup>10</sup> J. Dismukes, L. Ekstrom, and R. Paff, "Lattice parameter + density in germanium-silicon alloys", *J. Phys. Chem.*, **68**: 3021 (1964).

<sup>11</sup> C. Van de Walle and R. Martin, "Theoretical calculations of heterojunction discontinuities in the Si/Ge system", *Phys. Rev. B*, **34**: 5621-5634 (1986).

<sup>12</sup> J. C. Sturm, P. V. Schwartz, E. J. Prinz, and H. Manoharan, "Growth of Si<sub>1-x</sub>Ge<sub>x</sub> by rapid thermal chemical vapor deposition and application to heterojunction bipolar transistors", *J. Vac. Sci. Tech. B*, **9**: 2011-2016 (1991).

<sup>13</sup> J. C. Sturm, H. Manoharan, L. Lenchyshyn, M. Thewalt, N. Rowell, J. P. Noel, and D. Houghton, "Well-resolved band-edge luminescence of exitons confined in strained  $Si_{1-x}Ge_x$  quantum wells", *Phys. Rev. Lett.*, **66**: 1362-1365 (1991).

<sup>14</sup> M. S. Carroll, "The interaction of silicon self-interstitials and substitutional carbon in silicon based heterostructures", Ph.D. thesis, Princeton University, June 2001.

# SOLID PHASE CRYSTALLIZATION OF AMORPHOUS SILICON

#### 2.1 Introduction

Amorphous Si (*a*-Si) and poly-Si TFTs are widely used in active matrix liquid crystal displays (AMLCDs)<sup>[1]</sup>. They are used because they can be made on glass substrates, which are clear to visible light required for displays. Amorphous silicon is in more widespread use, but poly-Si is of increasing interest due to its high mobility. Recently, *a*-Si and poly-Si TFTs have been used for active matrix addressing for organic light emitting diode (OLED) displays <sup>[2,3]</sup>. In this chapter, we study the solid-phase crystallization of *a*-Si to poly-Si.

#### 2.1.1 Why Poly-Si TFTs?

Current AMLCDs are based on *a*-Si TFT technology. A-Si TFTs are used to achieve ON/OFF switching of each image pixel. Hydrogenated *a*-Si can be deposited directly on glass substrates by CVD. The low process cost and low OFF current makes *a*-Si TFTs dominant in active-matrix addressing of displays. However, compared with *a*-Si TFTs, poly-Si TFTs have a higher electron field-effect mobility ( $\sim 10 - 300$  cm<sup>2</sup>/Vs). Furthermore, no p-channel device is available in *a*-Si, so CMOS circuits require poly-Si. In active-matrix circuits, the higher carrier mobility of poly-Si TFTs results in a smaller transistor size than *a*-Si TFTs for same ON current. This will

increase the display aspect ratio between the optical windows and the total pixel size, and thus reduce the power consumption or increase the display resolution. In addition, p-channel poly-Si TFTs can provide electronic circuits to control OLED operation <sup>[4]</sup>.

Poly-Si could also be used to integrate the driver circuits for the active-matrix arrays. Drivers are difficult to fabricate from *a*-Si TFTs because of the low electron mobility and the extremely low mobility in p-channel transistor in *a*-Si. Usually, drivers are made of c-Si circuits, which are then bonded to the matrix-addressing array. This is the primary cost of electronics for AMLCDs. To reduce the cost, one can develop TFT active-matrix displays with fully integrated poly-Si driver circuits <sup>[5,6]</sup>.

#### 2.1.2 Solid-Phase Crystallization of *a*-Si

As described in Sec. 1.2.1, poly-Si can be obtained by direct deposition or by crystallization of *a*-Si. Due to the smoother surface and larger grain size of crystallized poly-Si, the crystallization of *a*-Si has attracted more interest. Solid-phase crystallization (SPC) of *a*-Si, accomplished by furnace annealing, produces highly uniform poly-Si films over large areas, and is a proven batch process. Because the strain points of affordable glass substrates lie near 600 °C, crystallization and further processing are restricted to temperatures at or below ~ 600 °C. However, the full crystallization of *a*-Si by furnace annealing at 600 °C historically has required a long anneal time, on the order of 20-60 hr <sup>[7]</sup>.

Solid-phase crystallization involves two steps: nucleation and grain growth. During nucleation, silicon atoms rearrange themselves from a disordered to an ordered state, forming small crystalline clusters. The crystal cluster spontaneously grows until it reaches a critical size. The critical size of crystal clusters has been estimated to be around 2-4 nm at a temperature of 650 °C <sup>[8]</sup>. Once the critical size is reached, grain growth will start. The grain growth mechanism is very similar to solid phase epitaxy (SPE). Since the activation energy of nucleation is ~ 4.9 eV <sup>[9]</sup>, greater than that of grain growth 2.3-2.7 eV <sup>[10-11-12]</sup>, the crystallization rate at low temperatures is primarily limited by the nucleation step. To reduce the crystallization time, various techniques

10

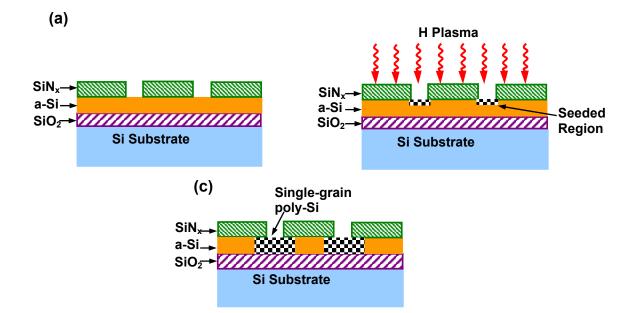

have been used to create crystalline "seeds" in an *a*-Si matrix to enhance the nucleation. They include metal-induced crystallization <sup>[13,14]</sup>, germanium-induced crystallization <sup>[15]</sup>, and plasma-induced crystallization <sup>[16,17]</sup>. For example, the hydrogen plasma treatment of *a*-Si enhances SPC by reducing the crystallization time from 20 hr to 4 hr at 600 °C <sup>[17]</sup>. In this chapter, we will show that a single nucleus is formed by exposing a hydrogen plasma to a small area of the *a*-Si film, leading to single-grain silicon films at a designed location, as opposed to a random one <sup>[18]</sup>.

#### 2.1.3 Fabrication of Polysilicon TFTs

P-channel poly-Si has been fabricated with the process flow shown in Fig. 2-1. Ultimate applications would be on glass, but our experiments were done on  $SiO_2$  on Si substrates for compatibility with the process lab. First, a 150-nm-thick *a*-Si film is deposited on an oxidized Si substrate at 150 °C by plasma enhanced chemical vapor

**Figure 2-2.** Electrical characteristics of (a) drain current *vs.* gate voltage and (b) drain current *vs.* drain voltage for p-channel TFTs.

deposition (PECVD). The deposition recipe is shown in Appendix A. Then, *a*-Si film is fully crystallized at 600 °C by furnace annealing for 20 hr, and subsequently patterned into active islands by optical lithography and reactive ion etching (RIE). The gate oxide (~ 130 nm) is deposited at 250 °C by PECVD, followed by a 250-nm-thick *a*-Si deposition for the gate. After gate patterning, source/drain and gate are ion implanted by boron (B<sup>+</sup>) with a dose of  $2 \times 10^{15}$  cm<sup>-2</sup> and energy of 35 keV. The dopants were activated by furnace anneal at 600 °C for 20 hr. RF hydrogenation at a temperature of 350 °C and power of 0.6 W/cm<sup>2</sup> was then performed in the PECVD chamber in order to passivate the silicon dangling bonds at poly-Si grain boundaries <sup>[19]</sup>. After hydrogenation, a 250-nm-thick passivation oxide is deposited, followed by contact hole opening in the oxide. Finally, aluminum was thermally evaporated and then patterned by optical lithography and wet etching. The sample was annealed in forming gas (mixture of 10% H<sub>2</sub> in N<sub>2</sub>) at ~ 250 °C for 90 s in a rapid thermal annealer. The whole fabrication process has been optimized, with details given in Ref. [20].

| 1000°C thermal oxide.             |       |        |                 |        |  |

|-----------------------------------|-------|--------|-----------------|--------|--|

|                                   | N-MC  | SFET   | <b>P-MOSFET</b> |        |  |

| <b>Electrical Characteristics</b> | 250°C | 1000°C | 250°C           | 1000°C |  |

| Electrical Characteristics        | DECUD |        | DECUD           |        |  |

**Table 2-1.** Electrical characteristics of polycrystalline silicon n-channel and pchannel TFTs ( $W/L = 50 \mu m/2 \mu m$ ) with gate oxides of 250°C PECVD oxide and 1000°C thermal oxide.

| Electrical Characteristics               | N-NIOSF E I         |                   | P-MOSFEI            |                   |

|------------------------------------------|---------------------|-------------------|---------------------|-------------------|

|                                          | 250°С               | 1000°C            | 250°C               | 1000°C            |

|                                          | PECVD               | thermal           | PECVD               | thermal           |

|                                          | oxide               | oxide             | oxide               | oxide             |

| μ <sub>field</sub> (cm <sup>2</sup> /Vs) | 38                  | 110               | 19.2                | 75.6              |

| $V_{th}$ (V)                             | 0.8                 | 0.1               | -11.8               | -2.8              |

| Subthreshold Slope (V/Dec)               | 1.6                 | 0.5               | 1.4                 | 0.4               |

| Ion/Ioff                                 | $> 1 \times 10^{6}$ | 1×10 <sup>7</sup> | $> 1 \times 10^{6}$ | 1×10 <sup>7</sup> |

The electrical characteristics of the TFTs are well behaved. Typical characteristics of drain current *vs.* gate voltage and drain current *vs.* drain voltage are shown in Fig. 2-2(a) and (b) respectively. TFTs with channel length from 2  $\mu$ m to 50  $\mu$ m were fabricated, showing results with field-effect mobilities of 10-20 cm<sup>2</sup>/Vs, subthreshold slopes of 1.2-2 V/Dec., and ON/OFF current ratios of 10<sup>6</sup>-10<sup>7</sup>.

TFTs with a thermal gate oxide grown at 1000 °C were also fabricated. The oxide thickness was ~ 35 nm. The electrical characteristics of TFTs are summarized in Table 2-1, including n-channel TFTs from Ref. [20] by a similar process (prior work in our lab). It is not surprising that n-channel TFTs have slightly higher field-effect mobilities than p-channel TFTs. However, TFTs with a high-temperature thermal gate oxide have much higher field effect mobilities than those with low-temperature PECVD gate oxide. This may be attributed to the low density of interface states between the thermal oxide and poly-Si, or to the decreasing of the intragranular defect density in poly-Si grains during high temperature annealing<sup>[21]</sup>. The high-temperature process is not fit for glass substrates with strain point of ~ 600 °C. A method to reduce the intragranular defect density of SPC poly-Si films with process temperatures not greater than 600 °C is required, and will be studied in Sec. 2.3.

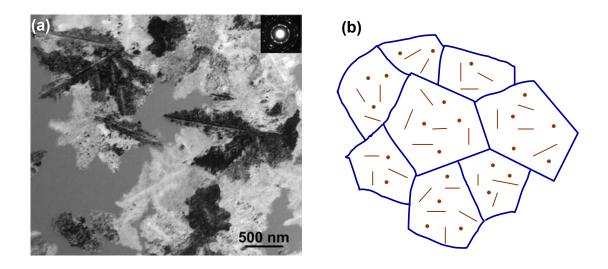

#### 2.1.4 Microstructure of SPC Polysilicon

Compared with the electron and hole mobilities of *c*-Si transistors, for example,  $\sim 700 \text{ cm}^2/\text{Vs}$  for electrons and  $\sim 250 \text{ cm}^2/\text{Vs}$  for holes in silicon-on-insulator (SOI) MOSFETs <sup>[22]</sup>, the carrier mobilities in the above poly-Si TFTs are much smaller. Figure 2-3(a) shows the microstructure of poly-Si films under TEM. The difference between c-Si and SPC poly-Si is that SPC poly-Si contains many grain boundaries and intragranular defects, as indicated in Fig. 2-3(b).

**Figure 2-3.** (a) TEM observation of polysilicon film after anneal at 600 °C for 16 hr without hydrogen plasma treatment (control sample) shows grain size  $0.3-0.8 \mu m$ . Inset is the diffraction pattern. (b) Schematic of poly-Si microstructure composed of grain boundaries and intragranular defects.

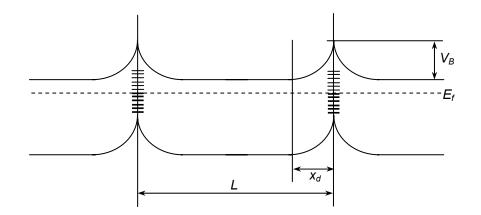

**Figure 2-4.** Potential barriers in poly-Si, which are due to the charge trapping at the grain boundaries <sup>[23]</sup>.

In poly-Si, defects at grain boundaries are trapping centers. Free carriers are trapped at the grain boundaries, forming depletion regions and leading to energy band curvature (see Fig. 2-4 <sup>[23]</sup>). The resulting potential barriers at the grain boundaries will make it difficult for carriers to cross grain boundaries, which results in low field-effect mobilities. Furthermore, it has been reported that intragranular defects, such as micro-twins and dislocations, exist in SPC poly-Si <sup>[21,24]</sup>, as seen in Fig. 2-3(a). They can also trap carriers and decrease the mobilities of poly-Si TFTs. Therefore, to improve the poly-Si TFTs, the number of grain boundaries and intragranular defects in the transport channel of TFTs should be reduced. This is our goal for this research.

## 2.2 Single-Grain Silicon Film at Designed Locations

#### 2.2.1 Motivation

The electrical characteristics of polysilicon TFTs are strongly dependent on the polysilicon microstructure. Grain boundaries are scattering centers which decrease carrier mobility and also serve as midgap states to increase leakage current. To improve the performance of polysilicon TFTs, one would want to locate the TFTs within a single grain of the polysilicon between grain boundaries. Therefore, it is of great interest to control the location of single grain regions <sup>[25,26,18,27,28]</sup>.

The solid-phase crystallization (SPC) of amorphous silicon involves two steps, *i.e.* nucleation and growth. A single nucleus induced during the nucleation stage is the prerequisite for the formation of a single-grain island. To date, several methods have been demonstrated to enhance the nucleation of *a*-Si:H SPC, such as metal-induced SPC <sup>[13,14]</sup>, germanium-induced SPC <sup>[15]</sup>, and plasma-induced SPC <sup>[16,17]</sup>. Although the original motivation of these methods was to reduce the thermal budget of SPC, they can be used to induce a single nucleus and increase grain size by lateral growth from seeding sites into the amorphous matrix. The formation of single-grain islands at designed locations has been reported by methods of silicon ion implantation <sup>[25]</sup> and nickel-induced crystallization <sup>[26-28]</sup>. Single-grain silicon islands by plasma seeding

16

have not been reported. Compared with the seeding by ion implantation and metals, plasma-induced SPC has possible advantages of low metal contamination and less radiation damage.

#### 2.2.2 Experimental Details

It has been reported that a hydrogen plasma treatment (HPT) of amorphous silicon films at room temperature enhances the rate of SPC, and thus can reduce the crystallization time from 20 hr to 4 hr at 600 °C <sup>[17]</sup>. Surprisingly, the hydrogen plasma actively abstracts hydrogen from the amorphous silicon and creates seed nuclei in the top 30 nm of the film. This process can be spatially masked by covering the surface of *a*-Si: H with a silicon nitride film and then opening holes in the nitride where the hydrogen seeding process will occur. There is no accelerated crystallization under the nitride films.

Figure 2-5 shows the experimental steps for the formation of single-grain islands. First, 100-nm-thick amorphous silicon was deposited on an oxidized silicon substrate at 150°C with RF power of 18 mW/cm<sup>2</sup> by PECVD. During deposition, the flow rate of silane is 50 sccm and pressure stabilizes at 500 mtorr. The hydrogen concentration is ~ 17 % (atomic) in the amorphous silicon. Silicon nitride with 200-nm-thickness was then deposited by PECVD at 200 °C, which has been demonstrated not to reduce the hydrogen concentration in a-Si:H <sup>[29]</sup> and has little effect on the hydrogen-plasma enhancement of SPC. Holes with diameters from 0.4 µm to 1.8 µm were opened in the silicon nitride film by electron-beam lithography and dry etching. The samples were then exposed to a hydrogen plasma in a parallel-plate reactive ion etcher (RIE) at the optimum condition with an RF power of 0.8 W/cm<sup>2</sup>, hydrogen flow rate of 50 sccm, and pressure of 50 mtorr <sup>[17]</sup>. The low pressure and high power are designed to give a high hydrogen ion energy. Finally, the nitride films were removed by wet etching and the samples were annealed at 600 °C in nitrogen. The crystallinity of the silicon film was monitored by ultraviolet reflectance ( $\lambda$ =276 nm).

**Figure 2-6.** TEM sample preparation: (a) active island patterning, (b) film lift off by selective wet etching, and (c) film after pick-up with a copper grid.

Samples for transmission electron microscope (TEM) observation were prepared by a lift-off process, as indicated in Fig. 2-6<sup>[30]</sup>. Silicon films, first pattered into  $1 \times 1$ mm<sup>2</sup> islands, were lifted off from the oxidized silicon substrate by an HF solution. The peeled-off films were placed onto copper grids for TEM observation. The grain size is characterized by an effective diameter  $d = \sqrt{4A/\pi}$ , where A is the grain area. TEM observations were performed in the Princeton Materials Institute. High-resolution lattice images were under assistance of Dr. Nan Yao.

## 2.2.3 Results and Discussion

**Figure 2-7.** SEM (a & c) and TEM (b & d) micrographs of lateral growth from the nucleation sites induced by hydrogen plasma treatment after 600 °C annealing for (a) (b) 6 hr and (c) (d) 10 hr.

TEM observations on polysilicon films without hydrogen plasma treatment (HPT) are shown in Fig. 2-3(a). The grains locate randomly on the film with a size of  $0.3 - 0.8 \mu m$ . Fig. 2-7 shows the selective crystallization and lateral growth through

scanning electron microscope (SEM) and TEM for samples with large seeding holes (~3  $\mu$ m) which were annealed for (a) (b) 6 hr and (c) (d) 10 hr. The dark areas in the Fig. 2-7 (a) and (c) are fully crystallized polysilicon, but the white areas are still amorphous, which has been confirmed by UV reflectance. The films in the holes seeded by the hydrogen plasma are not only completely crystallized, but also laterally grow outward to the surrounding amorphous matrix with a lateral growth rate of 0.5  $\mu$ m/hr. Comparing TEM observations between Fig. 2-7(b) and Fig. 2-7(d), we can see no grains formed in the area without HPT (control area) until the anneal time increases to 10 hr. The grain size at the control area of Fig. 2-7(d) is ~ 0.4  $\mu$ m (indicated by an arrow), in contrast with the grain size of ~ 2.5  $\mu$ m in the area which nucleated from the HPT hole and laterally grew outward of the hole. This result shows that the nucleation site can be controlled by selective exposure to the hydrogen plasma, and lateral growth from this site will increase the grain size.

**Figure 2-8.** The relationship between the number of nuclei and the hole size, after hydrogen plasma treatment and annealing at 600 °C for 3 hr <sup>[18]</sup>.

Multiple polysilicon grains were also observed by TEM in a hole with a 1.0- $\mu$ mdiameter annealed at 600 °C for 5 hr. Although the crystallization occurs only within the hole region exposed to the hydrogen plasma, multiple grains are formed, presumably resulting from multiple nucleation sites within the hole. To reduce the number of nuclei, holes with diameters from 0.4  $\mu$ m to 1.8  $\mu$ m were opened in silicon nitride prior to the HPT. After annealing for 3 hr at 600 °C, the number of grains in the holes was counted under the TEM (Fig. 2-8). When the hole diameter is greater than 0.8  $\mu$ m, multiple grains exist in the exposed hole; when the hole diameter is between 0.6  $\mu$ m and 0.8  $\mu$ m, single or multiple grains are observed in the hole. When the hole diameter is less than 0.6  $\mu$ m, a single grain island is formed. In the silicon ion implantation approach <sup>[25]</sup>, the minimum hole size needed to produce single grain is ~ 0.66  $\mu$ m, which is close to our result.

**Figure 2-9.** TEM micrograph of a single nucleus in a hole with a diameter of  $0.55\mu$ m, induced by hydrogen-plasma exposure and then annealing at 600 °C for (a) 3.0 hr, (b) 8.0 hr, and (c) the SADP of the grain of (b).

Figure 2-9(a) shows a single grain within a 0.55  $\mu$ m diameter hole after annealing for 3 hr, with approximate dimensions of 0.13  $\mu$ m × 0.4  $\mu$ m. No other grains exist either in the hole or outside of the hole. For longer anneals (8hr, Fig. 2-9b), the grain grows laterally outside of the seeding hole to the amorphous matrix, with the grain size increasing to ~ 0.25  $\mu$ m × 0.8  $\mu$ m. The grain size can be as large as 2.5  $\mu$ m after a 16 hr anneal, which is large enough for TFT fabrication. We did not make TFTs in such grains. However, it is a promising direction for future work. The selective area diffraction pattern (SADP) (Fig. 2-9c) of the silicon grain of Fig. 2-9(b) confirms the single crystalline nature of the grain. The zone axis of the SADP is the [112] of a facecentered-cubic crystalline structure. The grains are not defect-free, however, and the intra-grain defects appear by TEM to be similar to those in other polycrystalline silicon films formed by low temperature crystallization of amorphous silicon.

## 2.3 Polysilicon Films with Large Grain Size and Low Intragranular Defect Density by Removal of Underlying Oxide

#### 2.3.1 Introduction

As we mentioned above, the electrical characteristics of polysilicon TFTs are strongly dependent on the polysilicon microstructure. Grain boundaries and intragranular defects form electrical potential barriers and impede the carrier transport of poly-Si TFTs. Polysilicon films with larger grain sizes and fewer intragranular defects have been a continual goal <sup>[31,32,33,34]</sup>. Recent low-temperature ( $\leq 600$  °C) SPC techniques can achieve a grain size as large as 3.0 microns deposited by disilane gas <sup>[31]</sup>. TFTs made with channel lengths smaller than the grain size still have a mobility only on the order of 100 cm<sup>2</sup>/Vs, even though there should be no grain boundaries within the channel. However, the residual intragranular defects reduce the defect-free area of polysilicon film down to 30 nm, and it is thought that they become the limiting factor in device performance <sup>[7]</sup>. Therefore, reducing the density of intragranular defects becomes very important to improve the electrical performance of TFTs.

To date, two methods have been suggested to reduce the density of intragranular defects: high-temperature annealing <sup>[21,35]</sup> and laser crystallization <sup>[36]</sup>. Haji *et al* <sup>[21]</sup> reported that the main intragranular defects in polysilicon films after crystallization at 600 °C are microtwins, and that they are not stable above 750 °C, so they can be eliminated with further high-temperature annealing. However, high-temperature processing cannot be applied to AMLCD TFTs fabricated on glass substrates with a strain point less than 650 °C. Compared with the furnace annealing, laser crystallization has disadvantages of high-cost and poor film uniformity. Reducing this intragranular defect density of SPC polysilicon films at a temperature below 650°C is a motivating factor for this research. In this work, a free-standing cantilever of amorphous silicon film without underlying silicon dioxide was fabricated. The absence of underlying oxide is found to decrease the intragranular defect density and increase the grain size <sup>[37]</sup>.

#### 2.3.2 Experimental Details