CompArch 08/20/08

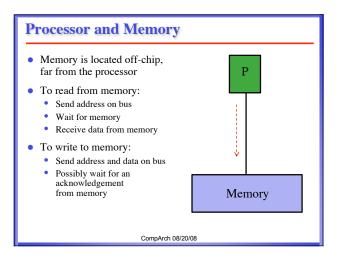

Р

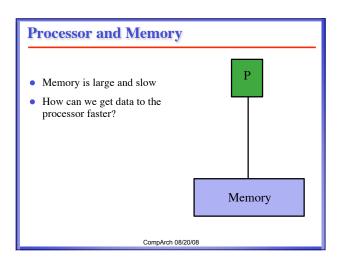

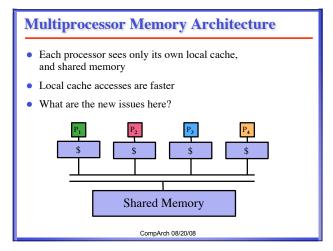

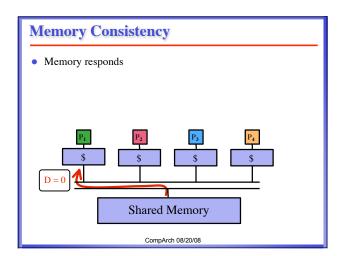

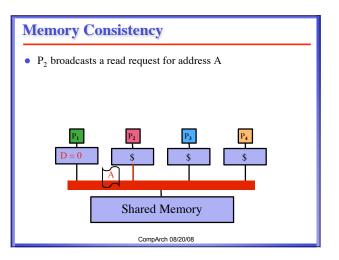

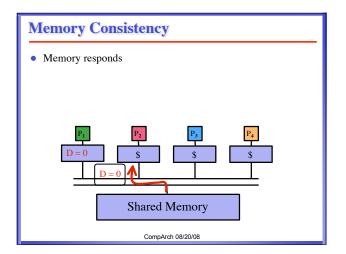

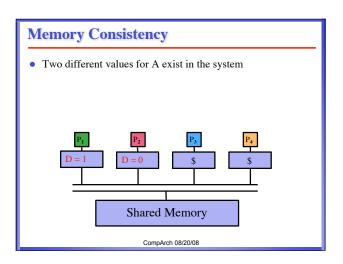

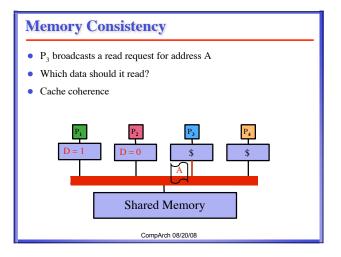

# Multiprocessor Memory Architecture Processors connected to shared memory via a shared bus All processors see all memory activity Memory is large and slow How can we get data to the processor faster? Pa Pa Pa Pa Pa Memory Shared Memory Comparch 08/20/08

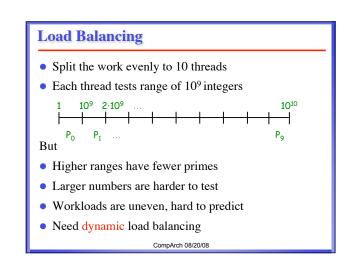

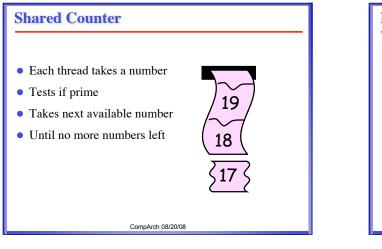

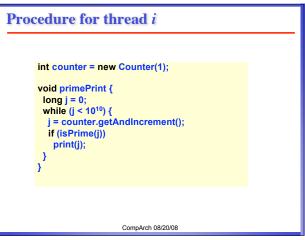

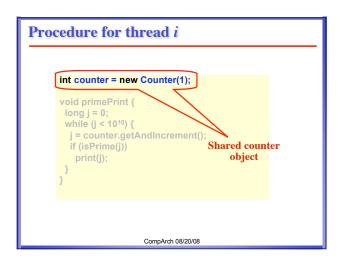

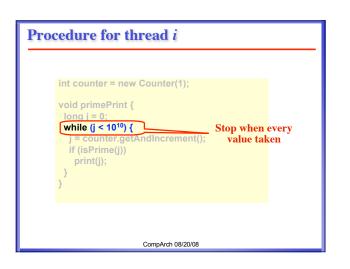

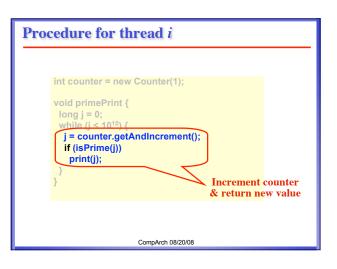

# Prime Number Example

- <u>Task</u>: Print primes from 1 to 10<sup>10</sup>

<u>Hardware</u>:

- Ten-processor CMP One thread per processor

- <u>Goal</u>: Close to maximum possible speedup Ten fold speedup over uniprocessor (?)

Example adopted from "Art of Multiprocessor Programmin CompArch 08/20/08 Herlihy-Shavit

# **Parallel Programming for Performance**

- Load balancing

- Reduce idle time when threads wait

- Maximize parallel portion of code

- Minimize sequential parts

- Small critical sections

- Fine-grained synchronization

CompArch 08/20/08

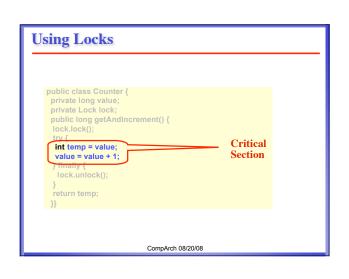

## **Disadvantages of Locks**

### • Coarse-grain

- High contention (on the lock)

- Low throughput

- Fine-grain

- Difficult to program and debug

- Deadlock, interrupt

- Spin-locks repetitive accesses until free

- Many memory accesses

- Useless work

- Alternatives: blocking, queue locks

CompArch 08/20/08

| Fransactional Memory                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Lock-free synchronization                                                                                                              |

| Transaction: Atomic section $lock() \rightarrow unlock()$                                                                              |

| <ul> <li>Speculative execution – optimistic</li> <li>No conflicts → commit</li> <li>Conflicts detected → roll back, reissue</li> </ul> |

| <ul> <li>Hardware requirements</li> <li>Additional memory or dedicated cache</li> <li>Changes to cache coherence protocol</li> </ul>   |

| • May also be implemented in software                                                                                                  |

| CompArch 08/20/08                                                                                                                      |

# Parallel Programming

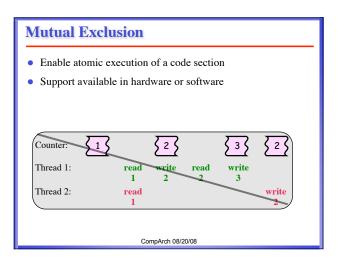

- Parallelize as much of the code as possible

- Minimize sequential parts

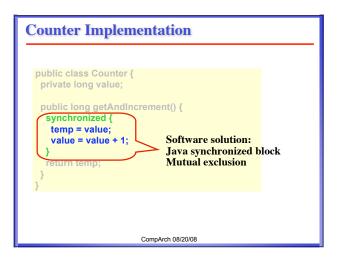

- Be careful with mutual exclusion

- Requires waiting

- Different approaches

- Each has its advantages

CompArch 08/20/08

CompArch 08/20/08