### Power in Microprocessor Designs

**Mandy Pant**

**MMDC, Intel**

Email: mondira.pant@intel.com

# First.... Who Am I ?

### Until a few years ago ..

# Emphasis had been **solely** on improving performance

21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

## **Times have changed**

No longer sole emphasis on performance ....

# Power & reliability concerns have become huge !!

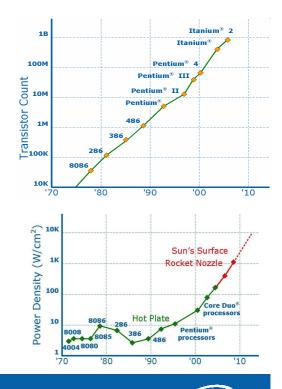

### **Technology Trends: Moore's Law**

- More and faster transistors with higher power demands

- Gate delay ↓30% every process generation (2 years)

- Area of a transistor roughly scales by 50% per generation

- Transistor density doubling

- Power density increasing

5 21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

# **Technology Trends**

Traditional cooling solutions reaching physical limits

http://www.phys.ncku.edu.tw/~htsu/humor/fry\_egg.html

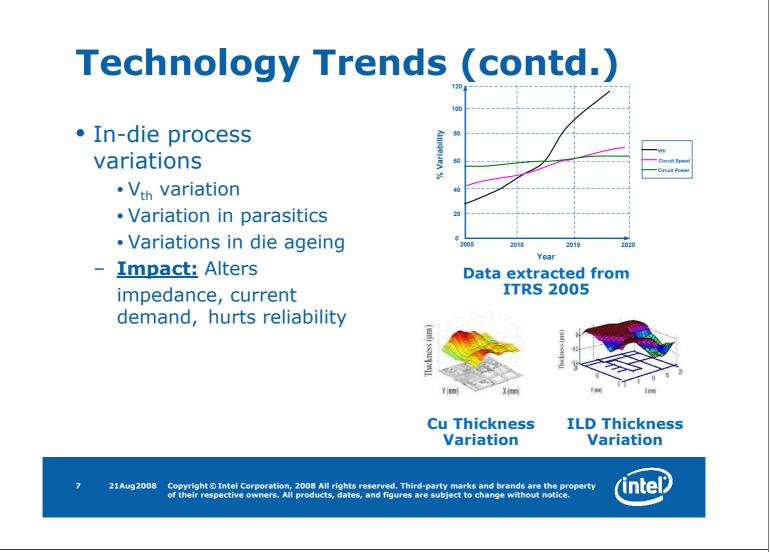

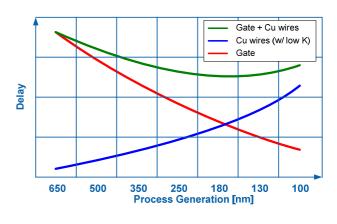

# **Technology Trends (contd.)**

- Delay Trends

- ➡ Gate delay, Wire delay

- Cross-chip communication

#### Performance demands continue

Wire & gate delay trends

## **Technology Trends (contd.)**

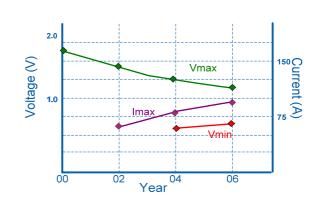

- Intel's "Right Hand Turn"

- Power is \$\$

- "Power Wall" driving reduction in voltage

- Dynamic power =  $\alpha C V^2$ F

- V<sub>MIN</sub> relatively constant

- – Operating range

- Noise margins

9 21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

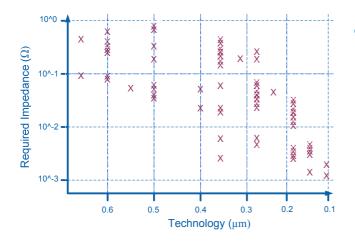

## **Technology Trends (contd.)**

#### **Impedance Rqmts. For High Performance MicroProcessors**

ISTR RoadMap July 31st 2007

- Impedance scaling:

- Drastic drop in supply impedance

- Even at constant power

- Vdd 🖊, Imax 🕇

- → |Zrequired| ↓ ↓

- Today's chips: |Zrequired|

≈1 mΩ

- Supply voltage becoming noisy as result

(intel.

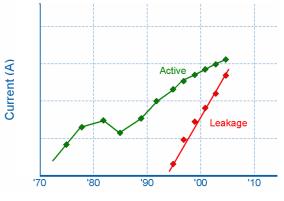

# **Technology Trends (contd.)**

#### Leakage power

- Increasing

- Constant demand on power delivery system

- Reliability impact

#### Leakage & Active Current Trends

#### **Challenge:** Efficient power delivery while:

- Minimizing power consumption

- Optimizing heat dissipation

11 21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

### (intel)

# **Some Other Trends**

#### Economy

- Electronic device presence multiplying

- Energy consumption increasing

- Energy costs rising

- We all have an electricity bill to pay at the end of the month

#### Sociology & environment

• Global warming awareness

### What exactly is Power & Energy ?

Power

- Rate at which work is done, expressed as amount of work per unit of time in Watts

- In a microprocessor:

- Power consumed = dynamic power + leakage power

- P = (Pswitch + Psc + Pcont + Pglitch) + Pleak

- $P = (\alpha C V^2 F + Psc + Pcont + Pglitch) + VI_{leak}$  $\alpha$  activity factor V power supply voltage F clock frequency

- C switching capacitance

- Vt threshold voltage

- $I_{loak} \sim exp(-qVt/kT)$  leakage current

Energy

- Total amount of work done expresses in Joules

- Power \* Time = Energy

Which one do we aim at lowering: Energy or Power or BOTH?

21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice. 13

# **Current Design Solutions**

- Multiple voltage domains on-die

- Trick used to reduce power while maintaining performance

- Cache voltage lower than core/uncore voltage

- Cache mainly needs to hold state

- Speed critical for execution units, overall communication etc  $\rightarrow$  leads to higher voltage requirements here

- Impact

- Overall grid metal available per domain reduced

- May need to compromise grid requirements depending upon distribution of voltage domains

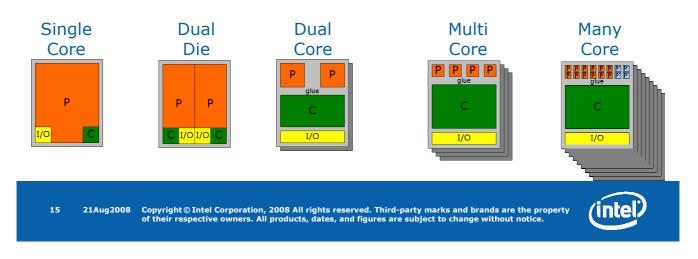

# **Current Design Solutions**

- Multi-core trend

- Attractive for throughput based solutions

- Enables reduction in power consumption while maintaining throughput

- Dynamic power =  $CV^2F$

- Power = 1Core @ V,F ~ 2 Cores @ 0.8V,0.8F

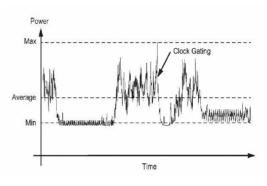

# **Current Design Solutions**

- Active power management techniques

- V/f scaling

- Multiple operating modes for various benchmarks

- Clock gating & power down mechanisms

- ➡ Higher I<sub>STEP</sub> (I<sub>MAX</sub> I<sub>MIN</sub>)

- Power gates

#### SUN Microsystems CPU Sample Current Profile

Source: Harris, Addison-Wesley '05

# Is it sufficient ?

21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

17

## 2015 Likely Scenario

# 5 Billion Connected People Always On In Pursuit of Killer "Experiences"

Network Capacity? 100 Tbits/sec Today. 100,000 Tbits/sec Needed. That is **1000x** Increase!

**inte**

# That's a lot of power!

19 21Aug2008 Copyright © Intel Corporation, 2008 All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are subject to change without notice.

### **Summary**

- Technology trends in nano-era have elevated our power and reliability challenges

- Call for action: We need to be able to develop easy and revolutionary techniques to counter this in the increasing world of complicated microprocessor design

- Plenty exist....but not sufficient

- Plenty of opportunities for research

Talk to/email me for further input/questions **Email: mondira.pant@intel.com**