## Oxide TFT LC Oscillators on Glass and Plastic for Wireless Functions in Large-Area Flexible Electronic Systems

Yasmin Afsar\*, Jenny Tang\*\*, Warren Rieutort-Louis\*, Liechao Huang\*, Yingzhe Hu\*,

Josue Sanz-Robinson\*, Sigurd Wagner\*, Naveen Verma\*, and James C. Sturm\*

\*Department of Electrical Engineering, Princeton University, Princeton NJ, USA

\*\*Department of Chemical and Biological Engineering, Princeton University, Princeton NJ, USA

#### Abstract

High-frequency signals have important applications in large-area hybrid systems, enabling efficient wireless transmission of power and information. We report zinc-oxide thin-film transistor (ZnO TFT) cross-coupled LC oscillator circuits on glass and 3.5-µm-thick polyimide substrates that achieve oscillation frequencies as high as 35 MHz and 17 MHz, respectively. The TFTs are designed for high unity power-gain frequency  $f_{MAX}$  by minimizing gate resistance and device capacitances. In a resonant oscillator topology, this enables oscillation well above the cutoff frequency  $f_T$  of the TFTs. Oscillators on plastic benefit from the improved dimensional stability of spin-cast ultrathin substrates, which allows TFTs on these substrates to have gate resistances and device capacitances comparable to TFTs on glass.

## **Author Keywords**

Oxide thin-film transistor (TFT); zinc oxide; plasma-enhanced atomic layer deposition (PEALD); cutoff frequency  $(f_T)$ ; unity power gain frequency  $(f_{MAX})$ ; TFT circuits; thin-film/CMOS hybrid systems; flexible electronics; large area electronics (LAE).

## 1. Objective and Background

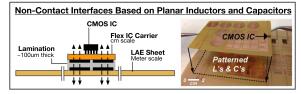

Large-area electronics (LAE) offers unprecedented capabilities as a technology for sensing. This is because its characteristic lowtemperature processing enables compatibility with a variety of flexible substrates and materials for forming diverse transducers. While a broad set of sensors have been demonstrated [1-4], creating full sensing systems with exclusively low-temperature compatible components remains challenging. Full LAE sensing systems can be achieved effectively with a hybrid approach in which silicon-CMOS ICs are coupled with LAE components (TFT circuits, large-area passive inductors and capacitors, thinfilm solar cells, sensors) [5]. In these systems, we avoid complex challenges of monolithic system integration by fabricating different large-area components on separate polyimide sheets and laminating them together into a single flexible unit. Lamination is made possible by the use of non-contact interfaces for wireless data and power transfer between the sheets, as in Figure 1.

**Figure 1.** Cross section (left) and photo (right) of non-contact interfaces in LAE hybrid systems [5].

Generation of high-frequency signals (> 10 MHz) enables improved performance and/or power efficiency in inductive noncontact LAE interfaces [6]. For thin-film transistors (TFTs) processed at plastic-compatible temperatures, limited TFT performance makes circuit operation above 10 MHz a significant challenge. We report key advances in this direction: TFT oscillators fabricated at a maximum temperature of 200°C on glass and 3.5-µm-thick polyimide substrates, operating at oscillation frequency  $f_{OSC} = 35$  MHz with a 7 V supply voltage (glass) and  $f_{OSC} = 17$  MHz with a 9 V supply voltage (plastic).

To achieve these results, we:

- 1. Use zinc oxide semiconductor with a mobility of  $\sim 10~\text{cm}^2$  /Vs for the active TFT material, because metal-oxide semiconductors offer higher mobility than  $\alpha$ -Si at temperatures  $\leq 200^{\circ}\text{C}$ .

- 2. Employ a resonant circuit topology and high quality, low-R inductors enabled by large area to build circuits operating above the TFT's cutoff frequency  $f_T = 12.9 \text{ MHz}$ ;

- 3. Design TFTs with low gate resistances (30  $\Omega$ ) and parasitic device capacitances (14 pF), thereby boosting the maximum possible oscillation frequency, i.e. the TFT unity powergain frequency  $f_{MAX}$ , above 35 MHz;

- 4. Use ultrathin spin-coated polyimide substrates, which permit flexible oscillators to oscillate above  $f_T$  because TFT gate resistance and capacitance can be as low as on glass.

To our knowledge, the presented circuits represent the fastest oscillators achieved at fabrication temperatures entirely  $\leq 200^{\circ} \text{C}$  and the fastest oscillators fabricated directly on ultrathin plastic.

## 2. Approach

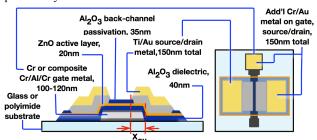

**2.1** ZnO/Al<sub>2</sub>O<sub>3</sub> Fabricated at Plastic-Compatible Temperatures: We build ZnO TFTs on 75 mm X 75 mm substrates, using a plasma-enhanced atomic-layer deposition (PEALD) system based on [7] for depositing the Al<sub>2</sub>O<sub>3</sub> gate dielectric, ZnO active layer, and Al<sub>2</sub>O<sub>3</sub> passivation layer. These three oxide layers are deposited in a single run, without breaking vacuum. The TFT structure is bottom-gate and non-self-aligned. Figure 2 shows the device cross-section and top view and specifies layer thicknesses.

Figure 2. Cross-section and top-view of ZnO TFT.

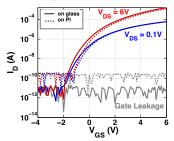

The W/L ratio is 500  $\mu$ m / 5  $\mu$ m, and the gate-source/drain overlap  $X_{OV}$  is 5  $\mu$ m. Although this  $X_{OV}$  value is typical of large-area TFT technology, it imparts a significant overlap capacitance  $C_{OV} = C_{GD} = C_{GS}$ , which will be discussed later. The top view shows that source, drain, and gate pads are capped with an additional 50-nm Cr, 100-nm Au top-metallization layer for low-resistance interconnects between TFTs. In this work, we fabricate TFTs on glass and 3.5- $\mu$ m-thick polyimide substrates. Figure 3 below shows typical ZnO TFT transfer characteristics and Table 1 presents extracted device parameters for TFTs on both substrates.

**Figure 3.** TFT transfer characteristics for  $V_{DS}$  of 0.1 and 6 V for devices on glass (solid) and 3.5- $\mu$ m polyimide (dashed) after delamination.

**Table 1.** TFT parameters on glass and 3.5- $\mu$ m PI substrates. Mobility and threshold voltage are extracted from the saturation portion of the I<sub>D</sub>-V<sub>GS</sub> curve at V<sub>DS</sub> = 6 V.

|                             | Glass    | 3.5µm Pl |

|-----------------------------|----------|----------|

| $\mu$ (cm <sup>2</sup> /Vs) | 13.4±2.0 | 11.3±1.2 |

| $V_T(V)$                    | 2.0±0.4  | 2.2±0.3  |

| $C_{GD}/W$ (fF/ $\mu$ m)    | 10       | 10       |

| $R_{gate}/W (\Omega/\mu m)$ | 0.07     | 0.07     |

| W (µm)                      | 500      | 500      |

| <i>L</i> (µm)               | 5        | 5        |

| <i>X</i> <sub>OV</sub> (μm) | 5        | 5        |

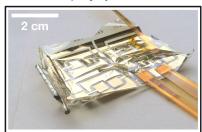

**ZnO TFTs on 3.5μm polyimide:** Because the maximum process temperature is 200°C, TFT fabrication on polyimide is possible with very few alterations compared to processing on glass. To prepare 3.5-μm-thick polyimide foil substrates, a single layer of HD Microsystems PI2611 is spin-coated onto a silicon carrier wafer (as in [8, 9]), cured in a nitrogen environment, and lastly outgassed in a vacuum oven prior to TFT fabrication. Fabrication proceeds directly on the fresh polyimide surface. After processing, these TFTs must be delaminated from the carrier. A border in the polyimide is defined with a razor blade, and the entire film is slowly peeled off the carrier along the direction of channel length. Introducing DI water between the film and the silicon carrier assists in this removal. Fig. 4 shows a photo of a delaminated 3.5μm polyimide foil with ZnO TFTs.

**Figure 4.** ZnO TFTs on 3.5-µm-thick polyimide delaminated from silicon carrier. Flexible laminated connectors to offsheet inductors also shown.

Because the carrier wafer prevents the polyimide from expanding during fabrication, the TFT dimensions (W, L,  $X_{OV}$ ) on

glass can also be used on plastic ( $X_{OV}$  must be made  $\sim 3X$  larger when fabricating TFTs on freestanding polyimide substrates [10]). I-V transfer curves for ZnO TFTs on plastic are overlaid on Figure 3, and extracted device parameters are listed in Table 1.

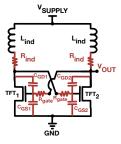

2.2 Resonant Oscillator Topology for High-Frequency TFT Circuits: Resonant oscillator circuits are essential to our hybrid LAE architecture because they generate high-frequency oscillations required for non-contact interfaces between different functional sheets within a system. High-frequency operation of LAE circuits is typically limited by low TFT transconductance  $g_m$ and high TFT gate-source/drain overlap and gate-to-channel capacitances  $C_{GS}$ ,  $C_{GD}$ , and  $C_{GCh}$ . To overcome these obstacles, we use high-quality planar inductors enabled by LAE [11] to resonate out large TFT capacitances in a resonant inductive-capacitive (LC) oscillator circuit. In this way, TFT oscillators operating above  $f_T$  can be robustly achieved. In this work we use the crosscoupled LC oscillator topology, pictured in Figure 5.  $L_{ind}$  and  $R_{ind}$ refer to the inductance and resistance of the planar inductor, TFT1 and TFT2 are two equally-sized ZnO TFTs,  $V_{SUPPLY}$  is the DC supply voltage,  $V_{OUT}$  is the node at which the output is measured,  $R_{gate}$  is the TFT gate resistance, and  $C_{GDI,2}$  and  $C_{GSI,2}$  are the TFT overlap capacitances.

**Figure 5.** Schematic of the cross-coupled LC oscillator topology, with relevant parameters labeled. Parasitic quantities are drawn in red.

If the positive feedback condition of this circuit is satisfied

$$g_m R_{TANK} = \frac{\left(\mu C_{GCh} \frac{W}{L} (V_{GS} - V_T)\right) L_{ind}}{C_{Par}(R_{ind} + R_{gate})} > 1, \tag{1}$$

then the circuit will oscillate at a frequency  $f_{osc}$  set by the inductance of the planar inductor  $L_{ind}$  and the  $C_{par}$  of the circuit:

$$f_{osc} = 1/(2\pi\sqrt{L_{ind}C_{par}}), \tag{2}$$

where  $C_{par}$ , due to Miller capacitances, is dominated by TFT overlap capacitances:

$$C_{par} = 2 \times (C_{GD1} + C_{GD2}) + C_{GS1,2} + C_{GCh}$$

$$\approx 5 \times C_{OV} + C_{GCh}$$

(3)

For a given TFT geometry and fabrication process, positive feedback is made easier by either (1) boosting  $V_{SUPPLY}$  and thereby boosting  $g_m$ , or (2) increasing the size of the inductor  $L_{ind}$ . Boosting  $V_{SUPPLY}$  results in increased power consumption, while increasing  $L_{ind}$  increases area and reduces the oscillation frequency (according to Eq'n. 2). Hence, careful circuit design and TFT materials improvement have important impacts on system-level metrics. In the following section we focus on design of the oscillator parameters that impact the feedback condition (Eq'n. 1) and frequency  $f_{osc}$  (Eq'n. 2).

## 2.3 Optimization of TFT $f_{MAX}$ for Oscillations Beyond $f_T$ :

Mobility  $\mu$  and device capacitances  $C_{GS}$ ,  $C_{GD}$ , and  $C_{GCh}$  are most prominent in setting the TFT's cutoff frequency,  $f_T$ , the frequency

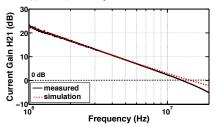

at which current gain is unity:  $f_T = g_m/2\pi (C_{GD} + C_{GCh} + C_{GS})$ . This motivates using ZnO for high  $g_m$  and minimizing gate-source/drain overlap size and channel length, all to 5  $\mu$ m. Figure 6 shows a representative measurement of current gain, H21, versus frequency, where the 0 dB intercept corresponds to  $f_T$ . Transistor-level Spectre simulations based on TFT models derived from extracted device parameters are also shown, and exhibit good agreement. At  $V_{GS} = V_{DS} = 9 V$ ,  $f_T = 12.9 \text{ MHz}$ .

**Figure 6.** ZnO TFT  $f_T$  measurement and simulation at bias point  $V_{GS} = V_{DS} = 9$  V for TFTs on glass substrates.

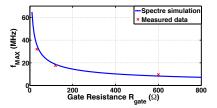

As discussed, resonant circuit topologies enable the oscillator frequency  $f_{osc}$  to exceed  $f_T$  if the condition for positive feedback (Eq'n. 2) is met at small inductance  $L_{ind}$ . However, an additional TFT limitation imposes a caveat:  $f_{MAX}$ , the TFT's unity power gain frequency, must exceed this resonant oscillation frequency  $f_{osc}$ , or oscillations will not occur.  $f_{MAX}$  is expected to exhibit a strong dependence on  $R_{gate}$ :

$$f_{MAX} = \frac{1}{2} \frac{f_T}{\sqrt{2\pi f_T C_{GD} R_{gate} + \frac{R_{gate}}{r_o}}},\tag{4}$$

Thus,  $R_{gate}$  is a new focus for TFT optimization in a device already optimized for  $f_T$ . Therefore, we reduced the  $\sim 3~\Omega/\text{sq}$  sheet resistance of our initial 100-nm-thick sputtered chrome gate metal to  $0.3~\Omega/\text{sq}$  by sandwiching an aluminum layer up to 80-nm thick between Cr bottom and top layers. Capping the Al layer with  $\geq$  20-nm-thick layer of Cr prevents sharp hillocks from forming during 200°C PEALD deposition; hillocks can puncture the 40-nm thin Al<sub>2</sub>O<sub>3</sub> gate dielectric and create electrical shorts. For this bottom-gate process, keeping the total gate metal thickness  $\leq$  120 nm ensures adequate step coverage by the 40 nm gate dielectric across the 75 mm X 75 mm substrates. Because Al is more ductile than Cr, this composite gate material also prevents the gate metal from cracking under strain on polyimide substrates.

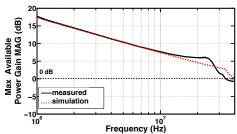

Figure 7 shows a representative power gain versus frequency measurement for a ZnO TFT with a Cr/Al/Cr gate electrode, where  $f_{MAX}$  is extracted from the curve's 0 dB intercept. The transistor-level Spectre simulations exhibit good agreement with data at low frequencies. The discrepancy between the experimental  $f_{MAX}$  of 33.9 MHz and the simulated result of 40 MHz may be due to residual parasitics in the measurement setup which were not fully de-embedded.

**Figure 7.** ZnO TFT  $f_{MAX}$  measurement and simulation at bias point  $V_{GS} = V_{DS} = 9$  V for TFTs on glass susbtrates.

To illustrate how important  $R_{gate}$  reduction is to raising  $f_{MAX}$ , Figure 8 shows the measured  $f_{MAX}$  of ZnO TFTs having three different gate resistances ( $f_{MAX}$  values predicted by Spectre simulation are also shown).

**Figure 8.** Dependence of ZnO TFT  $f_{MAX}$  on gate resistance  $R_{gate}$  for TFTs on glass substrates.

Note that  $g_m R_{TANK}$  (Eq'n. 1) depends inversely on the *sum* of  $R_{gate} + R_{ind}$ . Because oscillators presented here employ low resistance planar copper inductors,  $R_{gate} + R_{ind} \approx R_{gate}$ , and hence  $R_{gate}$  optimization has powerful consequences.

### 3. Results: Demonstrated Oscillator Circuits

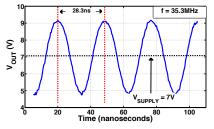

**3.1 ZnO TFT-based Oscillator on Glass:** Using ZnO TFTs with optimized  $f_{MAX}$  (reduced  $R_{gate}$  and high  $f_T$ ), we construct the cross-coupled LC oscillators described in section 2.2. To approach the frequency limitation ( $f_{MAX}$ ) set by the TFTs, we employ a range of planar spiral inductors with varying values of  $L_{ind}$ , all with low-resistance (low  $R_{ind}$ ) 25-µm-thick copper traces. Inspection of Eq'n. 1 and Eq'n. 2 indicates that reduction of  $R_{gate}$  and  $C_{par}$  allows the positive-feedback condition (Eq'n. 1) to be met with reduced  $L_{ind}$  values, which then results in higher oscillation frequencies (Eq'n. 2). Figure 9 shows the oscilloscope-measured output of a cross-coupled oscillator with  $L_{ind} = 1.5 \, \mu H$ . The circuit oscillates at  $f_{OSC} = 35.3 \, \text{MHz}$ , just below the simulated TFT  $f_{MAX}$ , and well above the  $f_T$  of 12.9 MHz.

Figure 9. Output of ZnO TFT oscillator on glass.

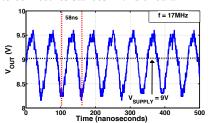

**3.2 ZnO TFT-based Oscillator on Plastic:** ZnO TFT oscillators on 3.5μm polyimide substrates are also able to achieve oscillation well above  $f_T$ . Figure 10 shows the oscilloscope-measured output of a cross-coupled oscillator with  $f_{OSC} = 17$  MHz, achieved at  $L_{ind} = 3.7$  μH and  $V_{DD}$  of 9 V. This frequency is lower than glass substrate counterparts, due to a higher effective  $R_{gate}$  (52  $\Omega$  instead of 33  $\Omega$ ). We are currently working to reduce parasitic interconnect resistances in this circuit.

Figure 10. Output of ZnO TFT oscillator on plastic.

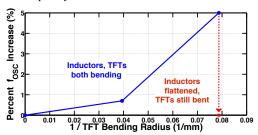

We measured the oscillation frequency while bending the plastic substrate into a cylinder, with the TFT channel length perpendicular to the direction of the axis of the cylinder, and with TFTs on the outside of the cylinder (corresponding to tensile strain). The change in oscillation frequency as a function of bending radius of the TFTs in the circuit is provided in Figure 11. When the entire oscillator (TFTs and inductors) is bent to the same radius, the frequency changes measurably. However, when the inductors are flattened, but the TFTs remain bent, the oscillation frequency returns to its unbent value.

Figure 11. Bending oscillators impacts oscillation frequency through the inductor, not the TFT. In this circuit,  $L_{ind}$  =152  $\mu$ H, V<sub>SUPPLY</sub> = 6.3 V, and unbent  $f_{OSC}$  = 2.2 MHz.

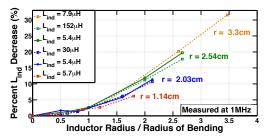

This behavior is explained as follows: the inductance  $L_{ind}$  of the planar inductors decreases as its bending radius increases, as shown in Figure 16. This causes the oscillator frequency to shift upwards upon bending. Indeed, the inductance  $L_{ind}$  of the planar inductors decreases as its bending radius increases, as shown in Figure 12, which suggests that the oscillator frequency shifts upon bending are caused by changing  $L_{ind}$ . We see that inductors with very different inductances but identical outer radius (i.e. different numbers of turns) have nearly identical bending behavior, which suggests that inductor geometry plays a role in this effect. For the inductor used in the oscillator measured while bending in Figure 11, we see a 10% reduction in inductance at an inverse bending radius of 0.08 inverse millimeters. Eg'n. 2 predicts a 5% increase in oscillation frequency as a result of a 10% inductance decrease, which is exactly the result we see in Figure 12. This change in oscillation frequency as a function of bending radius is important to consider in large area flexible systems employing resonant LC oscillators.

Figure 12. Bending planar spiral inductors significantly impacts inductance value, which impacts  $f_{OSC}$ .

# 3.3 Oscillation Frequency and Power Consumption:

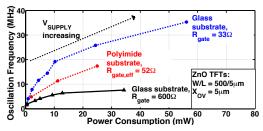

Because oscillator frequency can be increased at the cost of increased power consumption, it is useful to look at power consumption and frequency together. Figure 13 shows the maximum oscillation frequency we could achieve at a given level of power consumption for reduced- $R_{gate}$  ZnO TFT, high- $R_{gate}$  ZnO TFT, and flexible ZnO TFT cross-coupled oscillators. As seen, the use of ZnO TFTs with low  $R_{gate}$  in our cross-coupled oscillators leads to a substantial frequency-power improvement.

With improved interconnects we expect the results for oscillators on polyimide to approach the result for glass.

Figure 13. Power-Frequency comparison. For a given  $R_{gate}$ , oscillator frequency and power consumption are both increased by boosting  $V_{SUPPLY}$  to raise  $g_m$  (to more easily satisfy the positive feedback condition of Eq'n. 1), and then reducing  $L_{ind}$  to increase oscillation frequency (via Eq'n. 2).

### 4. Conclusions and Impact

In this work we demonstrate high-frequency oscillators on glass and ultrathin plastic. Because resonant oscillators are limited by TFT  $f_{MAX}$ , we focus on designing TFTs not only for improved  $f_T$ (i.e., by using ZnO for  $g_m$  improvement and by minimizing L,  $C_{OV}$ , and  $C_{OX}$ ), but also for high  $f_{MAX}$  (i.e., by minimizing  $R_{gate}$ through a composite low-resistance gate material). Because the fabrication process takes place ≤ 200°C, transitioning to flexible substrates is relatively straightforward. The 3.5-µm-thick spincoated polyimide substrate, in addition to being desirably thin, allows us to maintain the same TFT dimensions—and hence, critically, the same parasitic quantities  $R_{gate}$  and  $C_{par}$  that determine  $f_{MAX}$ —as a glass substrate. Oscillators are also evaluated while bending, and an increase in frequency is observed with decreasing bending radius. The increase in frequency corresponds exactly to the measured reduction in inductance of the planar inductors used. The observed change in oscillation frequency as a function of bending radius is important to consider in large area flexible systems employing resonant LC oscillators. Lastly, we investigated the tradeoff between oscillation frequency and power, which indicates that both frequency and power consumption benefit from  $f_{MAX}$ -optimized TFTs.

## 5. Acknowledgements

The authors thank the National Science Foundation for supporting this research (Grants ECCS-1202168 and CCF-1218206), the Princeton Program in Plasma Science and Technology (Grant DE-AC02 09CH11466), and Prof. T. N. Jackson and his students Yangyang Liu and Israel Ramirez for their guidance and support.

#### 6. References

- S. C. B. Mannsfeld, et al., Nat. Mat., 9 p.859, 2010.

- M. Melzer, et al., Adv. Mat., 27, p. 1274, 2015.

- [3] D-H. Kim, et al., Science, 333, p. 838, 2011.

- [4] S. Bauer et al., Adv. Mat., 26, p. 149, 2014.

- [5] N. Verma, et al., Proc. of IEEE, 103, p. 690, 2015.

- [6] W. Rieutort-Louis, et al., IEEE JPV, 4, p. 432, 2013.

- [7] D. A. Mourey, et al., IEEE TED, 57, p.530, 2010.

- [8] C. Pappas, IEEE Trans. on Appl. Super., 25, 2015.

- [9] H. Li, T.N. Jackson, IEEE EDL, 36, p. 35, 2015.

- [10] I-C. Cheng, et al., JSID, 13/7, p. 563, 2005.

- [11] Y. Hu, et al., VLSI Symp. Circuits, p. 120, 2012.