# A Lateral Silicon-on-Insulator Bipolar Transistor with a Self-Aligned Base Contact

JAMES C. STURM, MEMBER, IEEE, JAMES P. McVITTIE, MEMBER, IEEE, JAMES F. GIBBONS, FELLOW, IEEE, AND L. PFEIFFER

Abstract—A novel lateral bipolar transistor structure in silicon-oninsulator (SOI) is presented. The structure allows for a minimum geometry base width yet still provides for a metal contact to the entire base region. Fabricated transistors exhibit a base resistance of less than  $20~\Omega$ .

I. Introduction

THE advantages of bipolar transistors over MOSFET's for driving large loads and sensing low currents are well known. Several merged bipolar—CMOS processes have indeed emerged in conventional bulk technology which exploit these advantages [1]—[3]. These merged processes make use of the inherent vertical n-p-n structures present in a bulk CMOS process. In a thin-film silicon-on-insulator (SOI) CMOS technology, such vertical structures do not exist. Lateral bipolar transistors are, however, ideally suited to a thin film, and have the potential for sharing fabrication steps with MOSFET's. Unfortunately, lateral bipolar transistors suffer from an inherent performance limitation related to the base width and the base series resistance. In this letter a lateral bipolar SOI transistor structure is introduced which overcomes this inherent trade-off.

In a conventional lateral bipolar transistor, one can choose to make the base width the lithographic minimum dimension. This narrow base width minimizes the base transist time, but forces the base contact to be placed outside the active region. This leads to a high base resistance which can reduce the speed of the device and lead to severe current crowding. A 0.5-μmthick film doped 1017 cm<sup>-3</sup> p-type in the base region would have a sheet resistance of 4 k $\Omega/\square$ . Hence, in a device with a base width of only 1  $\mu$ m, current crowding would render all but the first few micrometers of the device useless. Alternatively, one could make the base wide enough such that one could fit a metal contact along the entire base region. Such a device would have a low base resistance, but the wider base width would severely affect the switching speed of the device because of the increased base transit time. Our new structure employs a narrow-base pedestal which can be contacted without any critical lithography. This allows for a minimumgeometry base width yet still provides for a metal contact to the entire base region. The details of the structure are discussed in the next section.

## II. FABRICATION

The "starting" materials for the fabrication were 1-μmthick strip-heater recrystallized silicon films on 2 µm of underlying oxide. The films were recrystallized using a "slow" scan which yielded films which were free of subgrain boundaries [4]. The dominant defect in the films was an array of threading dislocations with a spacing between dislocations of 75 µm perpendicular to the scan direction and a spacing of  $\sim 1 \mu m$  along the scan direction. The films were patterned into individual islands for device isolation and were then implanted to provide a uniform boron doping of 8 imes 10  $^{16}$  cm $^{-3}$ . Then 2000 Å of thermal oxide was grown by thermal oxidation, followed by a second boron implant chosen to have its peak at the silicon surface and yield a surface dopant concentration of 10<sup>20</sup> cm<sup>-3</sup>. Lithography was then used to define narrow stripes of photoresist which would eventually define the base region. These stripes ranged down to approximately 2  $\mu$ m in width, the lithographic minimum dimension for the tools we used. (This mask was actually the "gate" mask of a standard MOS

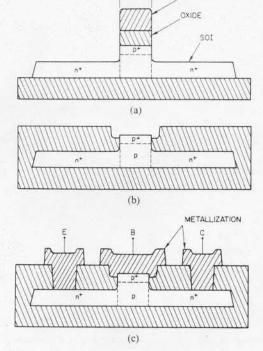

The photoresist stripes were then used as a mask for the vertical plasma etching of the oxide, followed by vertical etching of the silicon. The silicon etch was adjusted to etch approximately halfway through the silicon film. Arsenic ion implantation and annealing were then used to form the n<sup>+</sup> emitter and collector regions on either side of the silicon pedestal in the base. The photoresist and oxide masked the implant from penetrating into the base region. At this point the structure resembled that diagrammed in Fig. 1(a). Note that the base width corresponds to the lithographic minimum dimension. Structures similar to this have been described previously [5], [6]. However, in these structures the base regions were still contacted outside the active device region, leading to potential base-resistance problems.

Following the collector-emitter implantation, the photoresist and oxide were removed and the implant was annealed. An oxide deposition and planarization were performed. A lithography step then defined holes for the contact to the base region, and a wet oxide etch was done to expose the top of the base pedestal but not to expose the n<sup>+</sup> regions (Fig. 2(b)). Conventional definition and etching of the collector-emitter

Manuscript received December 2, 1986.

J. C. Sturm was with Stanford Electronics Labs, Stanford, CA 94305. He is now with the Department of Electrical Engineering, Princeton University, Princeton, NJ 08544.

J. P. McVittie and J. F. Gibbons are with Stanford Electronics Labs, Stanford, CA 94305.

L. Pfeiffer is with AT&T Bell Laboratories, Murray Hill, NJ 07974. IEEE Log Number 8613335.

Fig. 1. Cross section of the device structure (a) after the collector-emitter implant, (b) after the base contact etch, and (c) after the completion of processing.

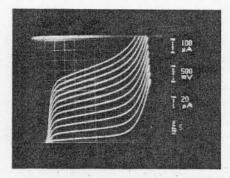

Fig. 2. Common-emitter curve-tracer characteristic of a 2-μm device.

contacts and a multilayer metallization step completed the processing.

Although the base width corresponds to the lithographic minimum dimension, no critical lithography or alignment was required to make a metal contact to the entire base region. The heavy p<sup>+</sup> doping at the top of the base pedestal serves two purposes. First, it provides for a low-resistance ohmic contact. Second, it provides a built-in electric field which repels minority-carrier electrons in the base away from the metal base contact. Electrons reaching the base contact would recombine and give rise to base current, not the collector current desired in normal bipolar transistor operation.

# III. RESULTS

from 2 to 10  $\mu$ m, and a device length of 50  $\mu$ m. (This corresponded to the MOS "gate" mask used for the base definition having a series of W/L from 50/2 to 50/10.) Shown in Fig. 2 is a common-emitter curve-tracer characteristic of a

breakdown voltage  $V_{CEO}$  of 4-7 V, and had a typical current gain of 2.

Considering the doping profiles used in the transistors, the  $2\text{-}\mu\text{m}$  device might have been expected to exhibit current gain on the order of 10–50. To identify the cause of the low current gain, measurements were made on transistors of different base widths. It was found that the gain of the transistors was strongly dependent on base width (Fig. 3). The exponential dependence of gain on the base width means that most of the electrons injected into the base at the emitter are recombining before they diffuse across the base to the collector. From the slope in Fig. 3, an effective lateral minority-carrier diffusion length of 1.4  $\mu\text{m}$  can be extracted.

Because the silicon film is thin, the lateral diffusion of minority carriers will be limited by recombination at the film interfaces as well as by recombination within the "bulk" of the film itself. Of special concern in our case is possible recombination at the metal base contact on top of the base region. To test if the vertical built-in base field indeed was successful in repelling electrons away from the base contact, a second series of lateral transistors was fabricated in identically prepared films. This series of transistors had the base contact outside the active device region, and no p+ surface implant to create a vertical field. The interface on top of the base region in this case was an annealed silicon-silicon dioxide interface, presumably one with a low surface recombination velocity. The collector current of these devices also had an exponential dependence on base width, with a characteristic length of 1.5  $\mu$ m. Comparing this to the earlier diffusion length of 1.4  $\mu$ m, we conclude that recombination at the metal base contact was not the site of the dominant recombination in the self-aligned devices. This leaves the "bulk" of the SOI film or the bottom interface as the location of the dominant recombination centers.

A major goal of this device design was to minimize the base resistance. Measurements of the base-emitter and basecollector diodes in forward bias consistently showed a series resistance of 75-100  $\Omega$ . Because the mask set used for the devices was based on a standard MOS test set, the collectoremitter contacts were removed  $\sim 50 \mu m$  from the active device. The sheet resistance of the collector and emitter regions was  $\sim 50 \Omega/\Box$ , and hence largely responsible for the above series resistance. (An optimized device would of course have the emitter and collector contacts very close to the base region.) By connecting the emitter and collector together and repeating the above measurements, it is possible to separate the effects of base resistance and those of emitter (collector) resistance. Although this analysis was limited by a nonzero probing resistance, we were able to establish an upper limit to the base resistance of 20  $\Omega$ —an exceptionally low number.

# IV. DISCUSSION

The motivation for this work was to develop a bipolar transistor to merge with a thin-film SOI (SOS) CMOS process. One can make a vertical bipolar transistor directly in a thin  $(0.75~\mu\text{m})$  film, but such a structure has too large a collector resistance to be a useful driver [7]. Alternatively, one might

Fig. 3. Gain versus base width for the self-aligned devices.

grow epi on the thin SOI film for vertical bipolar transistors [8], [9]. Such an approach, however, would greatly complicate the fabrication process. Hence we resorted to lateral structures. By providing a body contact to a SOI MOSFET, one can operate the device as a lateral bipolar transistor [10], [11], but, as pointed out earlier, the usefulness of such a structure is inherently limited because of the base resistance. Our structure overcomes the above limitations, and could be merged with an SOI CMOS structure with only one or two extra masks. In addition to using 1- $\mu$ m-thick films for our fabrication process, we have also used 0.4- $\mu$ m-thick films coated with a 0.5- $\mu$ m layer of polysilicon and achieved similar results. These thinner starting films would be more compatible with advanced short-channel CMOS fabrication processes.

Simple calculations show the speed of the device to be dominated by the base transit time down to base widths of less than 0.5  $\mu$ m. In a one-dimensional approximation, the base transit time  $\tau_B$  is given by  $W_B^2/2D_n$ . For example, a 0.5- $\mu$ m device would have a base transit time of roughly 60 ps. While this is not small compared to the transit time of modern digital bipolar circuitry, it is probably adequate to serve as a driver for merged CMOS-bipolar applications. Because the device is isolated on all sides by oxide, the parasitic capacitances in the device should be small. One drawback, however, is the absence of a lightly doped collector region. Such a lightly doped region is necessary for a minimum base-collector capacitance.

The gain of the devices was shown earlier to be limited by a minority-carrier diffusion length of only 1.4  $\mu$ m. This occurred despite the fact that the devices were small enough and oriented so that the active regions fit between the dislocation defects mentioned earlier. For a gain of 50, base

$\mu$ m for a 1- $\mu$ m device). Recombination diffusion lengths of from 5 to 10  $\mu$ m have been observed in some strip-heater recrystallized films [10], [11]. Experiments are underway to identify and remove the source of the recombination (filing defects, interface states, etc.) in our films.

# V. CONCLUSION

A novel lateral bipolar structure has been developed that allows for both a minimum-geometry base width and a metal contact to the entire base region. Fabricated devices did indeed exhibit an extremely low base resistance, while the current gain of the devices appeared to be limited by recombination in the SOI film. While this device was developed with merged SOI (SOS) CMOS processes in mind, the basic structure should be adaptable to bulk lateral transistors as well.

# ACKNOWLEDGMENT

The assistance of K. West in performing the recrystallization is greatly appreciated. This experiment would also not have been possible without the dedicated assistance of the staff of the Stanford I.C. Lab.

# REFERENCES

- O. Minato, T. Masuhara, T. Sasaki, Y. Sakai, and T. Hayashida, "A HI-CMOSII 8K × 8b static RAM," in ISSCC Dig. Tech. Papers, 1982, pp. 256–257.

- [2] J. Miyamoto, S. Saitoh, H. Momose, H. Shibata, K. Kanzaki, and S. Kohyama, "A 1.0 μm n-well CMOS/bipolar technology for VLSI circuits," in *IEDM Tech. Dig.*, 1983, pp. 63-66.

- [3] E. L. Hudson and S. L. Smith, "An ECL compatible 4K CMOS RAM," in ISSCC Dig. Tech. Papers, 1982, pp. 248-249.

- [4] L. Pfeiffer, K. W. West, D. C. Joy, J. M. Gibson, and A. E. Gelman, "Reduced subboundary misalignment in SOI films scanned at low velocities," in *Mater. Res. Soc. Symp. Proc.*, vol. 53, 1986, pp. 29– 38.

- [5] T. H. Ning and D. D. Tang, "High performance lateral bipolar transistor on insulating substrate," IBM Tech. Discl. Bull., vol. 26, pp. 5858-5862, 1984.

- [6] M. Nakano, "Lateral bipolar transistor on an insulating substrate," European Patent 84110211.4, publ. 0137992, 1984.

- [7] J. C. Sturm and J. F. Gibbons, "Vertical bipolar transistors in laser recrystallized polysilicon," *IEEE Electron Device Lett.*, vol. EDL-6, pp. 400-402, 1985.

- [8] E. W. Greeneich and R. H. Reuss, "Vertical n-p-n bipolar transistors fabricated on buried oxide SOI," *IEEE Electron Device Lett.*, vol. EDL-5, pp. 91-93, 1984.

- [9] H. Münzel, G. Albert, and H. Strack, "Vertical bipolar transistors on buried silicon nitride layers," *IEEE Electron Device Lett.*, vol. EDL-5, pp. 283–285, 1984.

- [10] M. Rodder and D. A. Antoniadis, "Silicon-on-insulator bipolar transistors," *IEEE Electron Device Lett.*, vol. EDL-4, pp. 193–195, 1983.

- [11] B.-Y. Tsaur, D. J. Silversmith, J. C. C. Fan, and R. W. Mountain, "Fully isolated lateral bipolar-MOS transistors fabricated in zonemelting-recrystallized Si films on SiO<sub>2</sub>," *IEEE Electron Device Lett.*, vol. EDL-4, pp. 269-271, 1983.