# SILICON AND SILICON-GERMANIUM EPITAXY FOR QUANTUM DOT DEVICE FABRICATIONS TOWARDS AN ELECTRON SPIN-BASED QUANTUM COMPUTER

#### Kun Yao

A DISSERTATION

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

ELECTRICAL ENGINEERING

ADVISER: JAMES C. STURM

September 2009

© Copyright by Kun Yao, 2009. All Rights Reserved

#### Abstract

Semiconductor quantum dots are promising candidates as qubits for spin-based quantum computation as they provide highly tunable structures for trapping and manipulating individual electrons. It is the objective of this doctorate thesis to study on the development of silicon and silicon-germanium epitaxy and nanofabrication techniques for quantum dot devices, and the performance level achieved in the silicon/silicon-germanium material heterosystem.

We describe the growth of two-dimensional electron gas structures in strained Si on high-quality SiGe relaxed buffers with low temperature mobility exceeding 10,000 cm<sup>2</sup>/Vs, currently limited by the background impurities in our RTCVD system. The modulation of the electron gases using atomic layer deposited Al<sub>2</sub>O<sub>3</sub> is also demonstrated. We have developed a wide range of fabrication methods of the electron gases for quantum dot applications including nanolithography and etching techniques optimized for etch selectivity and anisotropy. Feature sizes well under 100 nm can be reliably obtained.

To achieve precise control of exchange coupling of qubits, we present a new concept of parallel 2-D electron gases in a double quantum wells as interaction dimers. A typical value of 0.1 meV for symmetric-anti-symmetric splitting of subbands is predicted by modeling. The signature of inter-well scattering is proved by a negative transconductance effect measured in such structures. The physical realization of such qubit dimers can also enable a novel "flying qubit" scalable architecture for semiconductor-based quantum computers.

The robustness of quantum dot devices is often strongly affected by defect states on the surface arising from the Si/SiO<sub>2</sub> interface. We demonstrate the use of epitaxial regrowth of SiGe for surface passivation, done with thermal cleaning temperatures less than 800 °C and negligible degradation of device performance. Side-gated multiple quantum point contacts are fabricated. They can be used to completely deplete

electrons on a quantum dot with gate leakage less than a few nA. We have also observed periodic single electron tunneling conductance peaks in a single quantum dot transistor with a side-gate-to-dot capacitance of 4.4 aF.

#### Acknowledgements

First of all, I want to thank Princeton University and the Department of Electrical Engineering for giving me this wonderful opportunity to carry out my research work in the first instance.

I am deeply indebted to my advisor Professor James C. Sturm, whose perpetual enthusiasm, stimulating insight, and constant encouragement that have shaped me throughout the years. I always feel extremely lucky to have had worked with him inside and outside the laboratory. I also wish to thank Professors Jason R. Petta and Antoine Kahn for reviewing this thesis. Furthermore, Professors Sigurd Wagner, Mansour Shayegan, Stephen A. Lyon, Daniel C. Tsui, and Stephen Y. Chou are always willing to help me whenever I need their guide. They have set a role model of a great teacher and mentor.

This thesis could not have been achieved without all the collaborators. I would like to express my gratitude to Professor Leonid P. Rokhinson and his post-doc Dr. Alexander Chernyshov at Purdue University for their low-temperature measurement, Dr. Anthony Lochtefeld and his team at AmberWave Systems for their preparation of SiGe relaxed buffers, and Professor Ya-Hong Xie at UCLA for providing MBE samples. At Princeton, I would like to thank e-beam nanolithography expert Dr. Mikhail Gaevski, TEM imaging and analysis expert Dr. Nan Yao, and Shyam Shankar from Lyon group for his help with ESR measurement. I treasured all the cooperative work experiences that made the research more rewarding for me.

A special thanks goes to all members in Sturm group. Malcolm S. Carroll, Haizhou Yin, Xiang-Zheng Bo, Eric J. Stewart, Rebecca L. Peterson, Keith H. Chung, Weiwei Zheng, Sushobhan Avasthi, and Jiun-Yun Li are all among our RTCVD hall of fame. In particular, I am obliged to Keith for his friendship and loyal support to carry the reactor upon our shoulders for nearly half decade. All other folks, including Iris Hsu, Richard Huang, Ke Long, Troy G. Abe, John A. Davis, David Inglis, Hongzheng

Jin, Bahman Hekmatshoar, Yifei Huang, Noah Jafferis, and Kevin Loutherback, con-

tributed to make the lab a fun place to work. I would also like to thank my colleagues

in Tsui group, Gabor Csathy, Yong Chen, Zhihai Wang, Keji Lai, Tzu-Ming Lu, and

Dwight Luhman. They are great physicists and have offered me broad perspectives

during countless discussions.

My doctoral research would be very painful if I did not have the kind support from

PRISM and EE staffs. I am thankful to Dr. Helena Gleskova (now on the faculty

of the University of Strathclyde in Scotland), Dr. George Watson, Dr. Conrad L.

Silvestre, and Joe E. Palmer for their conscientious maintenance of the cleanroom. I

truly appreciate Cathy A. Wertz, Sarah M. Braude, Carolyn M. Arnesen and Sheila

R. Gunning for their generous help.

Finally, my deepest gratitude goes to my family for their love and care throughout

my life; I am simply impossible without them. I grew up in a typical south China

small town and have come a long way. I have no suitable words that can describe

the evergreen support from my parents and brother from oversea in the past eight

years. Last but not least, to my fiancée Lan, I remember all the moments with your

accompanying me during the hard times. Your love enabled me to accomplish this

work.

Thank you! Thank You!! Thank YOU!!!

vi

To the victims and heroes of September 11, 2001 On that day I was sitting 50 miles away at Princeton university graduate school orientation in Richardson auditorium in Alexander Hall.

# Contents

|          | Abst | tract . |                                                        | ii  |

|----------|------|---------|--------------------------------------------------------|-----|

|          | Ack  | nowledg | gements                                                | v   |

|          | List | of Tabl | les                                                    | xii |

|          | List | of Figu | nres                                                   | xiv |

| 1        | Intr | oducti  | ion                                                    | 2   |

|          | 1.1  | Motiva  | ation                                                  | 2   |

|          | 1.2  | A Brie  | ef History of Quantum Computing                        | 3   |

|          | 1.3  | Thesis  | s Outline                                              | 5   |

| <b>2</b> | Si/S | SiGe E  | pitaxy                                                 | 8   |

|          | 2.1  | Introd  | luction                                                | 8   |

|          | 2.2  | The S   | trained Si/SiGe Heterostructures                       | 10  |

|          |      | 2.2.1   | Structural Properties                                  | 10  |

|          |      | 2.2.2   | Band Alignment                                         | 12  |

|          | 2.3  | Si and  | SiGe Epitaxy at Princeton                              | 16  |

|          |      | 2.3.1   | Overview of the RTCVD Epitaxy                          | 16  |

|          |      | 2.3.2   | The Use of Commercially-available SiGe Relaxed Buffers | 18  |

|          |      | 2.3.3   | Infrared Absorption of Si and SiGe                     | 21  |

|          |      | 2.3.4   | Growth Rates and Doping Profiles                       | 27  |

|          | 2.4  | Summ    | arv                                                    | 30  |

| 3 | The | Two-    | dimensional Electron Gas in Strained Silicon                            | 32 |

|---|-----|---------|-------------------------------------------------------------------------|----|

|   | 3.1 | Introd  | luction                                                                 | 32 |

|   | 3.2 | Chara   | cterization of the 2DEG's                                               | 35 |

|   |     | 3.2.1   | Sample Structures                                                       | 35 |

|   |     | 3.2.2   | Effect of Substrate Doping in Relaxed SiGe Buffers on Leakage           | 38 |

|   |     | 3.2.3   | Magneto-transport Properties                                            | 41 |

|   |     | 3.2.4   | Electron Spin Resonance of Electrons in Si and SiGe                     | 43 |

|   | 3.3 | Theor   | etical Mobility Models                                                  | 46 |

|   |     | 3.3.1   | Calculation of Mobility Limited by Coulomb Scattering Mech-             |    |

|   |     |         | anisms                                                                  | 46 |

|   |     | 3.3.2   | The Effect of Background Impurities                                     | 51 |

|   |     | 3.3.3   | Efforts Towards Lower Background Impurities                             | 54 |

|   | 3.4 | Modu    | lation of Si/SiGe 2DEG Electron Density with Top Gating                 | 55 |

|   |     | 3.4.1   | $\mathrm{Al_2O_3}$ High-k Gate Dielectric by Atomic Layer Deposition $$ | 55 |

|   |     | 3.4.2   | Modulation of Si/SiGe 2DEG Electron Density                             | 57 |

|   | 3.5 | Summ    | nary                                                                    | 64 |

| 4 | Par | allel T | wo-Dimensional Electron Gases in Double Quantum Wells                   | 65 |

|   | 4.1 | Introd  | luction                                                                 | 65 |

|   | 4.2 | Model   | ing of the Double Quantum Well Systems                                  | 68 |

|   |     | 4.2.1   | Design of Double Quantum Well Systems                                   | 68 |

|   |     | 4.2.2   | Asymmetric Double Quantum Wells                                         | 71 |

|   |     | 4.2.3   | Symmetric Double Quantum Wells                                          | 72 |

|   |     | 4.2.4   | Comparison of Double Quantum Well Schemes                               | 75 |

|   | 4.3 | Chara   | cterization of the Double Quantum Well Systems                          | 78 |

|   |     | 4.3.1   | Growth of Si/SiGe Double Quantum Wells                                  | 78 |

|   |     | 4.3.2   | Modulation of Si/SiGe Parallel Two-Dimensional Electron Gases           | 79 |

|   | 4.4 | Summ    | arv                                                                     | 86 |

| 5 | Fab  | ricatio | on Methods for Quantum Dot Applications               | 88  |

|---|------|---------|-------------------------------------------------------|-----|

|   | 5.1  | Introd  | luction                                               | 88  |

|   | 5.2  | Nanol   | ithography Methods                                    | 90  |

|   |      | 5.2.1   | Electron-Beam Lithography at Princeton                | 90  |

|   |      | 5.2.2   | PFOTS-aided AFM Lithography                           | 93  |

|   |      | 5.2.3   | Comparison of Nanolithography Methods                 | 98  |

|   | 5.3  | Etchir  | ng Methods                                            | 100 |

|   |      | 5.3.1   | Wet Etching of Si and SiGe                            | 100 |

|   |      | 5.3.2   | Dry Etching of Si and SiGe                            | 104 |

|   |      | 5.3.3   | Mix of Dry and Wet Etching of Si/SiGe                 | 109 |

|   | 5.4  | Summ    | nary                                                  | 110 |

| 6 | Si/S | SiGe E  | pitaxial Regrowth                                     | 113 |

|   | 6.1  | Introd  | luction                                               | 113 |

|   | 6.2  | Cleani  | ing Processes for Si/SiGe Epitaxial Regrowth          | 115 |

|   |      | 6.2.1   | Low-temperature Surface Cleaning by $H_2$ Bake        | 115 |

|   |      | 6.2.2   | Chlorine Etching for Low-temperature Surface Cleaning | 117 |

|   |      | 6.2.3   | Conformal Epitaxial Regrowth on Sidewalls             | 119 |

|   | 6.3  | Electr  | ical Properties of Si/SiGe Epitaxial Regrowth         | 121 |

|   |      | 6.3.1   | The Effect of Si/SiGe Regrowth on 2DEG's              | 121 |

|   |      | 6.3.2   | The Leakage Across Si/SiGe Regrown Layers             | 122 |

|   | 6.4  | Summ    | nary                                                  | 125 |

| 7 | Cha  | aracter | rization of Quantum Dot Devices                       | 127 |

|   | 7.1  | Introd  | luction                                               | 127 |

|   | 7.2  | Chara   | ctierizaton of Quantum Point Contact Devices          | 129 |

|   |      | 7.2.1   | A Single Quantum Point Contact Device                 | 129 |

|    |                                               | 7.2.2                                                       | Quantum Point Contacts Used as Tunnel Junctions in A Quan- |                                                                                   |

|----|-----------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|

|    |                                               |                                                             | tum Dot                                                    | 131                                                                               |

|    | 7.3                                           | Charac                                                      | eterization of Single Quantum Dot Devices                  | 134                                                                               |

|    |                                               | 7.3.1                                                       | Coulomb Blockade and Quantum Dot Energies                  | 134                                                                               |

|    |                                               | 7.3.2                                                       | A Single Quantum Dot Device                                | 138                                                                               |

|    | 7.4                                           | Summa                                                       | ary                                                        | 141                                                                               |

| 8  | Con                                           | clusion                                                     | as and Future Work                                         | 143                                                                               |

|    | 8.1                                           | Conclu                                                      | sions                                                      | 143                                                                               |

|    | 8.2                                           | Future                                                      | Work                                                       | 145                                                                               |

|    |                                               | 8.2.1                                                       | Short-term Outlook                                         | 145                                                                               |

|    |                                               | 8.2.2                                                       | Long-term Outlook                                          | 148                                                                               |

| Bi | bliog                                         | raphy                                                       |                                                            | 150                                                                               |

| ΑI | PPE                                           | NDICE                                                       | es e                   | 161                                                                               |

|    |                                               |                                                             |                                                            |                                                                                   |

| A  | Sam                                           | ple R7                                                      | TCVD Growth Sequences                                      | 161                                                                               |

| A  |                                               |                                                             | action                                                     | <ul><li>161</li><li>161</li></ul>                                                 |

| A  | A.1                                           | Introdu                                                     |                                                            | 161                                                                               |

| A  | A.1<br>A.2                                    | Introdu<br>Growtl                                           | action                                                     | 161<br>162                                                                        |

| В  | A.1<br>A.2<br>A.3                             | Introdu<br>Growtl<br>Growtl                                 | n Sequences #4822: Asymmetric Double Quantum Well          | 161<br>162                                                                        |

|    | A.1<br>A.2<br>A.3                             | Introdu<br>Growth<br>Growth                                 | action                                                     | 161<br>162<br>167                                                                 |

|    | A.1<br>A.2<br>A.3<br>Sam<br>B.1               | Introdu Growtl Growtl                                       | n Sequences #4822: Asymmetric Double Quantum Well          | <ul><li>161</li><li>162</li><li>167</li><li>171</li></ul>                         |

|    | A.1<br>A.2<br>A.3<br>Sam<br>B.1               | Introdu<br>Growth<br>Growth<br>Introdu<br>Top-ga            | n Sequences #4822: Asymmetric Double Quantum Well          | <ul><li>161</li><li>162</li><li>167</li><li>171</li><li>171</li></ul>             |

|    | A.1<br>A.2<br>A.3<br>Sam<br>B.1<br>B.2<br>B.3 | Introdu<br>Growth<br>Aple Str<br>Introdu<br>Top-ga<br>Symme | action                                                     | <ul><li>161</li><li>162</li><li>167</li><li>171</li><li>171</li><li>172</li></ul> |

|    | A.1<br>A.2<br>A.3<br>Sam<br>B.1<br>B.2<br>B.3 | Introdu<br>Growth<br>Aple Sta<br>Introdu<br>Top-ga<br>Symme | Asymmetric Double Quantum Well                             | 161<br>162<br>167<br><b>171</b><br>171<br>172<br>173                              |

# List of Tables

| 2.1 | Selected physical properties of unstrained bulk silicon and germanium      |     |

|-----|----------------------------------------------------------------------------|-----|

|     | at room temperature                                                        | 9   |

| 2.2 | Summary of AmberWave Systems SiGe relaxed buffers                          | 20  |

|     |                                                                            |     |

| 5.1 | Common properties of Si/SiGe wet-chemical etchants on planar sub-          |     |

|     | strates                                                                    | 101 |

| 5.2 | Properties of Si/SiGe RIE using different etch gases on planar substrates. | 108 |

|     |                                                                            |     |

| 6.1 | Effects of SiGe epitaxial regrowth on 2DEG                                 | 122 |

|     |                                                                            |     |

| 7.1 | Fitted curve parameters of quantum dot conductance oscillation peaks       |     |

|     | (All units are in Volts)                                                   | 140 |

# List of Figures

| 1   | Sensation: Interior View (2006) is an abstract sculpture by Jersey         |    |

|-----|----------------------------------------------------------------------------|----|

|     | City artist Nancy Cohen that was inspired by discussions with Prince-      |    |

|     | ton University President Shirley Tilghman. Tilghman, a leader in the       |    |

|     | field of molecular biology, collaborated with Cohen and Princeton Uni-     |    |

|     | versity Electrical Engineering Professor James Sturm on the artwork,       |    |

|     | which is an abstraction about the sense of smell and how odors are         |    |

|     | recognized and remembered. Multi-colored cast resin discs are affixed      |    |

|     | to a steel armature forming a wall that connects to bulb-shaped struc-     |    |

|     | tures by vibrant wires. The different colors of discs represent the sensor |    |

|     | neurons in the nose that detect different odorant molecules; the wires     |    |

|     | represent the axonal connections that pass through the skull to the        |    |

|     | olfactory bulb in the brain, with the neurons from each type of sen-       |    |

|     | sor going to their own specific region in the olfactory bulb. (Image       |    |

|     | courtesy of NSF, from NSF IPAMM final report, 2007)                        | 1  |

| 2.1 | Schematic lattice structure of thin silicon deposited on silicon germa-    |    |

|     | nium substrate: (a) the SiGe lattice constant is larger compared to        |    |

|     | that of bulk Si; (b) the pure Si lattice attempts to line up with the      |    |

|     | SiGe lattice, which causes the Si to become tensilely strained. (Image     |    |

|     | courtesy of IBM www.ibm.com)                                               | 11 |

| 2.2 | [19] Critical thickness against fraction for $Si_1 - xGe_x$ on $Si$ . The lowest        |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | curve gives the theoretical limit in thermal equilibrium, whereas the                   |    |

|     | experimental curve is for a metastable layer grown at 550 $^{\circ}\mathrm{C}$ by MBE.  | 13 |

| 2.3 | [20] Summary of energy-gap values of SiGe alloys, both unstrained                       |    |

|     | bulk and strained SiGe on $\mathrm{Si}(100)$ substrate, at 90 K after correcting        |    |

|     | for quantum well shifts (circles = $75\text{Å}$ wells; triangles = $33\text{Å}$ wells). |    |

|     | The double points at the same values of x correspond to a splitting                     |    |

|     | of the valence band. The unstrained bulk alloy data are from optical                    |    |

|     | absorption measurement by Braunstein [21]                                               | 14 |

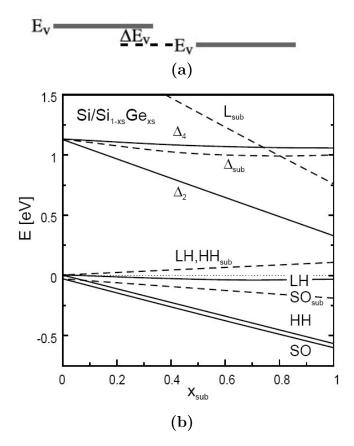

| 2.4 | (a) The splitting of Si conduction bands in tensilely strained Si/SiGe                  |    |

|     | heterostructures. (b) [19] Variation of the relevant silicon conduction                 |    |

|     | and valence bands of a tensilely strained Si/SiGe heterostructure as a                  |    |

|     | function of relaxed SiGe substrate composition $x_{sub}$                                | 15 |

| 2.5 | Schematic of Princeton RTCVD system used in this thesis. (Image                         |    |

|     | courtesy of P. V. Schwartz [28])                                                        | 17 |

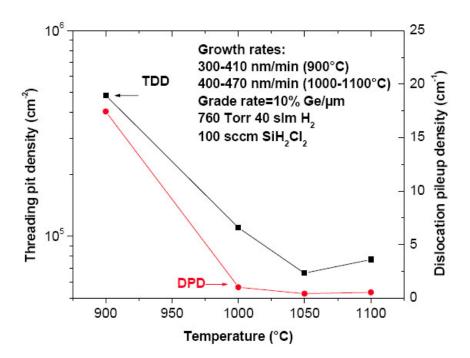

| 2.6 | [30] Effect of temperature on AmberWave graded buffer threading dis-                    |    |

|     | location density (TDD) and dislocation pileup density (DPD), deter-                     |    |

|     | mined by etch pit density and plan view TEM, respectively                               | 19 |

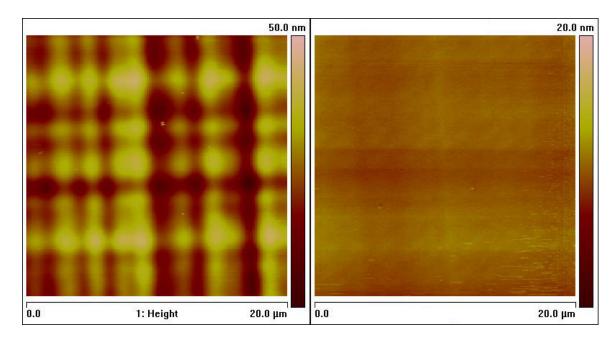

| 2.7 | Top-view AFM images of: (left) AW3L SiGe relaxed buffers with cross-                    |    |

|     | hatch patterns, surface RMS = $7.05$ nm; (right) AW3H SiGe relaxed                      |    |

|     | buffers after polishing, surface RMS = $0.57$ nm                                        | 20 |

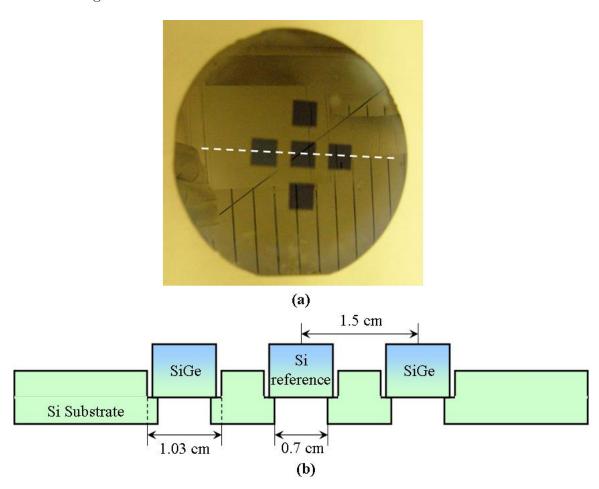

| 2.8 | (a) A picture of 5 1×1 cm square pieces loaded on a 100-mm carrier                      |    |

|     | wafer used for RTCVD growth. (b) A schematic view of cross section                      |    |

|     | along the dashed line in (a) showing the dimensions of recessed holes.                  | 21 |

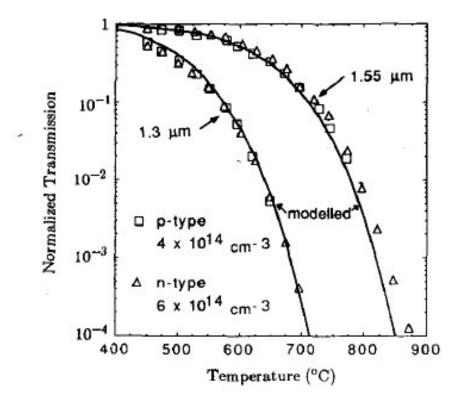

| 2.9  | [29] Data of normalized transmission vs. temperature for 1.30 and                                                     |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | 1.55 $\mu m$ , for lightly doped <100> n-type (7.5 $\Omega \cdot cm$ , thickness = 513                                |    |

|      | $\mu \mathrm{m}$ ) and p-type (37 $\Omega \cdot \mathrm{cm}$ , thickness = 493 $\mu \mathrm{m}$ ). The data have been |    |

|      | adjusted to reflect a 500- $\mu \mathrm{m}$ thickness. For comparison, also presented                                 |    |

|      | are the model results for the n-type wafer                                                                            | 24 |

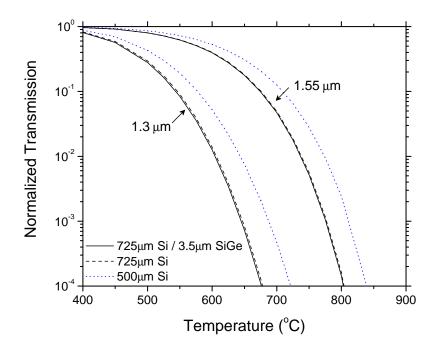

| 2.10 | Model of normalized transmission vs. temperature for $1.30$ and $1.55$                                                |    |

|      | $\mu \rm m,$ for lightly doped <100> p-type (1×10^{15} cm^{-3}, thickness=725 $\mu \rm m)$                            |    |

|      | plus a $\mathrm{Si_{0.7}Ge_{0.3}}$ buffer (thickness = 3.5 $\mu\mathrm{m}$ ). Also presented are the                  |    |

|      | model results for a 500- $\mu$ m thick silicon                                                                        | 26 |

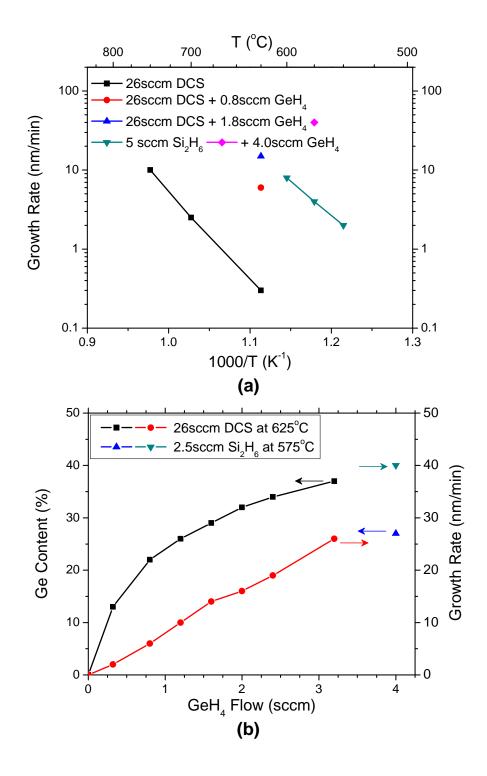

| 2.11 | Growth rate and Ge content of SiGe layers using DCS and disilane at                                                   |    |

|      | different temperatures and gas flow rates                                                                             | 29 |

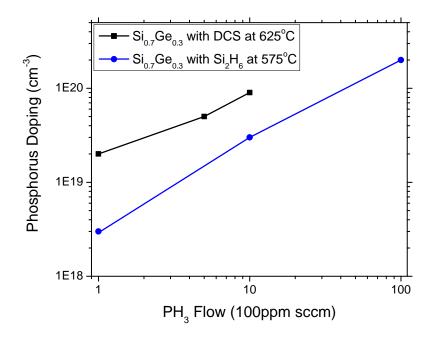

| 2.12 | N-type doping level in $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ vs. phosphine flow (100 ppm in hy-                        |    |

|      | drogen) layer grown at two different conditions                                                                       | 30 |

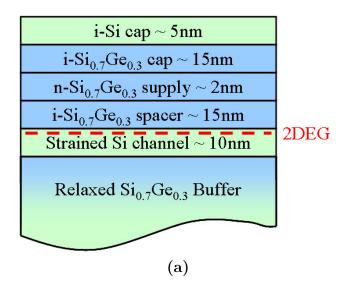

| 3.1  | (a) A typical structure of modulation-doped layers on a relaxed SiGe                                                  |    |

|      | buffer layer. (b) The band diagram shows a type-II band alignment                                                     |    |

|      | with the electrons confined in the tensilely strained Si channel. The                                                 |    |

|      | surface potential is assumed so that $V_{Schottky} = -0.1$ V. The electron                                            |    |

|      | wave function is plotted in red (in arbitrary units)                                                                  | 34 |

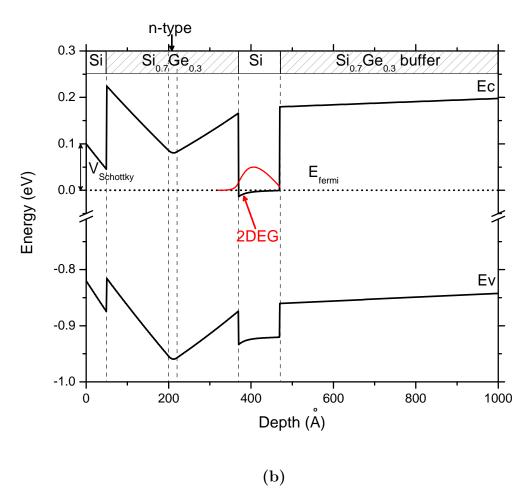

| 3.2  | [25] Temperature dependences of electron mobility for a Si/SiGe het-                                                  |    |

|      | erostructure with a graded buffer layer $(0 \le x_s \le 0.2)$ from literature                                         |    |

|      | [34, 35, 36, 37, 38, 39, 40]. Dotted lines are samples with a single-step                                             |    |

|      | buffer layer; dashed lines are samples with a graded buffer layer; solid                                              |    |

|      | line uses MBE combined with solid-phase epitaxy (SPE)                                                                 | 36 |

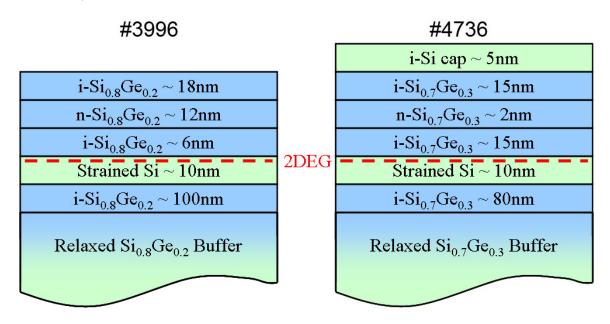

| 3.3  | Layer sequences for the two 2DEG samples $\#3996$ and $\#4736$ . The                                                  |    |

|      | n-type doping level is $\sim 10^{19}~{\rm cm}^{-3}$ in both samples; grown with DCS                                   |    |

|      | as in Fig. 2.12                                                                                                       | 37 |

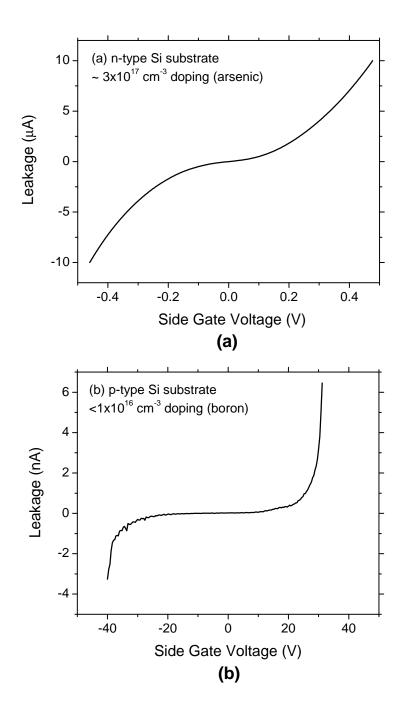

| 3.4  | I-V curves from the 2DEG Hall bar mesa through the SiGe buffers to                                       |    |

|------|----------------------------------------------------------------------------------------------------------|----|

|      | a back substrate contact for samples starting on (a) AW3H, a heavily                                     |    |

|      | n-type doped (arsenic) and (b) AW3L, a lightly p-type doped (boron)                                      |    |

|      | silicon substrates. Note the $\mu A$ scale in (a) and nA scale in (b)                                    | 39 |

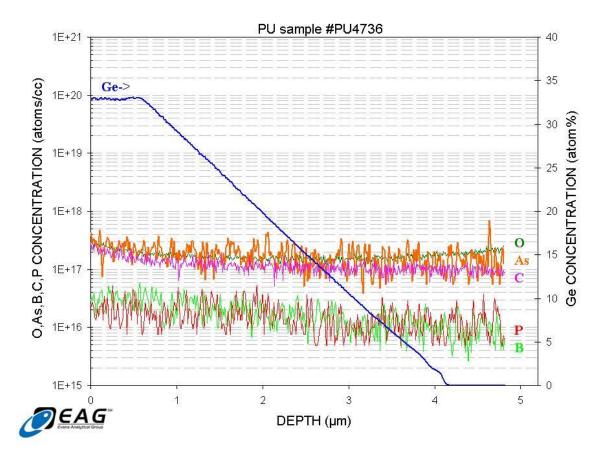

| 3.5  | SIMS analysis of AW3H substrate showing the starting Si substrate,                                       |    |

|      | the linearly graded SiGe buffer, and the uniform $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ buffer. The        |    |

|      | growth temperature of the relaxed SiGe buffer is over 1000 °C                                            | 41 |

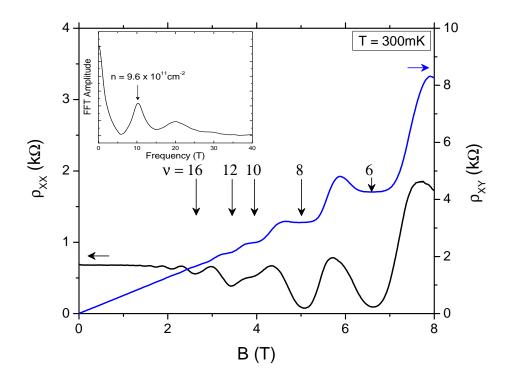

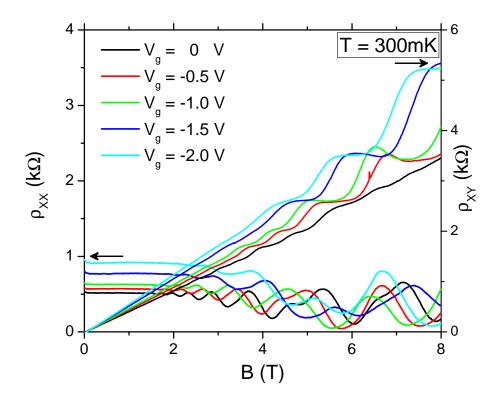

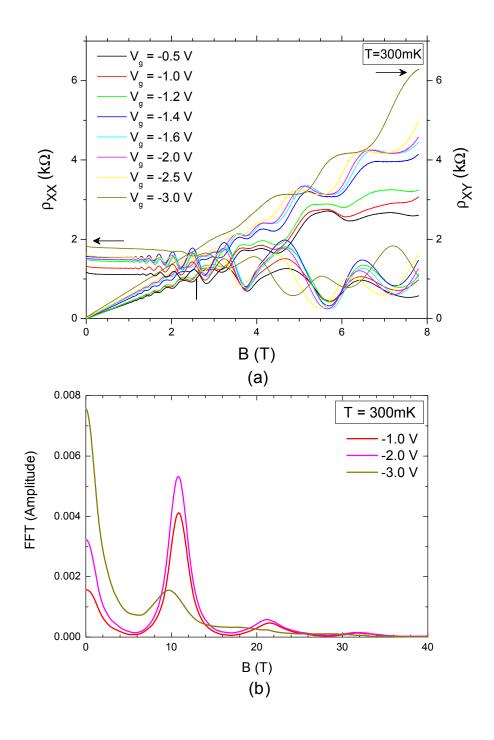

| 3.6  | Longitudinal resistance $\rho_{XX}$ and Hall resistance $\rho_{XY}$ vs. magnetic field                   |    |

|      | B at $T=300$ mK, showing the integer quantum Hall effect. The filling                                    |    |

|      | factor $\nu$ is marked by arrows. The inset shows the Fourier spectrum of                                |    |

|      | the longitudinal resistance                                                                              | 42 |

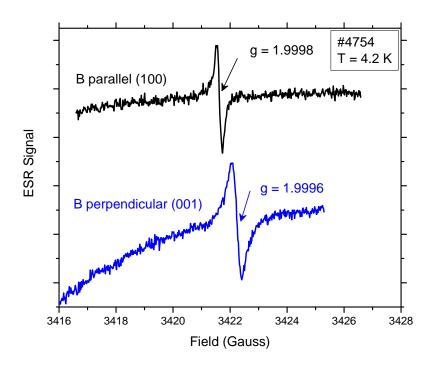

| 3.7  | The electron spin resonance spectrum of the Si 2DEG sample $\#4754$                                      |    |

|      | in both perpendicular and in-plane magnetic field                                                        | 45 |

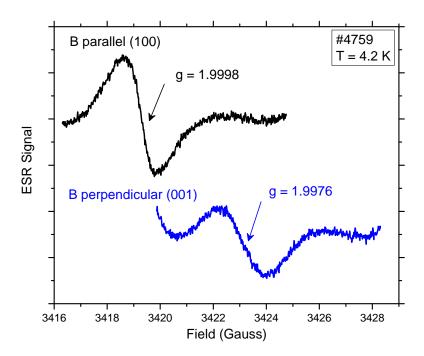

| 3.8  | The electron spin resonance spectrum of the $\mathrm{Si}_{0.95}\mathrm{Ge}_{0.05}$ 2DEG sample           |    |

|      | #4759 in both perpendicular and in-plane magnetic field                                                  | 46 |

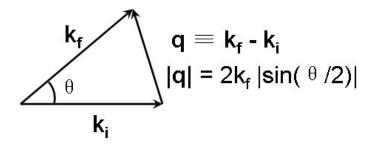

| 3.9  | Elastic scattering geometry in two-dimensions. $\mathbf{k}_i$ and $\mathbf{k}_f$ refer to the            |    |

|      | initial and final wave vectors. $\theta$ is the scattering angle                                         | 48 |

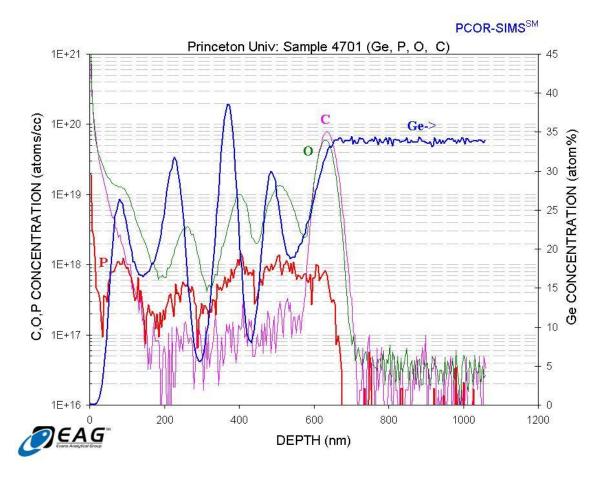

| 3.10 | SIMS analysis of sample $\#4701$ showing multiple Si quantum wells on                                    |    |

|      | $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ relaxed buffers. The growth temperatures for Si and SiGe            |    |

|      | are 625 $^{\circ}\mathrm{C}$ and 700 $^{\circ}\mathrm{C},$ respectively. The sample was not doped inten- |    |

|      | tionally with phosphorus                                                                                 | 52 |

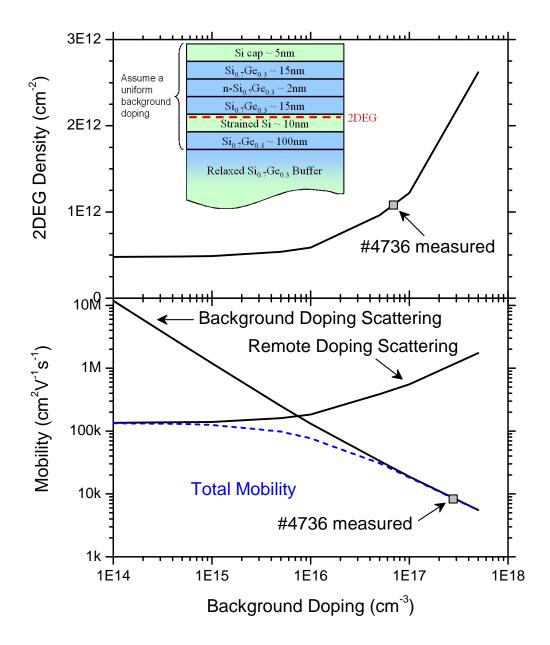

| 3.11 | Calculated 2DEG densities and electron mobilities limited by Coulom-                                     |    |

|      | bic scattering mechanisms vs. uniform background impurity levels.                                        |    |

|      | The inset shows the layer structures assumed in the calculation                                          | 53 |

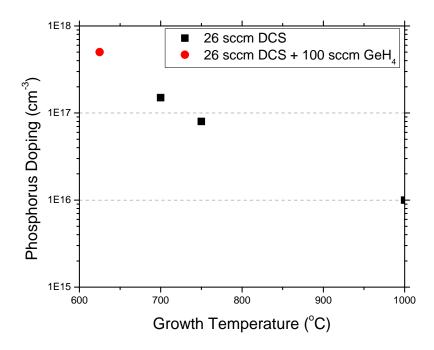

| 3.12 | Background phosphorus doping levels in Si and SiGe layers vs. growth                                     |    |

|      | temperature                                                                                              | 55 |

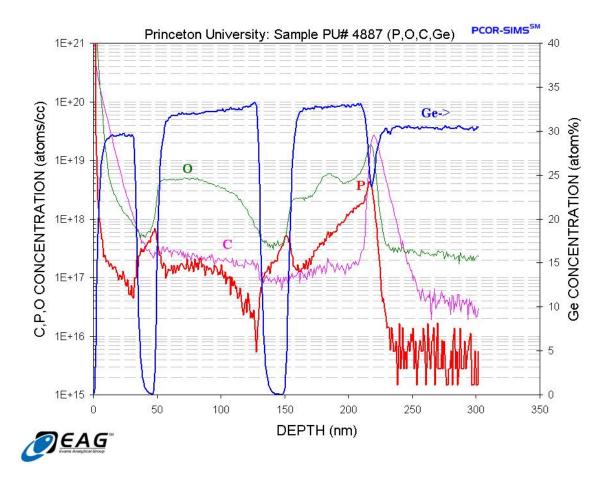

| 3.13 | SIMS analysis of sample #4887 showing multiple Si quantum wells on                             |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ relaxed buffers. The Si and SiGe layers are both grown at |    |

|      | 575 °C using $\mathrm{Si}_{2}\mathrm{H}_{6}$ as the silicon precursor                          | 56 |

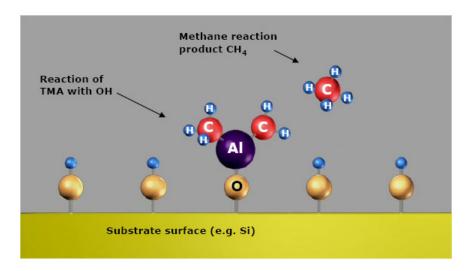

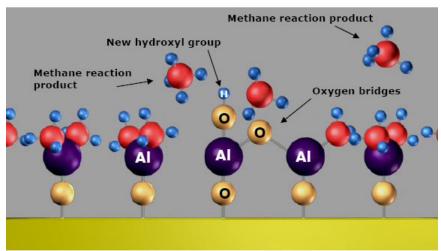

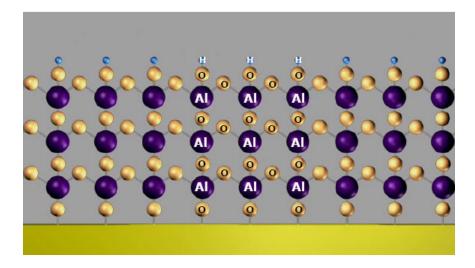

| 3.14 | ALD cycle for $Al_2O_3$ . Two reaction steps in each cycle as well as                          |    |

|      | completed monolayers are shown. (Image courtesy of Cambridge Nan-                              |    |

|      | oTech, www.cambridgenanotech.com)                                                              | 58 |

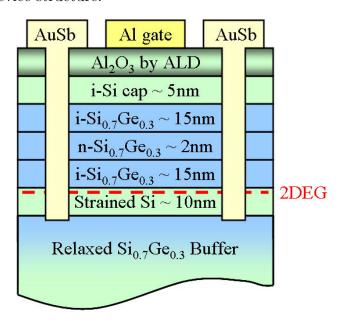

| 3.15 | Schematic view of an n-channel Si/SiGe MOSFET with ALD ${\rm Al_2O_3}$ as                      |    |

|      | gate dielectric                                                                                | 59 |

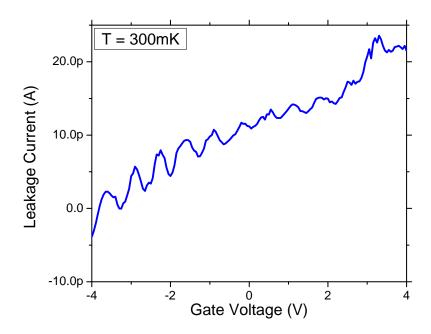

| 3.16 | Gate leakage current through the ALD ${\rm Al_2O_3}$ vs. applied voltage                       | 60 |

| 3.17 | Longitudinal resistance $\rho_{XX}$ and Hall resistance $\rho_{XY}$ vs. magnetic field         |    |

|      | at T = 300 mK, with an applied top-gate voltage $V_g$ from 0 to –2 V.                          | 61 |

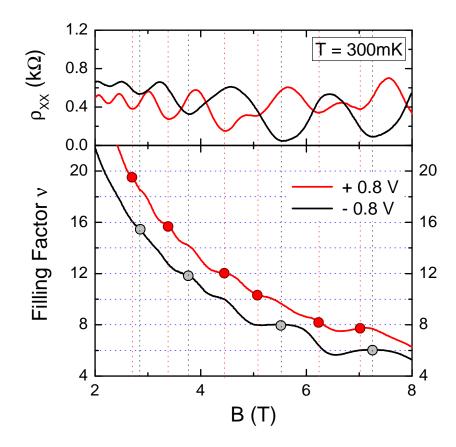

| 3.18 | Shubnikov-de Hass oscillations and quantum Hall effect at integer fill-                        |    |

|      | ing factors at $T=300$ mK, with applied top gate voltages of $+0.8$ and                        |    |

|      | -0.8 V                                                                                         | 62 |

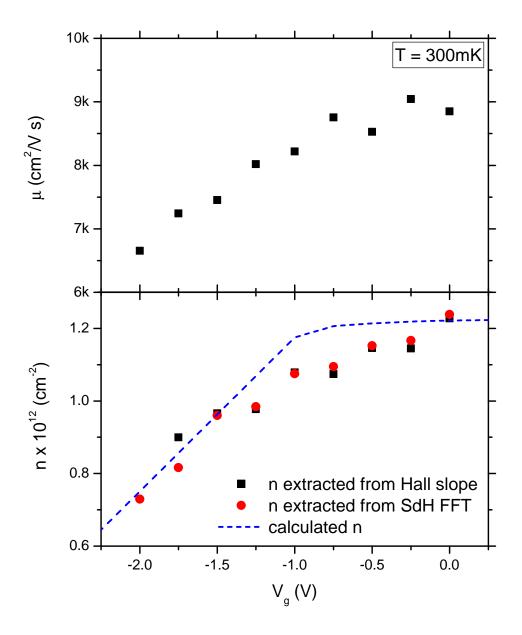

| 3.19 | 2DEG density and mobility vs. applied gate voltage at T = 300 mK.                              |    |

|      | Three methods for extracting the electron density are plotted: from                            |    |

|      | Hall slope, from SdH oscillation period, and from solution of 1-D Pois-                        |    |

|      | son's equation.                                                                                | 63 |

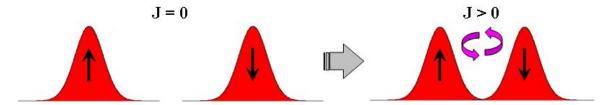

| 4.1  | Exchange interactions between two spin qubits: when $J=0$ , the two                            |    |

|      | qubits are uncoupled; when $J > 0$ , the two qubits are coupled and                            |    |

|      | two-qubit operations can be performed                                                          | 67 |

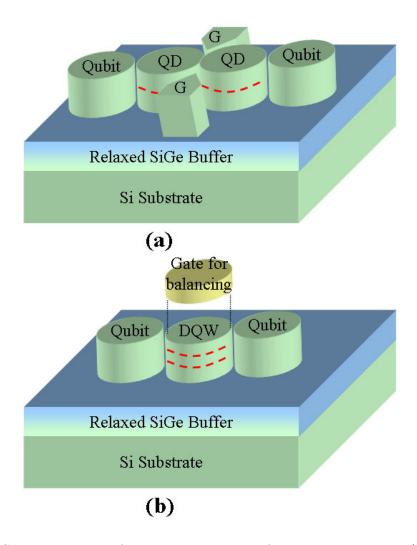

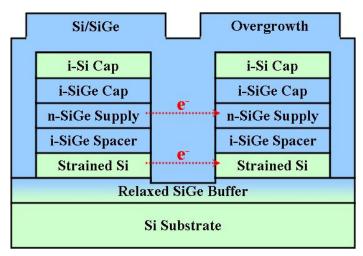

| 4.2  | Schematic view of two quantum dimer fabrication schemes: (a) a cou-                            |    |

|      | pled double quantum dot, the exchange coupling is controlled by two                            |    |

|      | side finger gates; (b) a single quantum dot of double quantum wells,                           |    |

|      | the exchange coupling is controlled by primarily the as-grown structure                        |    |

|      | of the DQW and not by a gate voltage                                                           | 68 |

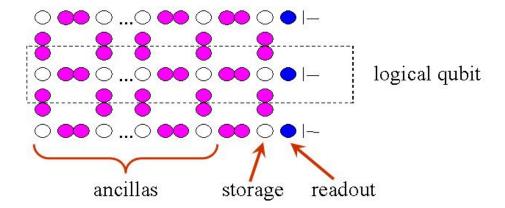

| 4.3  | The "flying architecture" map for a quantum computer. Each qubit                             |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | (white circle) is coupled to four identical qubits in the array via a                        |    |

|      | quantum dimer (adjacent pink circles)                                                        | 69 |

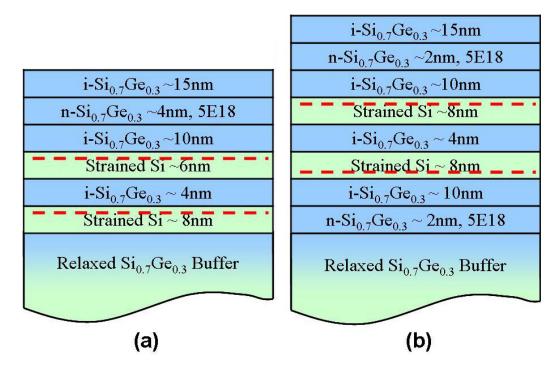

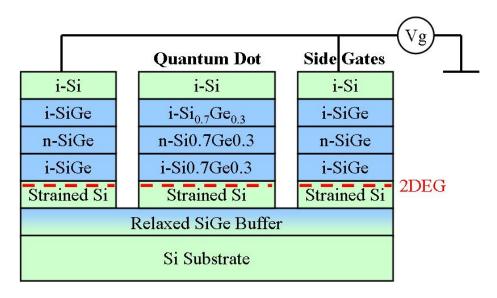

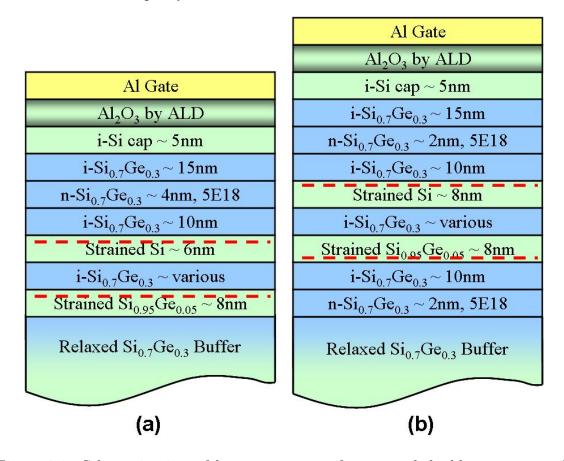

| 4.4  | Schematic view of layer structures of two double quantum well systems:                       |    |

|      | (a) asymmetric DQW with only one supply layer, (b) symmetric DQW                             |    |

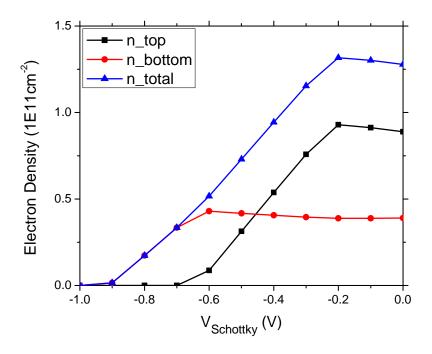

|      | with double supply layers. The red dashed line indicates a 2DEG. $$ .                        | 70 |

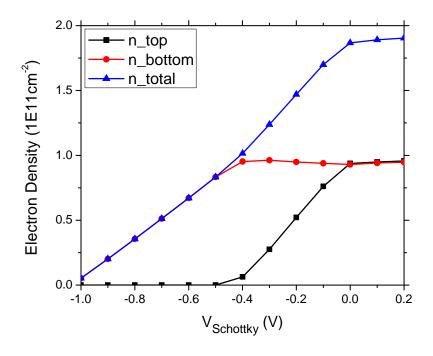

| 4.5  | Electron densities in asymmetric DQW system with different surface                           |    |

|      | Schottky barrier height applied                                                              | 71 |

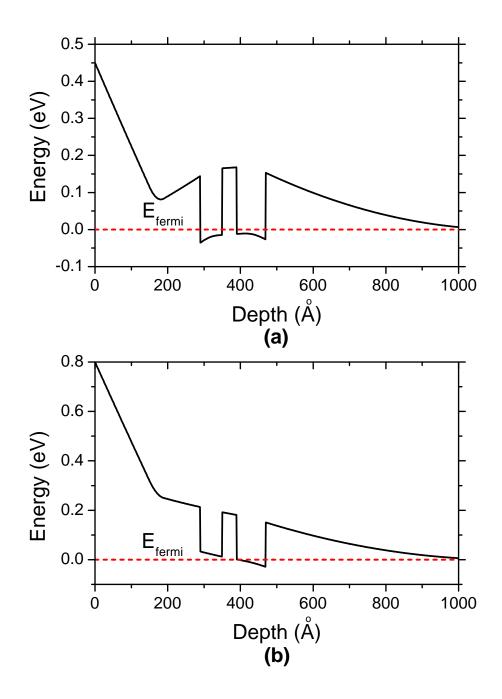

| 4.6  | Conduction band diagrams in asymmetric DQW design with surface                               |    |

|      | potentials at (a) $V_{Schottky} = -0.45 \text{ V}$ , (b) $V_{Schottky} = -0.8 \text{ V}$     | 73 |

| 4.7  | Electron densities in symmetric DQW system with different surface                            |    |

|      | Schottky barrier heights applied                                                             | 74 |

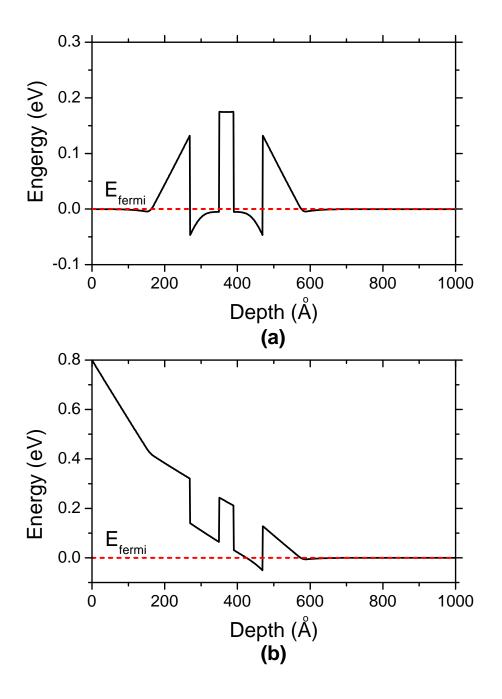

| 4.8  | Conduction band diagrams in symmetric DQW designs with surface                               |    |

|      | potentials at (a) $V_{Schottky} = 0$ , (b) $V_{Schottky} = -0.8 \text{ V.} \dots \dots$      | 76 |

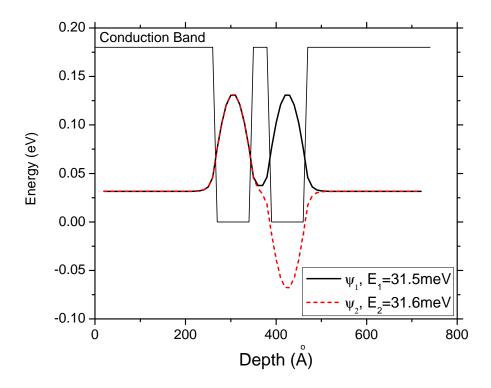

| 4.9  | The conduction band edge and the electron wave functions of the lowest                       |    |

|      | two quantized states in the symmetric double quantum well structures.                        |    |

|      | The strained Si conduction band is at $V=0.$                                                 | 77 |

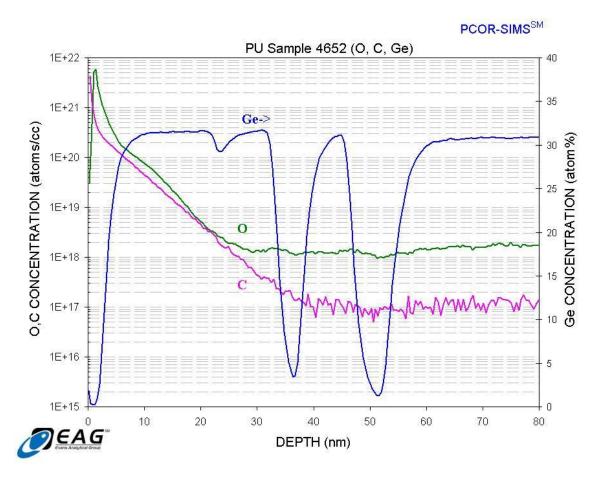

| 4.10 | SIMS analysis of an asymmetric double quantum well structure with a                          |    |

|      | 8nm barrier between the two wells                                                            | 79 |

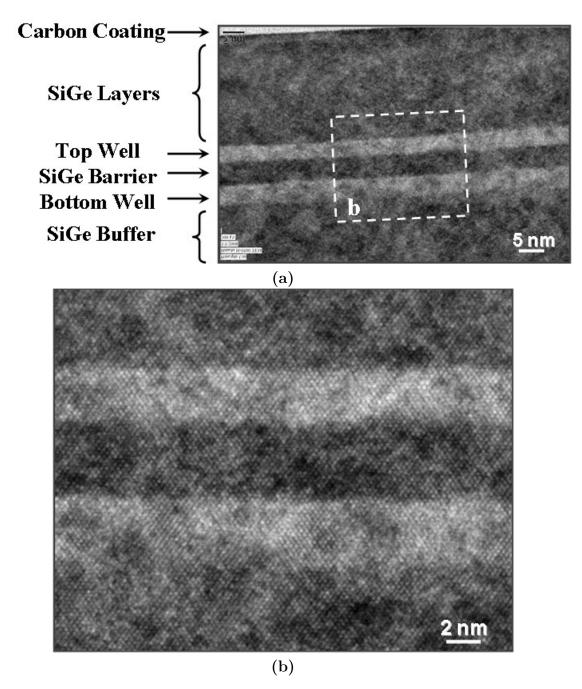

| 4.11 | (a) A cross section TEM image of an asymmetric double quantum well                           |    |

|      | structure on $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ relaxed buffers. (b) A high resolution TEM |    |

|      | image showing the Si/SiGe/Si double quantum wells. The TEM was                               |    |

|      | prepared by Dr. Nan Yao at Princeton and Hitachi laboratory, CA                              | 80 |

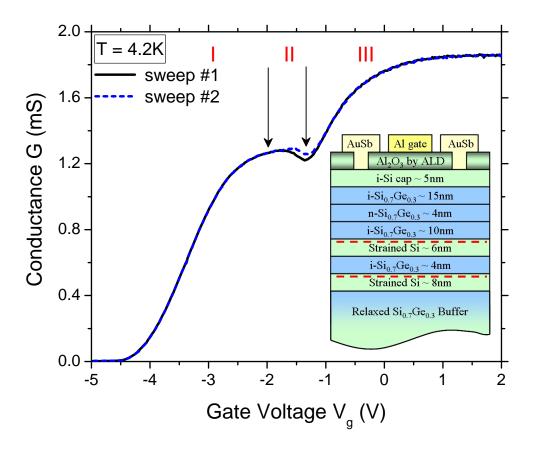

| 4.12 | The sheet conductance measured as a function of gate voltage at $T=$                         |    |

|      | 4 2 K                                                                                        | 82 |

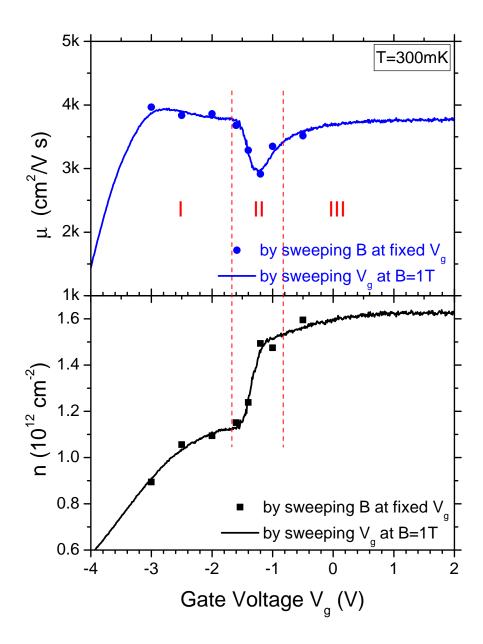

| 4.13 | DQW 2DEG density and mobility vs. applied gate voltage at $T = 300$                  |    |

|------|--------------------------------------------------------------------------------------|----|

|      | mK. The data were extracted from Hall slope and sheet resistance by                  |    |

|      | either sweeping the gate voltage at $B=1\ T$ or sweeping the field at                |    |

|      | certain fixed gate voltages                                                          | 83 |

| 4.14 | (a) Longitudinal resistance $\rho_{XX}$ and Hall resistance $\rho_{XY}$ vs. magnetic |    |

|      | field at T = 300 mK, with an applied top gate voltage Vg from $-0.5$                 |    |

|      | to $-3$ V. (b) The Fourier spectrum of the longitudinal resistance at Vg             |    |

|      | = $-1$ , $-2$ and $-3$ V                                                             | 85 |

| 5.1  | Schematic cross-section of side-gating structures for a 2DEG quantum                 |    |

|      | dot                                                                                  | 89 |

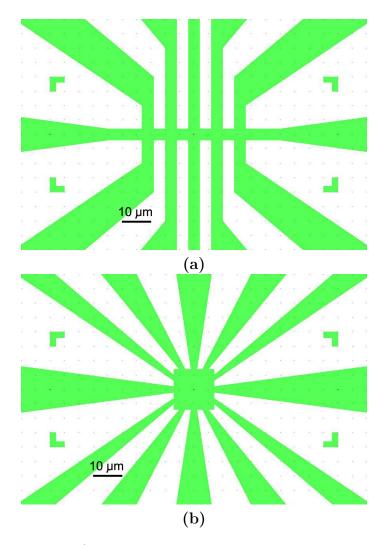

| 5.2  | Design view of optical photolithography masks with alignment marks                   |    |

|      | for (a) a Hall bar geometry for e-beam patterning of multiple quantum                |    |

|      | point contacts or gaps for leakage tests; (b) a symmetric square island              |    |

|      | geometry for complex quantum dot structures. The mask is designed                    |    |

|      | in L-Edit, Tanner EDA                                                                | 92 |

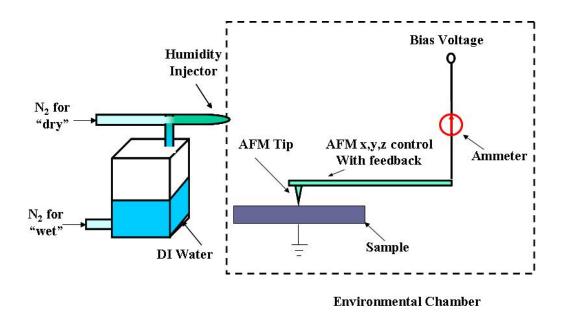

| 5.3  | The instrument setup for AFM lithography [91]                                        | 94 |

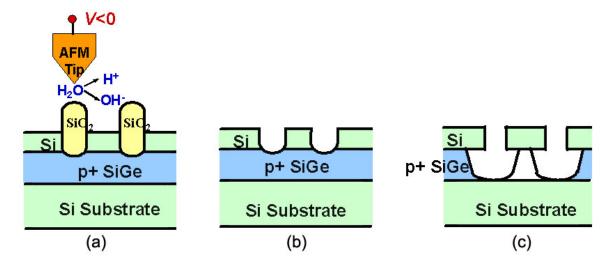

| 5.4  | Process of nanopatterning Si/SiGe layers with AFM lithography and                    |    |

|      | two-step wet etching: (a) AFM local oxidation, (b) Remove oxide by                   |    |

|      | HF, (c) SiGe selective wet etching                                                   | 95 |

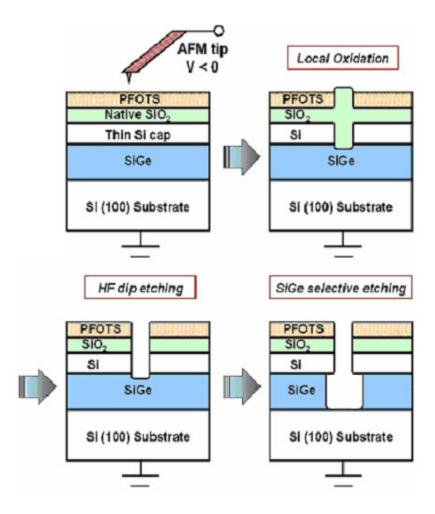

| 5.5  | Process of PFOTS-aided AFM lithography. PFOTS is deposited on                        |    |

|      | native oxide (for bonding) to prevent etching through 2-nm silicon                   |    |

|      | surface layer during SiGe patterning for improved uniformity. The                    |    |

|      | two-step etching process is used to pattern SiGe thicker than $\sim 2$ nm.           | 96 |

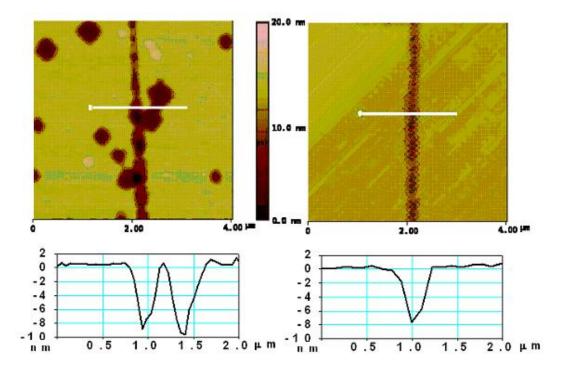

| 5.6  | Surface image and profile along the labeled white line for a Si/SiGe                 |    |

|      | pattern with (right) and without (left) PFOTS as a resist, the HF dip                |    |

|      | to remove silicon oxide and the SiGe selective wet etch for $\sim 40$ sec            | 97 |

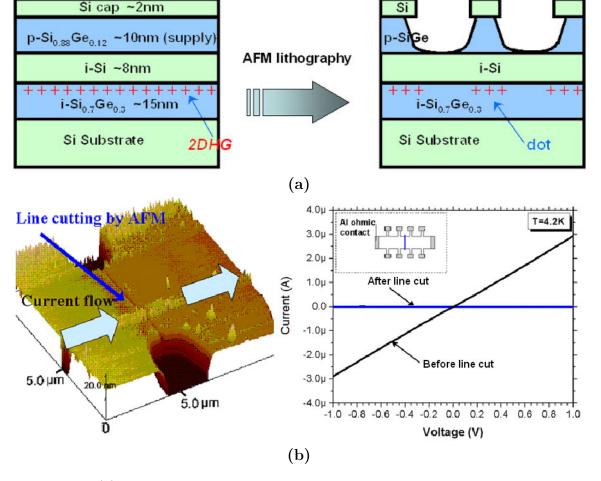

| 5.7  | (a) Schematic structures of the 2-D hole gas structure with $Sl_{0.9}Ge_{0.1}$                      |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | supply layer for patterning by AFM lithography; (b) AFM image and                                   |     |

|      | I-V curve of Hall showing conducting path cut by PFOTS-aided AFM                                    |     |

|      | lithography of supply layer and increased resistance at 4.2 K after the                             |     |

|      | cut                                                                                                 | 98  |

| 5.8  | Etch selectivity vs. Ge content with respect to Si for p-type SiGe etched                           |     |

|      | in $\mathrm{HF:H_2O_2:CH_3COOH} = 1:2:3$ . The etch rate data are obtained from                     |     |

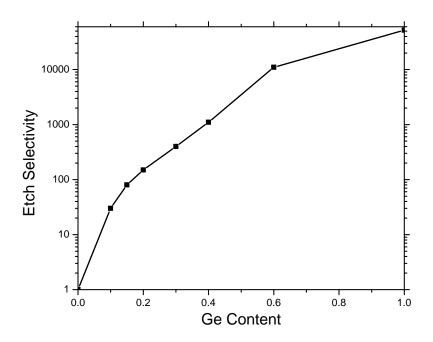

|      | [93]                                                                                                | 102 |

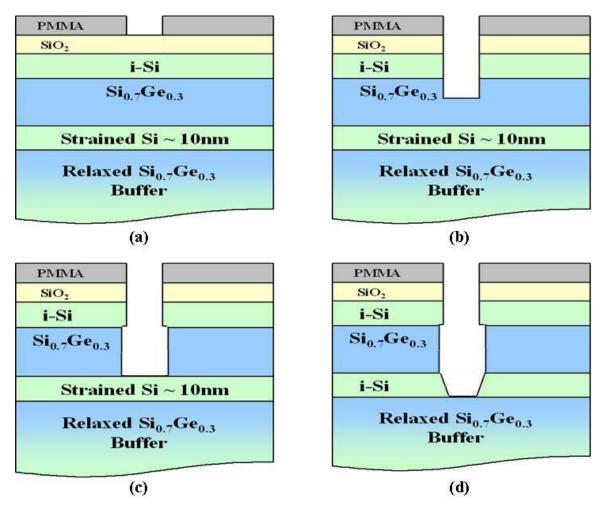

| 5.9  | Process of QPC in Si/SiGe heterostructure 2DEG fabricated by e-                                     |     |

|      | beam lithography and selective wet-etching. (a) E-beam lithography                                  |     |

|      | and development of PMMA; (b) a shallow RIE to remove $\mathrm{SiO}_2$ and $\mathrm{Si};$            |     |

|      | (c) SiGe wet etch; (d) Si wet etch                                                                  | 103 |

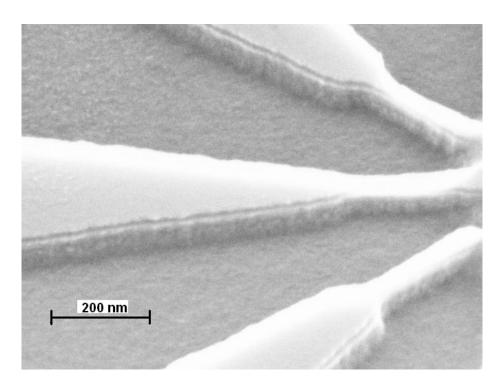

| 5.10 | A SEM image of Si/SiGe QPC after all etching steps and the removal                                  |     |

|      | of PMMA resist                                                                                      | 104 |

| 5.11 | SEM images of Si/SiGe structures etched by RIE using: (a) $\mathrm{Cl}_2/\mathrm{Argon}$            |     |

|      | gas mixtures; (b) $SF_2/CCl_2F_2$ gas mixtures                                                      | 106 |

| 5.12 | A SEM image of Si/SiGe quantum dot structure etched by RIE using                                    |     |

|      | $\mathrm{CF_4/O_2}$ gas mixture showing a straight sidewall profile and a clean                     |     |

|      | bottom surface                                                                                      | 108 |

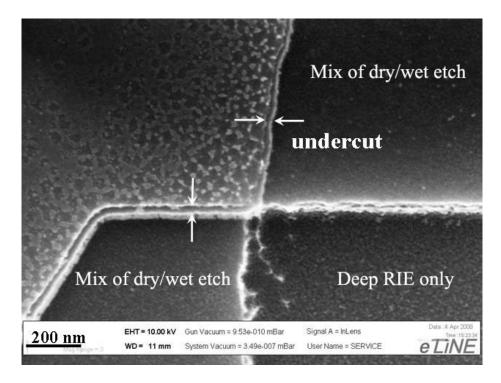

| 5.13 | A SEM image of Si/SiGe heterostructures etched by RIE using $\mathrm{CF_4/O_2}$                     |     |

|      | gas mixture and a subsequent 10-sec HF:<br>H $_2\mathrm{O}_2$ :<br>CH $_3\mathrm{COOH} = 1:2:3$ wet |     |

|      | etching. The finished under<br>cut features are marked by arrows                                    | 110 |

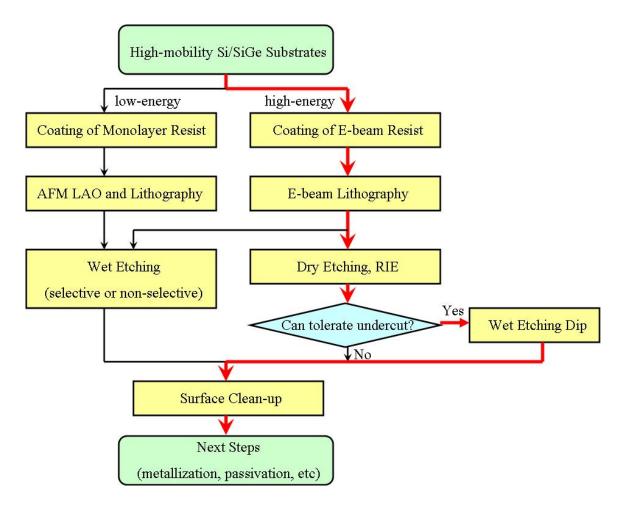

| 5.14 | Flowchart of the fabrication possibilities for quantum dot applications                             |     |

|      | combining different nanolithography and etching methods. Highlighted                                |     |

|      | (thick red) line gives the overall preference for quantum dot device                                |     |

|      | fabrication described in this thesis.                                                               | 112 |

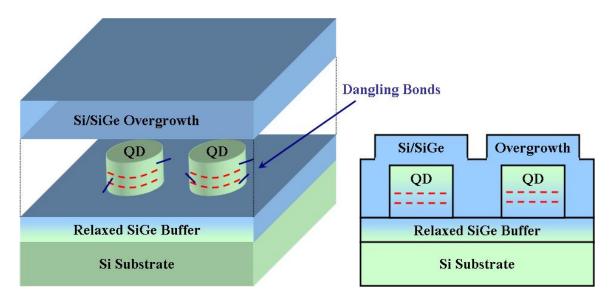

| 6.1 | Schematic of Si/SiGe quantum dot devices with SiGe epitaxial re-                                    |     |

|-----|-----------------------------------------------------------------------------------------------------|-----|

|     | growth. The regrowth ideally creates a coherent interface with no                                   |     |

|     | defect states                                                                                       | 114 |

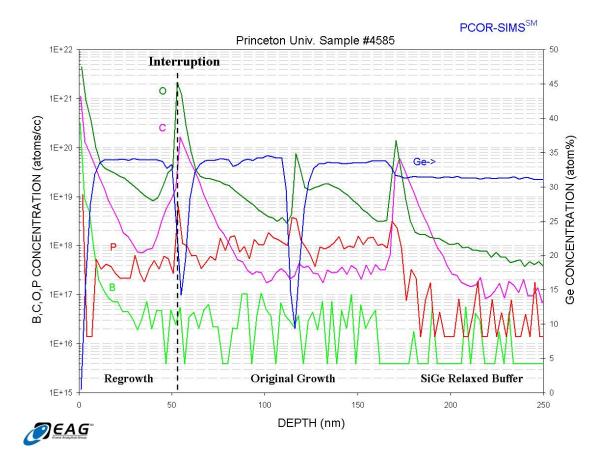

| 6.2 | SIMS analysis of sample #4585 with epitaxial $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ regrowth on a     |     |

|     | 2DEG in Si/SiGe on $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}$ relaxed buffers. The $in\ situ$ cleaning is |     |

|     | a 800 °C 3 slpm $H_2$ bake at 6 Torr for 4 minutes                                                  | 116 |

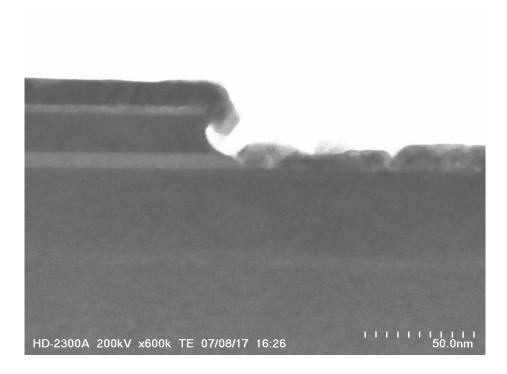

| 6.3 | A cross section TEM image a narrow gap etched in a 2DEG in Si/SiGe $$                               |     |

|     | on $\rm Si_{0.7}Ge_{0.3}$ relaxed buffers with Si/SiGe regrowth using chlorine etch-                |     |

|     | ing as a pre-clean step. The TEM was prepared by Dr. Nan Yao at                                     |     |

|     | Princeton and Hitachi laboratory, CA                                                                | 118 |

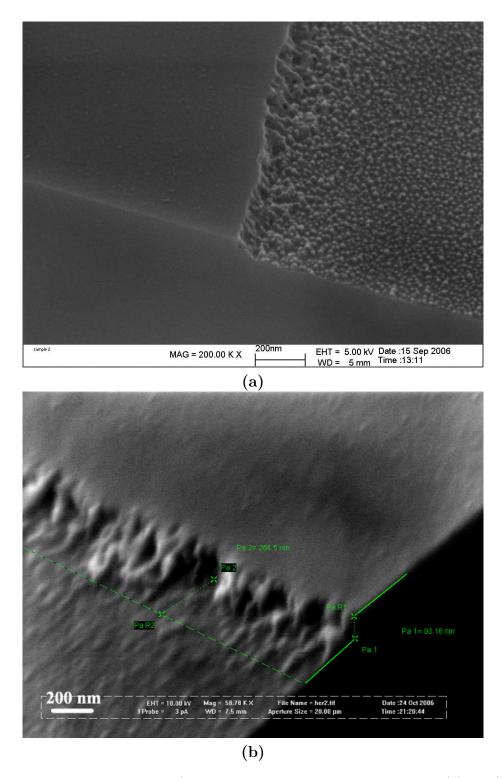

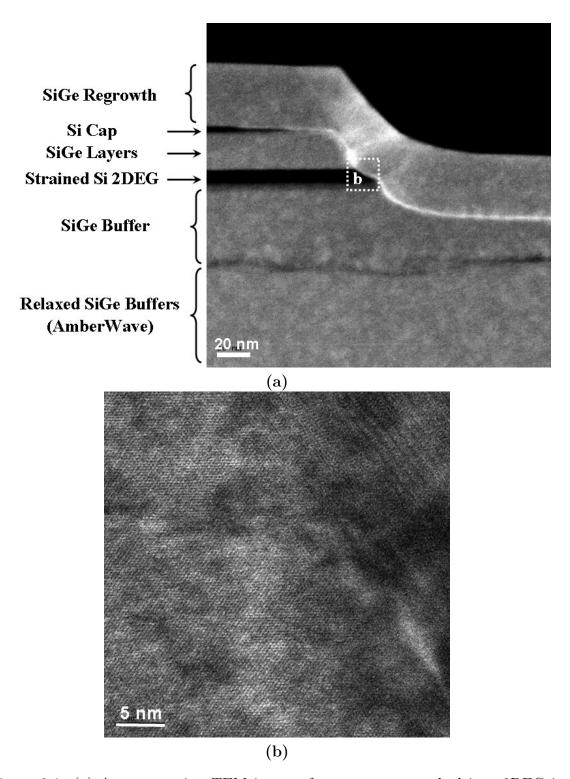

| 6.4 | (a) A cross section TEM image of a narrow gap etched in a 2DEG in                                   |     |

|     | $\mathrm{Si/SiGe}$ on $\mathrm{Si_{0.7}Ge_{0.3}}$ relaxed buffers with conformal epitaxial regrowth |     |

|     | on sidewalls. (b) A high resolution TEM image of the sidewall coverage,                             |     |

|     | showing that the regrowth over the sidewall is epitaxial. The TEM was                               |     |

|     | prepared by Dr. Nan Yao at Princeton and Hitachi laboratory, CA                                     | 120 |

| 6.5 | Schematic view of SiGe epitaxial regrowth over an etched 2DEG show-                                 |     |

|     | ing possible new leakage paths for electrons. (For example, from a side                             |     |

|     | gate to a laterally adjacent quantum dot.)                                                          | 123 |

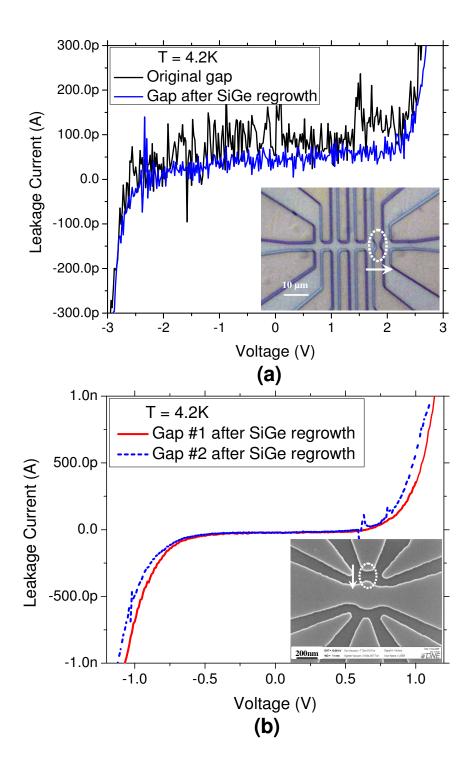

| 6.6 | I-V curves of the leakage current vs. gate voltage across narrow gaps of                            |     |

|     | (a) micron scale (2 $\mu m$ defined by optical lithography); (b) sub-micron                         |     |

|     | scale (100 nm defined by e-beam lithography)                                                        | 124 |

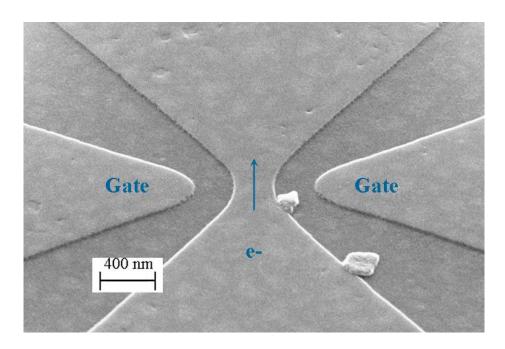

| 7.1 | A SEM image of Si/SiGe QPC patterned by low-damage wet etch and                                     |     |

|     | epitaxial dot passivation                                                                           | 130 |

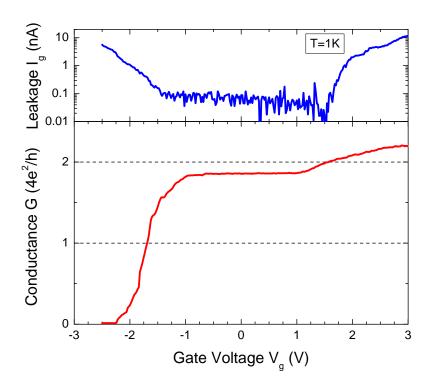

| 7.2 | Channel conductance and leakage current through the gate in a quan-                                 |     |

|     | tum point device as a function of the applied gate voltage at zero                                  |     |

|     | magnetic field                                                                                      | 131 |

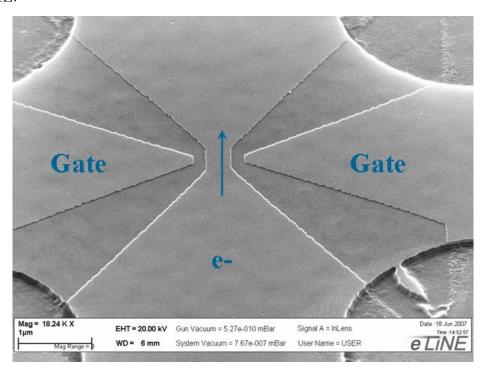

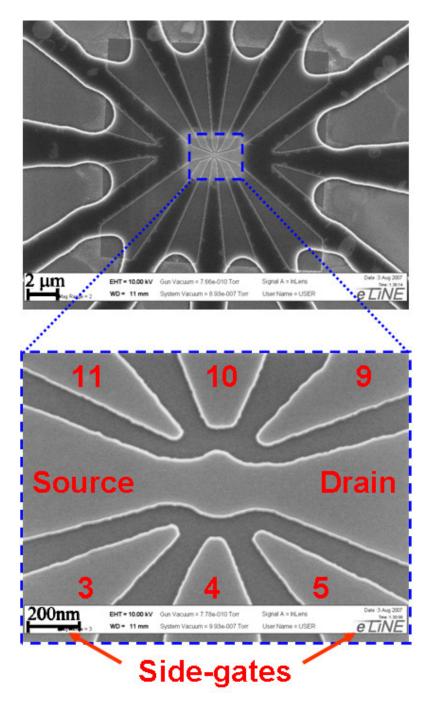

| 7.3 | A SEM image of a single Si/SiGe quantum dot with six side gates                     |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | patterned by RIE dry etch and epitaxial regrowth                                    | 133 |

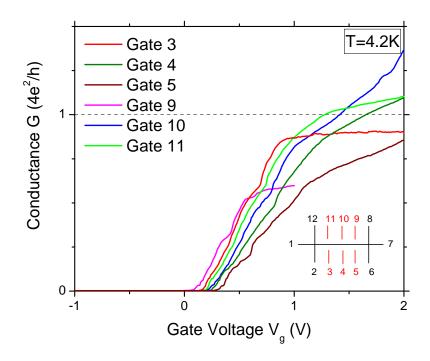

| 7.4 | Channel conductance in a quantum dot device at $T=4.2~\mathrm{K}$ as a              |     |

|     | function of the applied gate voltage at zero magnetic field. When a                 |     |

|     | voltage is applied to each individual gate, all other five side gates are           |     |

|     | held grounded                                                                       | 134 |

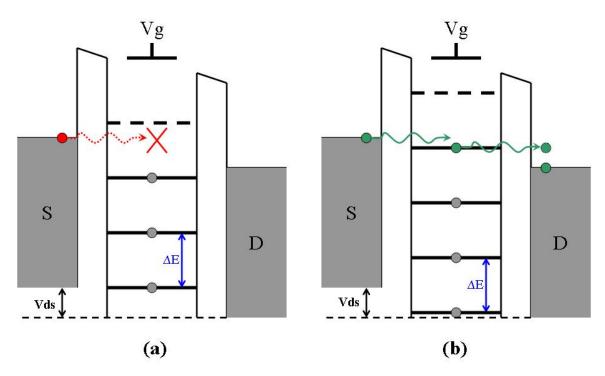

| 7.5 | Energy levels of a single quantum dot for (a) the blocking state, and               |     |

|     | (b) the transmitting state                                                          | 135 |

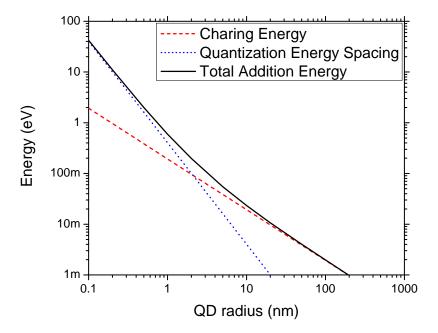

| 7.6 | Addition energy in a silicon quantum dot and its components of charg-               |     |

|     | ing energy and quantization energy spacing as a function of dot size                | 137 |

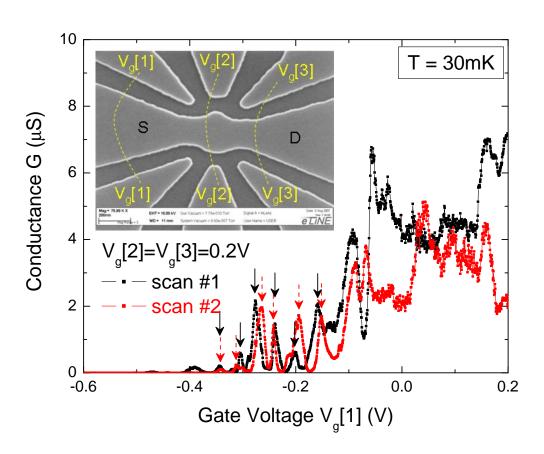

| 7.7 | Quantum dot conductance oscillations as the gate voltage on split gate              |     |

|     | $\mathrm{V}_g[1]$ is varied with zero magnetic field at T = 30 mK. The arrows indi- |     |

|     | cate the positions of conductance peaks that were included to calculate             |     |

|     | the gate capacitance                                                                | 139 |

| 8.1 | Schematic view of layer structures of two gated double quantum well                 |     |

|     | systems with one SiGe alloy well: (a) asymmetric DQW with only one                  |     |

|     | supply layer, (b) symmetric DQW with double supply layers                           | 146 |

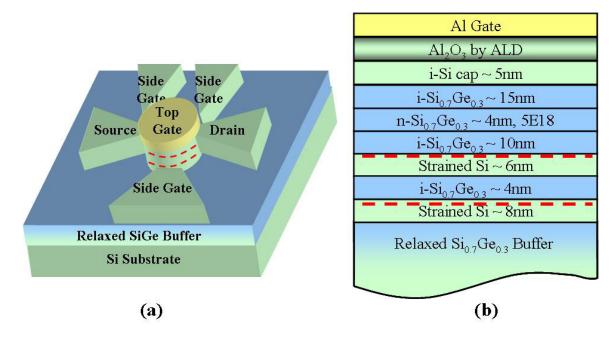

| 8.2 | (a) Top-view of a double quantum dot based interaction dimer device.                |     |

|     | (b) Schematic, cross-sectional view of the central quantum dot in the               |     |

|     | interaction dimer device                                                            | 147 |

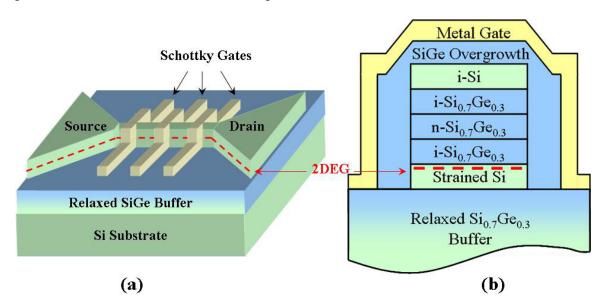

| 8.3 | (a) A multiple quantum dots device defined by Schottky finger gates                 |     |

|     | on a nanowire. (b) Schematic view of the Si/SiGe heterostructure                    |     |

|     | nanowire with epitaxial regrowth passivation.                                       | 148 |

Figure 1: Sensation: Interior View (2006) is an abstract sculpture by Jersey City artist Nancy Cohen that was inspired by discussions with Princeton University President Shirley Tilghman. Tilghman, a leader in the field of molecular biology, collaborated with Cohen and Princeton University Electrical Engineering Professor James Sturm on the artwork, which is an abstraction about the sense of smell and how odors are recognized and remembered. Multi-colored cast resin discs are affixed to a steel armature forming a wall that connects to bulb-shaped structures by vibrant wires. The different colors of discs represent the sensor neurons in the nose that detect different odorant molecules; the wires represent the axonal connections that pass through the skull to the olfactory bulb in the brain, with the neurons from each type of sensor going to their own specific region in the olfactory bulb. (Image courtesy of NSF, from NSF IPAMM final report, 2007)

## Chapter 1

#### Introduction

#### 1.1 Motivation

As the raw material of the information age, silicon has changed the world in a revolutionary fashion over the past 50 years. Interestingly, since silicon is similar to carbon, particularly in its valency, some people have proposed the possibility of silicon-based life. Life itself as we know it could not have developed based on a silicon biochemistry. However, the impact of silicon-based microelectronics on our life is apparent all around us. And the microelectronics universe itself is still expanding dramatically.

Moore's law has been the most important and most famous benchmark for developments in silicon technology. It describes that the number of transistors on a chip will double about every two years. The integrated circuit industry has kept that pace for nearly 40 years. As of today, Intel's next-generation Itanium processors will have 2-billion transistors [1]. CMOS scaling aggressively approximates the molecular scale in less than 10 years, transistors would eventually reach the limit of miniaturization at nearly atomic levels. Then the physical laws that govern the behavior and properties of the circuit will be inherently quantum mechanical in nature, not classical any more. On April 13, 2005, Gordon Moore himself stated in an interview that the law

cannot be sustained indefinitely [2]:

In terms of size [of transistor] you can see that we're approaching the size of atoms which is a fundamental barrier, but it'll be two or three generations before we get that far - but that's as far out as we've ever been able to see. We have another 10 to 20 years before we reach a fundamental limit. By then they'll be able to make bigger chips and have transistor budgets in the billions.

This is why we begin our journey at the level of atoms and electrons. Quantum computing, as its name suggests, may eventually allow computing to surpass the atomic level size restrictions. It represents the most promising possible final destination beyond the microelectronics roadmap. A quantum computer makes direct use of distinctively quantum mechanical phenomena to realize a fundamentally new mode of information processing. There are a number of quantum computing candidates, including those based on superconductors, Bose-Einstein condensates, quantum optics, and many others. Our work will focus on the "spintronic" quantum dot in silicon concept. This technology exploits the intrinsic spin of electrons and its associated magnetic moment, which is also the origin of the term "spintronics". A clear advantage of this route is that our experimental technique is compatible with existing complementary metal oxide semiconductor (CMOS) technology, making integration of quantum dots in silicon chips feasible.

#### 1.2 A Brief History of Quantum Computing

The idea of a computational device based on quantum mechanics was first explored in the 1970's and early 1980's by a small number of visionaries, such as Charles H. Bennett of the IBM Thomas J. Watson Research Center, Paul A. Benioff of Argonne National Laboratory in Illinois, David Deutsch of the University of Oxford, and

Richard P. Feynman of the California Institute of Technology. The idea of a quantum gate was introduced, the basic possibilities of quantum algorithms were set forth, quantum communication (in the form of quantum cryptography) was well developed, and some rudimentary ideas of how quantum computing could be implemented were considered.

In 1994, Peter Shor, a research and computer scientist at AT&T's Bell Laboratories in New Jersey, devised the first quantum algorithm [3]. Shor's algorithm harnesses the power of quantum superposition to rapidly factor very large numbers (on the order ~ 10<sup>200</sup> digits and greater) in a matter of seconds, much faster than is possible on conventional computers. With this breakthrough, quantum computing was transformed from a mere academic curiosity into a world interest. There is now a fast growing list of potential quantum tasks such as cryptography, error correcting schemes, quantum teleportation, etc. that show even more desirability of experimental implementations of quantum computing [4]. There is a remarkably long list of physical systems that have been proposed for potential realizations. Several significant experimental examples include: trapped ions [5], cavity QED [6], nuclear magnetic resonance [7], superconducting devices [8, 9, 10, 11, 12]. The Loss-DiVicenzo proposal that would use coupled quantum dot arrays as qubits [13] for a semiconductor-based quantum computer has attracted many researchers in solid-state physics field.

To consider how a practical quantum computer can be built, David DiVincenzo of the IBM Thomas J. Watson Research Center gave a simple list of five requirements: [14]

- 1. The machine should have a collection of qubits.

- 2. It should be possible to set all the memory bits to 0 before the start of each computation.

- 3. The error rate should be sufficiently low.

- 4. It must be possible to perform elementary logic operations between pairs of bits.

- 5. Reliable output of the final result should be possible.

To summarize the challenges from the perspective of an engineer, one needs to be able to build a physical system with a collection of well-characterized quantum two-level systems (qubits). Furthermore, the decoherence time of these qubits should be long (compared to the "clock time"), so that the qubits are to a high degree isolated from coupling to the environment so as to not decohere while performing operations on them. Electron spins in silicon are promising because of their long decoherence times, but electrical gating schemes for doable logic operations and measurements of individual qubits still seem challenging.

The Loss-DiVincenzo proposal uses the intrinsic spin of the electrons in coupled quantum dots as the basic carrier of information. Desired operations are effected by the gating of the tunneling barrier between neighboring dots. At this point, devices capable of quantum computing must be constructed so that theory can be put to test. This relies on simultaneous further advances in the experimental techniques of semiconductor nanofabrication, magnetic semiconductor synthesis, single electron electronics, and scanning probe techniques.

At present, quantum computing and quantum communication technology remains in its infancy, especially on the hardware side. However there is a vast amount of versatility as well. Eventually time will tell whether any of these efforts will actually provide a successful route to a quantum computer. Its future undoubtedly lies in the profound effect it will have on the lives of all mankind.

#### 1.3 Thesis Outline

Chapter 2 gives a brief review of the properties of the strained Si/SiGe heterostructures and the means to exploit the strain status in the layers for band engineering.

This chapter also contains details of Si and SiGe epitaxy at Princeton by rapid-thermal CVD (RTCVD).

Chapter 3 is dedicated to two-dimensional electron gas (2DEG) in modulation-doped Si/SiGe heterostructures, which is the physical embodiment of single electrons in quantum dots. Transport properties of electrons and modulation of heterojunction potentials are discussed. A theoretical model is studied to understand the limits on low-temperature electron mobilities.

In chapter 4 we extend our study to parallel 2DEGs in double quantum wells. Such a structure can serve as interaction dimer between two adjacent qubits in a "flying qubit" architecture for quantum computing. For this purpose, we investigate the band structures and the epitaxial growth of double quantum wells.

Chapter 5 presents a thorough review of quantum dot fabrication methods. Various nanolithography and etching methods are critically studied and compared. Examples of successful device applications are given. The expected limitations and benefits of different fabrication options are assessed.

Chapter 6 is focused on Si/SiGe epitaxial regrowth, a novel concept and technique for silicon-based quantum dot surface passivation with ideally zero defects and interface states. A low-temperature cleaning and growth sequence is developed to achieve conformal crystalline passivation over nanopatterned device surface on a wafer scale. This chapter also demonstrates the electrical compatibility of the regrowth technique with the existing 2DEG structures.

The growth, fabrication and epitaxial passivation techniques of Si/SiGe structures are the key to the realization of silicon-based quantum computer architectures. Chapter 7 covers the device aspects of these achievements. Simple quantum device applications including quantum point contact (QPC) and a single quantum dot are presented. We also discuss the possible role of such quantum devices in future quantum computers.

Finally in chapter 8 a summary of the contributions of this thesis is combined with a brief discussion of some possible future directions of research towards quantum computers.

## Chapter 2

# Si/SiGe Epitaxy

#### 2.1 Introduction

Silicon-based heterostructures have come a long way from the discovery of strain as a new and essential parameter for band structure engineering, to the present state of electron and hole mobilities enhancement which surpass those achieved in the traditional  $Si/SiO_2$  structures. Germanium can be considered as a kind of 'natural' choice for silicon-based heterostructures: the two group-IV elements silicon and germanium crystallize in the same diamond lattice, and form random  $Si_{1-x}Ge_x$  alloys of arbitrary composition. By means of these heterostructures, the band structure can be tuned within a wide margin. Table 2.1 lists the most important physical properties of silicon and germanium. In addition, their structural and chemical properties are very similar, which eases epitaxial growth and the application of standard Si CMOS technologies.

The obvious advantages of Si/SiGe heterostructures were recognized at an early stage of research, with the first report on a Si/SiGe superlattice appearing already back in 1975 [15]. After more than 30 years of research and development in this field, SiGe is commonly used as a strain-inducing layer for CMOS transistors in modern

Table 2.1: Selected physical properties of unstrained bulk silicon and germanium at room temperature.

|                                    |                | Silicon        | Germanium |

|------------------------------------|----------------|----------------|-----------|

| Crystal structure                  |                | diamond        | diamond   |

| Lattice constant (Å)               |                | 5.431          | 5.657     |

| Dielectric constant                |                | 11.9           | 16.2      |

| Direct bandgap (eV)                |                | 3.40           | 0.80      |

| Indirect bandgap (eV)              |                | $1.12(\Delta)$ | 0.66(L)   |

| Electron mass $(m_0)$              | $\mathrm{m}_t$ | 0.19           | 0.08      |

|                                    | $\mathrm{m}_l$ | 0.91           | 1.59      |

| Bulk mobility $(cm^2V^{-1}s^{-1})$ | Electrons      | 1450           | 3900      |

| (T = 300  K)                       | Holes          | 505            | 1800      |

technology. Since its introduction at the 90-nm node, strain has become a central performance enhancement element for the standard CMOS flow. With the scaling of the thickness of gate dielectric in silicon CMOS devices, channel mobility in MOS-FETs is trending towards lower values due to higher vertical fields [16]. Embedded SiGe source/drain (S/D) was first used in production for 65-nm PMOS. In the 45-nm method, the combined impact of higher Ge fraction in the embedded S/D and the strain enhancement from poly gate removal allow for a 1.5× higher hole mobility compared to 65-nm, despite the scaling of the transistor pitch (contact-poly-contact spacing) from 220 nm to 160 nm.

A key benefit of using SiGe in quantum computing applications comes from the Si/SiGe modulation-doped heterostructures. Modulation-doped structures were first conceived by Dingle in 1978 [17]. In such structures, the active layers consist of an undoped channel for the mobile carriers, an undoped spacer layer that separates the ionized dopants from the channel, and a doping layer. The carriers are confined at the heterojunctions to form a two-dimensional electron/hole gas (2DEG/2DHG). High mobilities are realized in the 2-D gas because the thick spacer layers significantly reduce Coulomb scattering at the ionized impurities of the doping layer. In the spin-qubit scheme for quantum computing we have considered, we are particu-

larly interested in quantum dots created by lateral confinement in a 2DEG. Because individual quantum states are accessible in such quantum dot, we can trap single electrons. The precise control of the electron number is accomplished using the well-documented Coulomb blockade effect.

#### 2.2 The Strained Si/SiGe Heterostructures

#### 2.2.1 Structural Properties

As the lattice constant of germanium is about 4.2% larger than that of silicon, the lattice constant of a bulk SiGe alloy can be estimated by Vegard's rule which uses a linear interpolation of the parameters of the end-point elements of Si and Ge:

$$a(Si_{1-x}Ge_x) = a(Si) + [a(Ge) - a(Si)]x,$$

(2.1)

where x represents the fraction of germanium atoms.

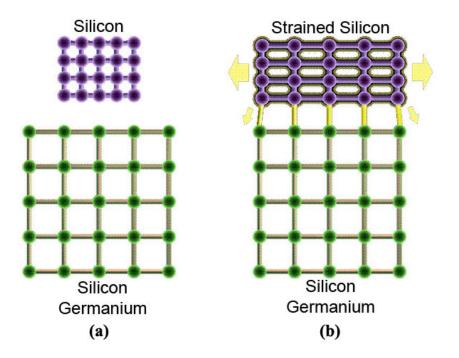

Let's first consider the case that a layer of pure silicon is deposited on top of bulk SiGe alloys. When the silicon film is thin, the in-plane silicon lattice tries to stretch and line up with the SiGe. The thin pseudomorphic (meaning that lattice mismatch is accommodated by strain in the thin film on a lattice-mismatched substrate) silicon becomes tensilely "strained". Fig. 2.1 illustrates the formation of such strained thin films.

The thin films cannot relax, because the elastic energy stored in such a homogeneously strained layer is lower than the elastic energy associated with the local distortion around a misfit dislocation. Also as a result of the strain, the perpendicular lattice constant of the silicon,  $a_{i\perp}$ , will decrease:

$$a_{i\perp} = a_i \left[ 1 - D^i \left( \frac{a_{i\parallel}}{a_i} - 1 \right) \right], \tag{2.2}$$

Figure 2.1: Schematic lattice structure of thin silicon deposited on silicon germanium substrate: (a) the SiGe lattice constant is larger compared to that of bulk Si; (b) the pure Si lattice attempts to line up with the SiGe lattice, which causes the Si to become tensilely strained. (Image courtesy of IBM, www.ibm.com)

where  $a_i$  denotes the cubic (unstrained) lattice constant of the film, and  $D^i$  is a constant that depends only on the elastic constant  $c_{11}^i$  and  $c_{12}^i$  of the respective material (in the above case, silicon):

$$D_{(001)}^i = 2\left(\frac{c_{12}}{c_{11}}\right). (2.3)$$

So far we have discussed in detail the heterostructures of stained Si on SiGe. The argument for thin pseudomorphic SiGe layers deposited on Si bulk is very similar, except for that SiGe layers are under compressive strained to maintain pseudomorphic bonding with the Si substrate.

It has been shown in Fig. 2.1 that in order to exploit strained silicon, the strain-defining SiGe substrate has to be realized. Bulk SiGe can be ruled out, both because of the growth problems of pulling homogeneous SiGe crystals, and because such substrates would jeopardize the Si/SiGe system's compatibility with existing silicon tech-

nologies. It is necessary to employ silicon substrates and grow a relaxed, intermediate SiGe buffer layer.

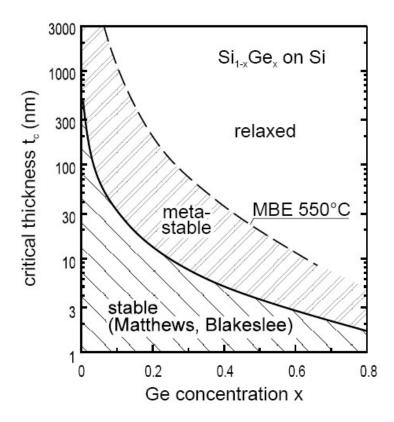

For relaxed buffers as well as for pseudomorphic layers the most relevant material parameter is the critical thickness  $t_c$  [18], an equilibrium parameter at which strain relaxation by the generation of misfit dislocations can commence. When the strained film thickness exceeds  $t_c$ , misfit dislocations become energetically favorable, and provide partial strain relaxation of the film. By using low-temperature epitaxy techniques, such as molecular beam epitaxy (MBE) or chemical vapor deposition (CVD), one can also grow pseudomorphic SiGe films above the equilibrium critical thickness on bulk Si. This is because a metastable range exists in which the nucleation and propagation of misfit dislocations is kinetically suppressed. Fig. 2.2 shows the three regimes labeled 'stable', 'metastable' and 'relaxed' as a function of Ge fraction x [19].

However, as there are many nucleation sites from the threading dislocations in a relaxed "virtual" substrate, in practice there is little metastable critical thickness for heterostructures grown on such substrates, such as tensilely strained silicon on relaxed SiGe buffers on a silicon substrate.

#### 2.2.2 Band Alignment

For the very large-scale integration (VLSI) community, the whole point of growing heterostructures is the opportunity to manipulate the behavior of carriers through band engineering. The bands of Si and SiGe alloys are strongly affected by strain, and experimental data are available both for unstrained bulk SiGe alloys and for pseudomorphic compressively strained SiGe films on Si(100) substrates. The strain-induced heavy-hole/light-hole splitting also leads to a splitting of the valence band in strained SiGe. Fig. 2.3 shows the bandgap values against Ge fraction x [20].

This thesis is focused on strained Si on SiGe relaxed buffer heterostructures. The

Figure 2.2: [19] Critical thickness against fraction for  $Si_1 - xGe_x$  on Si. The lowest curve gives the theoretical limit in thermal equilibrium, whereas the experimental curve is for a metastable layer grown at 550 °C by MBE.

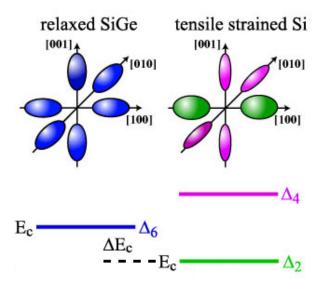

pseudomorphic Si/SiGe interface is commonly used as a quantum well to confine electrons. Such Si/Si<sub>1-xs</sub>Ge<sub>xs</sub> heterojunctions are of type II for all value of  $x_s$ . Fig. 2.4 illustrates the valley splitting and allows predictions for arbitrary Si/SiGe heterojunctions with respect to band ordering and band offsets [19]. Throughout this thesis we will discuss the Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> system unless a different  $x_s$  is specified. A complete description of the band alignment can be calculated based on the local density functional and *ab initio* pseudopotentials [22]. In summary, the hydrostatic strain component leads to an overall downward shift of the average valence band and lowers the  $\Delta$  and L band energies. The uniaxial strain component only splits the  $\Delta$  conduction bands and the degenerate light/heavy hole valence band edges and leaves the weighted average positions of these bands unaffected. For the conduction band,

Figure 2.3: [20] Summary of energy-gap values of SiGe alloys, both unstrained bulk and strained SiGe on Si(100) substrate, at 90 K after correcting for quantum well shifts (circles = 75Å wells; triangles = 33Å wells). The double points at the same values of x correspond to a splitting of the valence band. The unstrained bulk alloy data are from optical absorption measurement by Braunstein [21].

the six-fold valley degeneracy in bulk silicon is lifted. The overall lowest conduction band is always the  $\Delta_2$  level in the active Si layer. Analytical fittings for the band offsets that will be used for numerical simulations can be expressed as [23]

$$\Delta E_v(x_s) = -0.238x_s + 0.03x_s^2, (2.4)$$

$$\Delta E_c(x_s) = -0.35x_s - 0.35x_s^2 + 0.12x_s^3, \tag{2.5}$$

where  $x_s < 0.85$ , the negative signs indicate that the conduction and valence bands of strained Si are lower than those of the relaxed  $Si_{1-x_s}Ge_{x_s}$  substrate.

Figure 2.4: (a) The splitting of Si conduction bands in tensilely strained Si/SiGe heterostructures. (b) [19] Variation of the relevant silicon conduction and valence bands of a tensilely strained Si/SiGe heterostructure as a function of relaxed SiGe substrate composition  $x_{sub}$ .

The strain-induced band alignment also has strong effects on electron transport in strained silicon. The high electron mobilities realized in Si/SiGe heterostructures are of great interest for application in high performance CMOS as well as for quantum computation. The mechanism of mobility enhancement is well understood. For tensilely strained Si on SiGe substrate, the conduction band minimum lies in the silicon  $\Delta_2$ . At low temperatures, the electrons only populate in the lower minima. The in-plane effective mass is now reduced to the transverse effective mass, which is only

$$m^* = m_T = 0.19 \ m_0. \tag{2.6}$$

Besides the lower in-plane effective mass, the lifting of degeneracy also helps suppression of intervalley scattering. The enhanced electron mobilities and as a result, enhanced mean free paths in these structures have made a variety of transport physics experiments possible. One prominent example is the observation of the fractional quantum hall effect (FQHE) in an n-type Si/SiGe heterostructure [24]. To date, the highest low-temperature electron Hall mobility ever reported in strained Si is around  $8.0 \times 10^5$  cm<sup>2</sup>/Vs [25]. This has approached those in the GaAs/AlGaAs system to within a factor of 50. At room temperature, however, phonon scattering dominates and generally muffles the mobility. Still a 2DEG enhances the mobility by almost a factor of two over that of pure bulk silicon (2600 vs. 1450 cm<sup>2</sup>/Vs) [26].

# 2.3 Si and SiGe Epitaxy at Princeton

# 2.3.1 Overview of the RTCVD Epitaxy

The Si/SiGe epitaxy for this thesis was performed in a custom-built rapid thermal chemical vapor deposition (RTCVD) apparatus at Princeton [27]. The reactor includes a load-locked, cold-wall quartz tube. A 100-mm silicon wafer is loaded and

supported by a quartz stand. It is heated from underneath by a bank of twelve 6-kW tungsten-halogen lamps. The process gas flows are adjusted by mass flow controllers. Three silicon precursors are available: dichlorosilane (or DCS, SiH<sub>2</sub>Cl<sub>2</sub>), silane (SiH<sub>4</sub>, 10% in argon mixture), disilane (Si<sub>2</sub>H<sub>6</sub>, 10% in hygrogen mixture). Germane (GeH<sub>4</sub>, 0.8% in hydrogen mixture) is used as the germanium precursor. Diborane (B<sub>2</sub>H<sub>6</sub>, 20 ppm diluted in hydrogen) and phosphine (PH<sub>3</sub>, 100 ppm diluted in hydrogen) are added for *in situ* doping in both Si and SiGe growth. Unreacted exhaust gases are handled by a burnbox/scrubber equipment. The burnbox operates at around 850 °C to assure a thorough oxidation of the effluent. The hot treated gases are passed through a water recirculation tank for cooling and removal of residual reactor gases and particles.

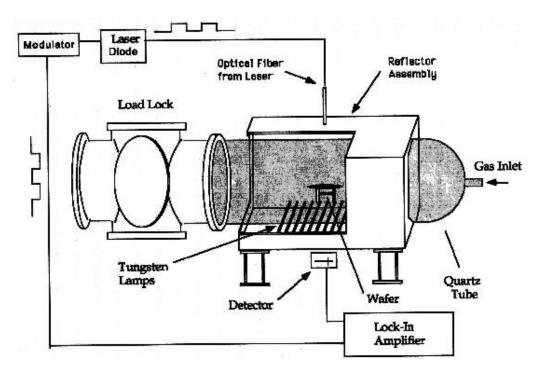

Figure 2.5: Schematic of Princeton RTCVD system used in this thesis. (Image courtesy of P. V. Schwartz [28])

Typical epitaxial growth conditions are at a pressure of 6 Torr with 3 standard liters per minute (slpm) hydrogen carrier flow. Under these conditions the growth surface is hydrogen-terminated. In this susceptor-free reactor, the silicon temperature

is measured by infrared absorption [29]. Two semiconductor lasers at 1.30 and 1.55  $\mu$ m are coupled into a common fiber. The transmission is measured using lock-in amplifier techniques. A feedback loop controls the lamp power for accurate temperature control. The RTCVD system has been shown capable of growing high quality Si/SiGe layers on a 100 Å scale with an interface abruptness on the order of 10 Å, which is essential for quantum computing applications. Next we will discuss the Si/SiGe epitaxial RTCVD growth in more details, as well as to learn the prospects and limitations of this system.

# 2.3.2 The Use of Commercially-available SiGe Relaxed Buffers

We obtained our SiGe relaxed buffer from AmberWave Systems (see also www. amberwave.com), one of the semiconductor industry's leading suppliers of strained silicon technology. From the perspective of epitaxial growth, the growth conditions of relaxed buffers of a few microns thick and the thin modulation-doped layers can be quite different. High temperatures typically above 1000 °C are desirable for relaxed buffer growth to enable simultaneous improvements in both dislocation density and growth rate. The growth optimization is focused on high throughput on a large wafer scale. In contrast, optimization for the growth of high-mobility heterostrucures often leads to a contrary requirement. The layers are usually grown at low temperatures ( $\sim$ 550 - 750 °C) for precise control of the thin layer thickness and interface abruptness. The typical sample dimension is around 1 cm for magneto-transport experiments at liquid helium temperatures. Therefore, it is difficult for a single system to grow both SiGe relaxed buffers and the modulation-doped heterostructures. We are among the first to use commercially available SiGe relaxed buffers for Si/SiGe modulationdoped heterostructures in academic research. The suitability of such applications is demonstrated.

Figure 2.6: [30] Effect of temperature on AmberWave graded buffer threading dislocation density (TDD) and dislocation pileup density (DPD), determined by etch pit density and plan view TEM, respectively.

AmberWave Systems has developed a novel, high quality SiGe graded buffer growth process using GeCl<sub>4</sub> [30]. The use of the new germanium precursor enabled previously unattainable growth temperatures and growth rates. The chlorine component also can reduce parasitic deposition on the reactor chamber walls. Fig. 2.6 shows the effect of temperature in their system while maintaining high growth rates. Normally their growth procedure is as follows:

- 1. Start with 200-mm silicon substrates, either heavily or lightly doped depending on the applications;

- 2. Grow an undoped linearly-graded SiGe buffer at 10% germanium per micron;

- 3. Grow an undoped SiGe cap layer at the final Ge content, approximately 2  $\mu$ m thick;

- 4. (optional) Chemical mechanical polishing (CMP) of the surface, to remove cross-

hatch roughness.

In this work three kinds of SiGe relaxed buffers from AmberWave Systems were used. Table 2.2 summarizes the parameters of these buffers. The use of CMP to eliminate cross-hatch patterns on relaxed SiGe buffers is illustrated in Fig. 2.7. The polished surface has a roughness RMS of 5.7 Å which is about ten times smoother than the as-grown surface. However the surface roughness has nearly no measurable effect on the quality of quantum wells growth on top, the electrical quality of quantum well samples grown on polished and unpolished buffers from the same growth were identical.

Table 2.2: Summary of AmberWave Systems SiGe relaxed buffers.