Contributions of DOE Weapons Labs and NIST to Semiconductor Technology

September 1993

OTA-ITE-585 NTIS order #PB94-134632 GPO stock #052-003-01349-5

#### **Recommended Citation:**

U.S. Congress, Office of Technology Assessment, *Contributions of DOE Weapons Labs and NIST to Semiconductor Technology, OTA-ITE-585* (Washington, DC: U.S. Government Printing Office, September 1993).

Foisale 6) the Us (lovernment Printing Office Superintendent of Documents, Mail Stop SSOP, Washington, DC 20-1 (J2 9328 ISBN 0-16 -042095-4

### Foreword

he federal laboratories of the United States are a diverse lot. For those whose primary function was advancing military technologies, the end of the Cold War has meant reexamination of missions, abilities, and resources on a scale grander than anything that has occurred in decades. In particular, the Department of Energy's nuclear weapons laboratories (Lawrence Livermore, Los Alamos, and Sandia National Laboratories) are under close examination. Throughout their existence, the weapons labs' primary missions have involved nuclear weapons. One of the most important is nuclear weapons development, and that function has diminished considerably as a result of the end of the Cold War. While other weapons-related missions remain important, a consensus has emerged that the labs are, in a sense, larger than their remaining missions warrant. But the issue is much larger than simply how much to cut and how to manage the reduction.

National security is still the issue, but defined more broadly than in the past, when it was confined to military security. The concept of national security is now expanding to include industrial competitiveness, and there is lively interest in examining how all the labs in the federal system could contribute to advancing science and precommercial technology. The debate over whether and how to expand the missions of the DOE labs has also raised questions of how to coordinate these new activities with those of labs and agencies that already have responsibility for civilian technology policy—principally the National Institute of Standards and Technology of the Department of Commerce. NIST has emerged in the last few years as one of the federal government's major players in civilian technology advancement through, for example, management of the new and well-regarded Advanced Technology Program.

This Report examines how NIST and DOE weapons laboratories could contribute to advances in semiconductor technology aimed specifically at civilian applications. Semiconductor technology was chosen as an example of a technology focus for a civilian technology initiative, primarily because the industry had already developed a set of comprehensive technology roadmaps and the federal labs had substantial expertise in the area. The Report was requested as a follow-on assessment to OTA's work on the implications for the U.S. civilian economy of the end of the Cold War. That work consists of two Reports: *After the Cold War: Living With Lower Defense Spending*, and *Defense Conversion: Redirecting R&D*. The former considered the effects on defense workers, defense-dependent communities, and defense companies, and suggested policy options to ease transitions for those affected by cutbacks. The latter examined how the R&D institutions whose primary missions were defense-related could contribute to national well-being under a broader concept of national security.

Roger C. Herdman, Director

# Laboratory Review Panel

**A.S. Oberai** *Chairman* Consultant

Graham Alcott Intel Corporation

**Charles Fowler** U.S. Department of Energy

Sam Harrell SEMATECH

William C. Holton Semiconductor Research Corporation John F. Holtzrichter Lawrence Livermore National Laboratory

Paul M. Horn IBM T.J. Watson Research Center

Ross A. Lemons Los Alamos National Laboratory

Zachary Lemnios Advanced Research Projects Agency

Paul S. Peercy Sandia National Laboratories Robert 1. Scace National Institute of Standards& Technology

**David Watkins** Los Alamos National Laboratory

**Owen P. Williams** Motorola, Incorporated

Edward D. Wolf Cornell University

**NOTE:** OTA appreciates and is grateful for the valuable assistance and thoughtful critiques provided by the laboratory review panel, The panel does not, however, necessarily approve, disapprove, or endorse this report. OTA assumes full responsibility for the report and the accuracy of its contents.

### **Project Staff**

Peter D. Blair, Assistant Director, OTA Industry, Commerce, and International Security Division

Audrey B. Buyrn, Program Manager Industry, Technology, and Employment Program

Julie Fox Gorte, Project Director

Jerry Sheehan

Sean Headrick\*

#### CONTRIBUTORS

Avtar S. Oberai, Contractor

Elizabeth Sheley, Editor

#### ADMINISTRATIVE STAFF

Carol A. Bock, Office Administrator

Diane D. White, Administrative Secretary

#### PUBLISHING STAFF

Mary Lou Higgs, Manager, Publishing Services Dorinda Edmondson, Typographer Susan Hoffmeyer, Graphic Design

\*On detail from the U.S. Department of Energy.

## Workshop Participants

Graham Alcott Intel Corporation

Richard Burke Institute for Defense Analyses

Glen T. Cheney SEMI/SEMATECH

Charles Fowler U.S. Department of Energy

**Thomas F. Gannon** Digital Equipment Corporation

Sam Harrell SEMATECH

Mark Hartney Office of Science& Technology Policy

William C. Holton Semiconductor Research Corporation John F. Holtzrichter Lawrence Livermore National Laboratory

Paul M. Horn IBM T.J. Watson Research Center

Dragan Ilic Hewlett-Packard Company

Ashok Kapoor LSI Logic Corp.

**C. Mark Melliar-Smith** AT&T Bell Laboratories

A.S. Oberai Consultant

Paul S. Peercy Sandia National Laboratories

Daniel J. Radak Science Applications International Corporation Robert 1. Scace National Institute of Standards & Technology

**David Watkins** Los Alamos National Laboratory

Robert M. White Carnegie Mellon University

**Owen P. Williams** Motorola, Incorporated

Edward D. Wolf Cornell University

**NOTE:** OTA appreciates and is grateful for the valuable assistance and thoughtful critiques provided by the workshop participants. The workshop participants do not, however, necessarily approve, disapprove, or endorse this report. OTA assumes full responsibility for the report and the accuracy of its contents.

### Contents

#### Summary and Policy Discussion 1 Background of this Report 7 Policy Issues 8

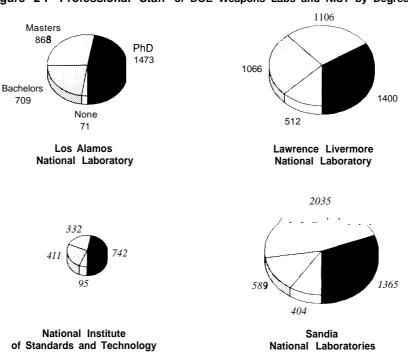

#### 2 Laboratory Capabilities 24

Laboratory/Industry Collaboration 25 Semiconductor Programs at the Four Labs *30* Coordination of Lab Activities *48*

#### 3 The Semiconductor Industry 52

A Strategic Industry 53

Competitive History of the U.S. Semiconductor Industry 56

Future Challenges to the U.S. Semiconductor Industry 68

Alternatives for Future R&D 77

INDEX 80

### Summary and Policy Discussion 1

he federal laboratories possess resources, technologies, and talents that could contribute to the development of semiconductor product and production technologies. Whether they will be able to is uncertain. In particular, the three Department of Energy (DOE) weapons laboratories and the National Institute of Standards and Technology (NIST) are well positioned to contribute to advancing technologies; all four currently participate in R&D partnerships with industry. While the extent of that participation varies greatly among the laboratories, it is clear from OTA's evaluation that there is room for all four labs to expand these partnerships without treading on the toes of other laboratories (private or public), but only if the effort is managed properly.

However, there are several issues that must be resolved if those contributions are to be made in effective, efficient, and synergistic ways. It is quite unlikely that the labs' most effective contributions will happen automatically, notwithstanding the interest among both lab and industry representatives regarding current R&D partnerships. The thorniest issues are:

developing an effective means of managing the disparate efforts of labs and industry so as to make the greatest possible contribution to commercial technology development, while the labs continue to work on microelectronics in connection with public missions;

<sup>&</sup>lt;sup>1</sup>For the purposes of this report, these are Livermore, Los Alamos, and Sandia National Laboratories. The Y-12 plant at Oak Ridge National Laboratory is included as a weapons laboratory in DOE accounts, but it is not comparable to the other weapons laboratories in size or scope of work. Readers not familiar with the semiconductor industry should start this report by reading chapter 3.

- focusing the labs' efforts on the areas in which their contributions are most needed and their talents most suited; and

- assuring a private-sector presence and commitment sufficient to take the hand-off of publicly funded technologies.

In addition, there is some concern over how to minimize competition or redundancy among laboratories and agencies if lab-based microelectronics R&D is expanded. Other policy issues include funding and development of performance criteria for labs' efforts devoted to civilian semiconductor technology. If these issues are not resolved, much of the promise of ongoing R&D agreements between industry and the labs—particularly the DOE labs—may never be realized, and the enthusiasm of both lab and industry representatives for cooperative work could die.

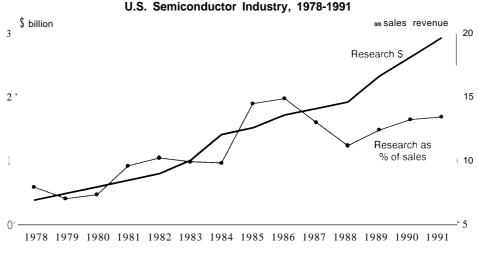

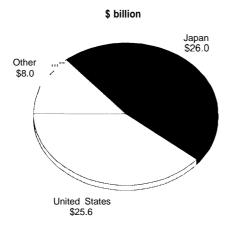

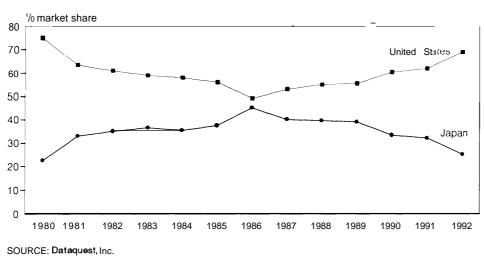

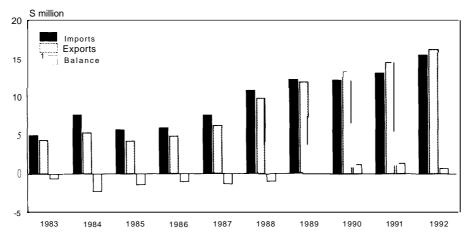

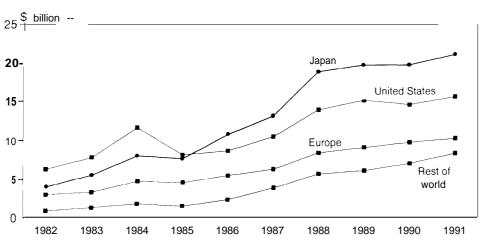

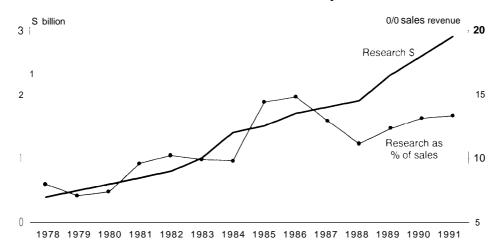

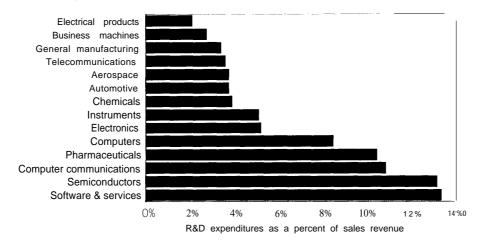

Ten years ago, this loss would have mattered less; private funding for R&D was more abundant, and labs' technologies were perhaps less relevant to commercial needs. Today, however, cooperative technology development between government and industry is more important than at any other time in the postwar period, especially in industries like microelectronics, where R&D costs are escalating more rapidly than revenues (figure 1-1). Many feel that industry's capacity to support escalating costs of technology development is strained; one member of an OTA workshop convened for this assessment asserted that it is becoming difficult for companies to fund the development of the next generation of technology from revenues made on the current generation. The pressure is compounded by rapidly rising plant and equipment costs. Generational changes in semiconductor technology are swift-the Semiconductor Industry Association (S IA) technology roadmaps assume that generational changes will occur every three years, on average, and each new generation entails rapidly escalating expenditures on plant and equipment. Estimates of the cost of wafer fabrication facilities (fabs) stretch to a billion dollars even for the next generation of semiconductors (equivalent to a 64-Megabit DRAM? fab), expected to come on line around 1995.<sup>3</sup>If the costs of new wafer fabs are any predictor of future costs, SIA expects semiconductor revenues to be inadequate to support construction of new fabs beyond 2001.<sup>4</sup> In short, it is becoming increasingly difficult for the industry to find the funds to support both ballooning capital expenditures and rapidly rising R&D costs; cooperative arrangements have been burgeoning as a result.

In the United States, most of the existing cooperative R&D enterprises are private. Semiconductor companies are linked to other companies via an expanding web of technology development and production agreements, many of which span national borders. A few have government support, most notably the industry consortium SEMATECH, which receives half its funding from the Department of Defense (DoD). The impetus for SEMATECH's formation, however, came from the industry itself, as did the Semiconductor Research Corporation (SRC), which was created by the SIA members in 1981. This is a contrast with other semiconductor-producing nations, where government support for commercial semiconductor technology and industrial development has been far more extensive and, in some cases, stretches back more than two decades.<sup>5</sup>

Government support of SEMATECH, originally planned for five years starting in 1987, has

<sup>&</sup>lt;sup>2</sup> DRAM stands for dynamic random access memory.

<sup>&</sup>lt;sup>3</sup>Semiconductor Industry Association Semiconductor Technology: Workshop Conclusions (San Jose, CA: Semiconductor Industry Association 1993), pp. 6 and 18; and Electronic EngineeringTimes, "IEDM Eyes Economics," Sept. 21, 1992.

<sup>&</sup>lt;sup>4</sup> Ibid.

<sup>&#</sup>x27;U.S. support for semiconductor technology development goes back even farther, to the immediate post-World War II years, when the Department of Defense played a key role in the industry's development and growth. However, support for commercial semiconductor technologies has rarely been considered in the United States, and did not become a reality until the mid-1980s.

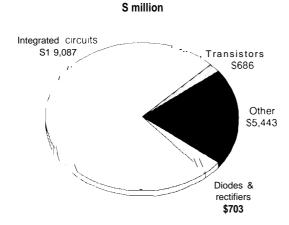

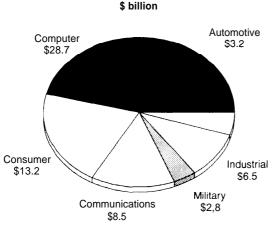

#### Figure I-I—Sales Revenues and R&D Expenditures in the U.S. Semiconductor Industry, 1978-1991

SOURCE: Semiconductor Industry Association, Annual Databook: Global and U.S. Semiconductor Competitive Trends-1978-1991 (San Jose, CA: Semiconductor Industry Association, 1992), p. 41.

been extended at \$100 million in FY 1993 (the same as in earlier years), in addition to ARPA's (the Advanced Research Projects Agency of DoD) funding of approximately \$300 million worth of R&D on microelectronics.<sup>6</sup> Government has also supported a few projects in other consortia, including SRC and the Microelectronics and Computer Technology Corporation, although most of the resources of these consortia are private.

The major purpose of government support and funding for semiconductor technology development has been for the military, and most of that came from the Department of Defense. While a few DoD labs have pursued microelectronics technology R&D, the largest share of military spending on microelectronics has been in the form of research funding in private companies. Both DOE and the Department of Commerce (DOC) have laboratories, and DOE's in particular are large and well-equipped. Until the end of the Cold War, DOE's work in semiconductor and microelectronics technologies was mostly related to nuclear weapons, and not very much of it was aimed at or available to commercial integrated circuit manufacturers. Now, however, the DOE labs are being encouraged to work with industry in cooperative R&D programs, and as industry and lab researchers become more familiar with each other's resources and abilities, enthusiasm for joint projects has permeated the working levels as well.

A new form of cooperative arrangement is now emerging. In this new arrangement, which often takes the form of a cooperative research and development agreement (CRADA), researchers at government labs and in private industry work together to solve problems of mutual interest, usually without any money changing hands. DOE labs gained authority to execute CRADAs in late 1989, and since then the CRADA has become the primary vehicle for cooperative R&D with industry.<sup>7</sup>NIST, with longer-standing ties to industrial technologies, has had CRADA authority since

<sup>6</sup> Not all this money goes to projects that benefit Commercial semiconductor production as ARPA must look after DoD's special needs for semiconductor technology. However, ARPA's mission is also strongly dual-use, and many of ARPA's projects help advance commercial technologies as well.

<sup>&</sup>lt;sup>7</sup>For a more complete discussion of DOE CRADA activities, opportunities, and problems, see U.S. Congress, Office of Technology Assessment, *Defense Conversion: Redirecting R&D*, OTA-ITE-552 (Washington DC: U.S. Governent Printing Office, May 1993).

#### 4 Contributions of DOE Weapons Labs and NIST to Semiconductor Technology

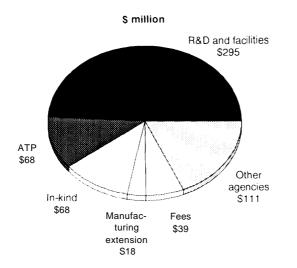

1986, in addition to nine decades' experience in working on problems of a commercial nature.<sup>8</sup> NIST's labs are a national repository of metrology<sup>9</sup> technologies, and they have had productive interactions (using many mechanisms, not just CRADAs) with the semiconductor industry stretching back more than three decades.

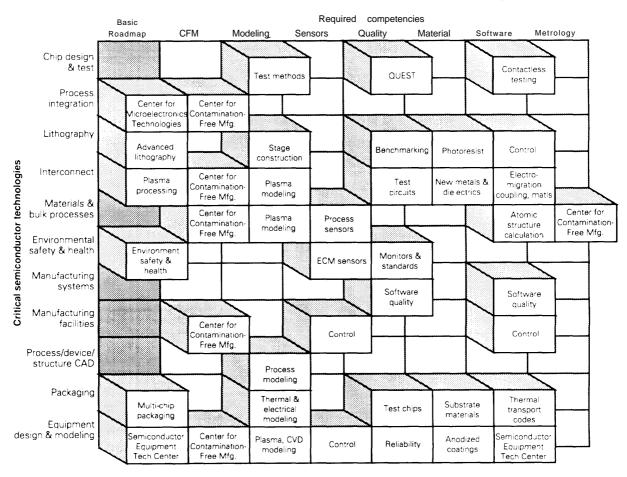

All four labs have CRADAs with industry in microelectronics. The DOE labs report that the value of DOE finds committed to CRADAs with the U.S. semiconductor industry, as of summer 1993, is over \$110 million. The underpinning of these efforts is approximately \$100 million worth of existing program efforts in microelectronics at the three DOE laboratories,<sup>10</sup> and \$9.5 million in internal funds and \$7.8 million in Advanced Technology Program funds at NIST<sup>11</sup> In the course of pursuing its mission, each laboratory has developed some competencies that semiconductor industry representatives believe could contribute to technological advance, in direct support of the SIA technology roadmaps, if properly managed (see ch. 2 for a discussion of core competencies, and box 1-A for a discussion of the SIA roadmaps).

In addition, several interagency and consortia/ agency efforts have begun. Sandia and NIST have a memorandum of agreement (MOA) governing the two labs' collaborative efforts in a number of technology areas.<sup>12</sup> SRC, which manages re-

search for a consortium of semiconductor companies, is trying to initiate CRADAs with all three DOE weapons laboratories; Los Alamos is an SRC member.<sup>13</sup> Defense Programs, at DOE headquarters, recently began to explore the feasibility of SRC coordinating the various cooperative research projects at all the DOE weapons labs on soft x-ray projection lithography, a technology that, if it proves viable and cost-effective, could be ready for commercial use by 2007.<sup>14</sup> SEMA-TECH has had a cooperative research agreement with Sandia for several years, and initiated anew, \$100-million, five-year agreement in early 1993. At the end of August 1993, the agreement included over 20 projects, such as tool benchmarking and characterization, materials and manufacturing process modeling and development, metrology, and contamination-free manufacturing.

Unfortunately, CRADAs have proven timeconsuming and troublesome to initiate at DOE (NEST'S CRADA process is much swifter and more predictable, in part because the legislation governing CRADA authority at NIST makes the process simpler than DOE's CRADA authority). Most DOE CRADAs, particularly those with weapons labs, still take over eight months to start after submission of a work proposal, which itself may take many months for industry researchers to prepare. Some of the reasons for this are the fault of the agency or the labs, though some are not

<sup>&</sup>lt;sup>8</sup>Most of **NIST's** work is and has been commercial, but the **NIST** labs have had substantially greater military funding in the past. In both World Wars, **NIST's** work was heavily oriented to military work. See Nelson Robert Kellogg, *Gauging the Nation: Samuel Wesley Stratton* and the Invention of the National Bureau of Standards, Ph.D. Dissertation The Johns Hopkins University, 1992.

<sup>9</sup> Metrology is the science of measurement.

<sup>10</sup> Avtar s. Oberai, "The OTA Report on Federal Labs and the Semiconductor Industry," Contractor report for the Office of Technology Assessment, June 1993, p. 60.

<sup>11</sup> The Advanced Technology Program (ATP) is a program of mostly private research, of which about half is funded by NIST.NIST holds competitions for ATP funding, and selects from among proposals made by private, university, and occasionally government researchers in a variety of fields. ATP projects do not involve NIST research or onsite research at NIST.

<sup>12</sup> These areas include development of advanced packaging technology, procedures and standards for characterizing lithography tools, techniques for model verification, and methods to improve integrated circuit performance, yield, and reliability. Source: "Memorandu of Agreement between the National Institute for Standards and Technology and Sandia National Laboratories," March 16, 1993, mimeo.

<sup>13</sup> Sandia has been a member in the past, but is no longer.

<sup>14</sup> Personal communication with William C. Holton, Vice President, Research Operations, Semiconductor Research Corporation, July14, 1993.

#### Box 1-A-The SIA Roadmaps

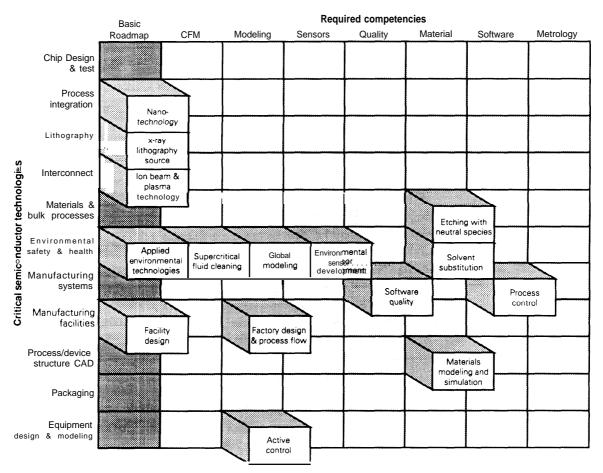

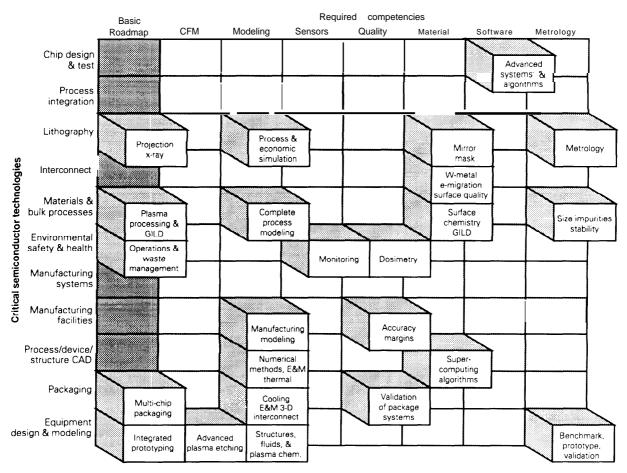

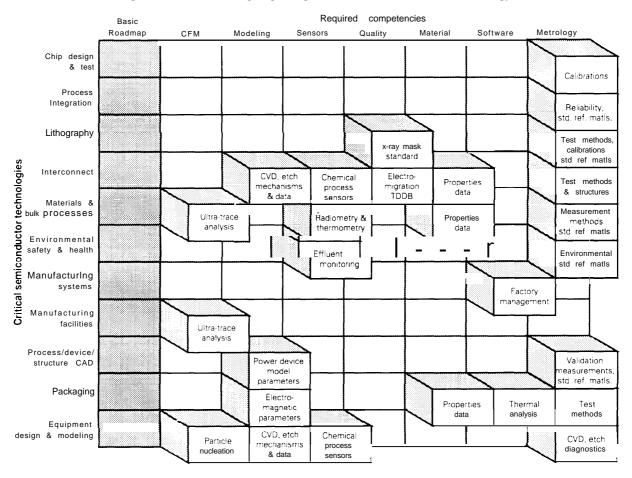

Over the past decade and a half, the Semiconductor Industry Association (SIA) has played an increasingly important role in supporting the industry's competitiveness. The very formation of the association was at least partly a response to the rise of Japanese competition; so was SIA's initiation of SRC in t he early 1980s and SEMATECH a few years later. Some of the competitive problems of the 1980s have been solved, and SRC and SEMATECH played important roles in many of the solutions. A new set of technical challenges confronts the industry in the 1990s. SIA's response was to convene a group of experts-mostly from the semiconductor industry and its customers, with several academ ics, government experts, and representatives from national laboratories--in late 1992 to "create a common vision of the course of semiconductor technology over the next 15 years."

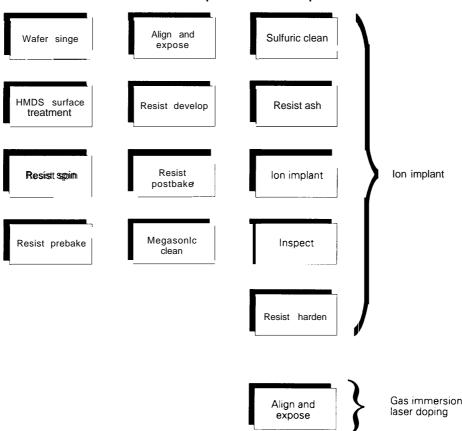

The group, through the course of several meetings and much off-line work, was able to create such a vision, specifying the characteristics of cutting-edge semiconductor technology in 2007, shown in table 3-5. Working groups assembled roadmaps of what efforts would be needed in 11 areas to assure that these technological advances could be made. The 11 areas are chip design and test, process integration, lithography, interconnects, materials and bulk processes, environmental safety and health, manufacturing systems, manufacturing facilities, process/device/structure computer-aided design (CAD), packaging, and equipment design and modeling. The roadmap lays out what performance must be achieved in each area, and what inquiries should be conducted, in order to meet broader semiconductor performance specifications.

The efforts that culminated in the roadmap date back several years. In the late 1980s, the National Advisory Committee on Semiconductors (NACS) examined future technological challenges to the semiconductor industry. This effort was followed by the MicroTech 2000 workshop, which focused on the requirements needed to accelerate technology development by one generation, producing a 1-gigabit static random access memory (SRAM) by the year 2000.<sup>2</sup> Construction of the roadmap was an outgrowth of MicroTech 2000.

SIA plans periodic updates of the roadmap as work underway in industry, academia, and government begins to narrow choices between technology options. Technology forecasts are notoriously unreliable past the short term, and updates and revisions will be needed to keep on track with both planned and unexpected developments in the industry.

<sup>1</sup>Semiconductor Industry Association, *Semiconductor Technology: Workshop Conclusions* (San Jose, CA: Semiconductor Industry Association, 1993) pp. iii-iv.

2 Micro Tech 2000 Workshop Report: A Report to the National Advisory Committee on Semiconductors, August 1991.

(box 1-B). While industry's appetite for joint research with the DOE labs has been unexpectedly vigorous in the four years that the labs have had authority to enter CRADAs, the difficulty and trouble it takes to establish one is frustrating to many industry participants. <sup>15</sup> If Congress or DOE initiates a formal program of R&D aimed at areas

of the SIA roadmaps, creation of a special means of managing cooperative R&D might be necessary. For instance, the Superconductivity Pilot Center Agreement (SPCA) is a means of arranging for cooperative R&D between companies or universities and the DOE labs that maintain Superconductivity Pilot Centers, and they appear

15 See U.s, Congress, Office of Technology Assessment, op. cit., chapters 1, 2, and 4, for a discussion of the CRADA process at DOE.

#### Box 1-B-The DOE CRADA<sup>1</sup>

The cooperative research and development agreement (CRADA) became an accepted way for government, industry, and academic researchers to engage in shared research in the 1980s. Most government laboratories got the authority to initiate CRADAs in 1986, with the passage of the Federal Technology Transfer Act (FTTA). FTTA authorized government-owned, government-operated (GOGO) labs to sign CRADAs with any outside organization, including businesses, nonprofits, and state and local government organizations. Federal Order 12591 of April 1987 authorized the directors of GOGO labs to negotiate the division of funds, services, property, and people with outside organizations in CRADAs, subject to the requirement that labs could contribute in-kind services, but not funds. Under FTTA, NIST labs could initiate CRADAs, and the Federal Order gave lab directors at NIST broad authority to approve agreements. NIST already had many ways of dealing with industry, and maintains many mechanisms still, but the CRADA became an important instrument over the next few years.

DOE's labs are nearly all government-owned, contractor-operated (GOCO) labs, and FTTA did not give them CRADA authority. That authority was granted in 1989, with the passage of the National Competitiveness Technology Transfer Act (NCTTA), and the powers of laboratory directors to enter into CRADAs were substantially different under NCTTA than under FTTA. NCTTA requires GOCO laboratories to gain approval from their departments of both the CRADA (which is a legal document) and a statement of work before initiating a CRADA; GOGOs do not face this requirement. Partly as a result of this requirement, and partly due to unfam iliarity with the process, DOE's CRADA process has proved frustratingly slow to many in industry. Most of the attention has focused on CRADAs with the weapons laboratories, partly because of their large size and resultant visibility, and partly because the lion's share of CRADA money comes through Defense Programs (DP) in DOE, which manages the weapons laboratory, beginning with the submission of a proposal. About half the time typically has been taken for review and ranking of proposals, a process that involves teams from the labs ranking proposals and forwarding prioritized lists to DP for headquarters selection. The other half has been used to negotiate the CRADA

1The information in this box is drawn from U.S. Congress, Office of Technology Assessment, *Defense Conversion: Redirecting R&D*, op. cit., pp. 98-120.

to be working more smoothly than the CRADA process.<sup>16</sup>

Government/private cooperative work to strengthen semiconductor product and process technologies has been helpful in the past and is even more promising today, but several measures could help assure that the program results are timely, useful, and efficient. Industry and lab researchers are interested in cooperative work, and both see that they have much to gain through working together. This enthusiasm is most readily measured by the volume of CRADA activity. But that is not a good measure of the overall success of cooperative R&D, which will depend on finding the right management structure, selecting and using appropriate evaluation criteria, taking steps to improve business plans and industrial strength as well as R&D in weak parts of the industry, selecting appropriate roles and projects for government labs, and providing for adequate funding of the federal part of the effort.

16 For a more complete discussion of SPCAS, see U.S. Congress, Office of Technology Assessment, op. cit., pp. 101-102.

itself. The labs take the lead in the negotiations, subject to guidance and review by DOE field offices and, in some cases, headquarters.

It has become common for critics of the DOE CRADA process to compare it with NIST's swifter, simpler one. This comparison is bot h misleading and unfair, partly due to the differences in authorit y of GOGO and GOCO labs. There are several other reasons for the difference. One is simply that DOE labs' authority to enter into CRADAs coincided with the National Technology Initiative (NTI), a special federal program of the Bush administration to stimulate cooperative technology development between government labs and industry, which generated an unexpectedly large industry interest in CRADAs at a time when DOE and its labs were trying to learn how to manage their new authority. Another factor is magnitude: the three weapons laboratories are the largest federal laboratories in the country, with a combined budget of \$3.4 billion in 1993. NIST's lab budget, in contrast, was \$599 million in FY 1993 (including the Advanced Technology Program). As of mid-1993, the average DOE CRADA involved more than \$800,000 in funding; the average NIST CRADA, \$200,000. By the end of FY 1993, the value of DOE's CRADAs probably will come to around \$400 m ill ion, and t he agency has asked for \$198 m illion in operating funds for DP technology transfer (most of which is expected to go toward CRADAs), a sizable program by any accounting. Considering t hat the DOE CRADA program is barely four years old, it is not surprising t hat the agency and labs have had t heir hands full trying to devise adequate oversight and management mechanisms, and that those mechanisms are not yet streamlined.

However, understanding the reasons for the time involved in initiating an agreement with a DOE lab and being willing to put up with them are hardly the same. Industry CRADA partners quickly grew frustrated with what they perceived as a slow, unpredictable process that required a great deal of effort up front and little confidence that any request for joint work would be funded. Bills in both houses of Congress in mid-1993 aim at streamlining and shortening CRADA approval and negotiation, and the agency and labs continue to try to do so on their own. However, it may still be some time before the process can be brought down to DP's target of four months (if indeed it is done at all), from proposal submission tot he beginning of work, even if this Congress does pass a national laboratories bill. As long as t he process remains as lengthy and, from the standpoint of bidders, unpredictable as it is, companies may become increasingly disenchanted with working with the DOE labs at all, even with tighter R&D budgets.

#### BACKGROUND OF THIS REPORT

OTA was asked by Senator Hollings, in his capacity as chairman of the Senate Commerce Committee and subcommittee chairman of the Senate Committee on Appropriations, to examine how national laboratories could contribute to commercial competitiveness. The primary focus of the request was on two sets of institutions: laboratories that would be closed or downsized as a result of declining defense budgets, and laboratories that already are responsible for supporting commercial competitiveness. At the time, OTA **was** working on its assessment *Defense Conversion: Redirecting R&D*,<sup>17</sup> which focused mainly on potential cutbacks and new roles for the Department of Energy's nuclear weapons laboratories. Both houses of Congress were considering new roles for the DOE labs, and there was some concern that expanding their missions could create redundancies with other laboratories, particularly those of NIST.

17 Ibid.

#### 8 Contributions of DOE Weapons Labs and NIST to Semiconductor Technology

OTA agreed to examine these issues in a selected technology area following the release of *Defense Conversion*. OTA selected semiconductor technology and hired a contractor, Dr. A.S. Oberai, to assemble a team of industry, laboratory, and academic experts to assess the work and potential contributions of the three weapons labs (Livermore, Los Alamos, and Sandia National Laboratories) and NIST. This panel toured and talked with researchers in all four labs<sup>18</sup> and prepared draft sections of a report summarizing their findings.<sup>19</sup>OTA used that report, along with its own evaluations and investigations, to prepare this document.

#### **POLICY ISSUES**

Congress had two main concerns in requesting this work. One was that all federal laboratories position themselves to make more effective contributions to civilian technology development and competitiveness. Another was that unnecessary overlaps between the work of the DOE weapons labs, which are pursuing civilian technology development more enthusiastically than in the past, and NIST, which also is managing rapidly expanding missions, be identified and eliminated. In evaluating these questions, OTA identified several other policy issues that underlie the original two.

#### Management Structure

**In a** CRADA that involves both a company and a lab doing research and no money changing hands,<sup>20</sup> the private company manages its portion of the research, and the public lab manages its share. This is the case with most CRADAs underway at the DOE weapons laboratories and NIST. In the case of DOE, the agency shares with the lab managers (who are not civil servants) responsibility for overseeing the work of the weapons laboratories. This kind of management is appropriate for individual projects, but, for a larger, multi-institutional program aimed at a set of objectives as broad and challenging as the SIA roadmap, probably is not adequate to assure the most effective contributions on the part of any participant. Even within the private sector, broadscale R&D efforts involving many companiessuch as the work of SEMATECH or SRC-have management structures that supersede those of individual companies. R&D programs that include both government and private researchers in joint projects are rare (more typical is federal funding of R&D performed by private sector or university researchers), and there are few examples of an effective management structure for such an effort. If Congress wishes to allocate additional resources at the labs<sup>21</sup> specifically to pursue civilian semiconductor technology development, it could be well worth the effort to devise a new management structure.

<sup>18</sup> Properly speaking, NIST is not one laboratory, but eight. Most of the work relevant to microelectronics and semiconductor technology is carried on in NIST's labs in Gaithersburg, Maryland, and the panel convened in Gaithersburg to hear about and discuss all NIST's microelectronics work. For the purposes of this report, NIST is referred to as one lab.

<sup>19</sup>Oberai, Op. cit. Thedraft and final reports of the panel were assembled and written by Dr. Oberai, using sections that were, in some cases, Written by panel members. Neither Dr. Oberai nor OTA represents this contractor report as a complete consensus; there were many disagreements among panel members, and while most were worked out, a few remain.

<sup>20</sup> Neither DOE nor NIST can pay for outside research through a CRADA. Some CRADAs involve industry, or another outside entity, writing a check for R&D done in a lab, but most DOE CRADAs and many of NIST's involve no exchange of money, The outside partner contributes in-kind R&D, and so does the lab.

<sup>21</sup> This would include not onlythe DOE weapons labs and NIST, but possibly other government labs as well. This study could not include evaluations of all the public or government-owntxi, contractor-operated (GOCO) labs that might contribute to the SIA roadmap, but there are other promising candidates. In 1992, the Army Research Lab's Electronics and Power Sources Directorate signed 21 CRADAs with totat funding of nearly \$4.4 million; some of this work maybe pertinent or adaptable to a government-wide effort to support civilian microelectronics technology development. So, too, is some of the work of MIT's Lincoln Laboratories, which has projects underway in advanced semiconductor technologies, mostly funded by the Air Force.

There is a range of opinion and options on what such a management structure should look like. At one end of the spectrum is the industry advisory panel approach, a model with which many in government are comfortable if not wholly satisfied. Advisory panels are common throughout the federal government, and they have the advantage of being a relatively quick way of getting feedback and advice on the conduct of federal programs from affected groups. However, few in the private sector care for this model, and some in government are growing more disenchanted with it. According to critics, advisory panel membership is unduly constrained by conflict of interest and financial disclosure regulations that often prevent those most interested from serving as advisors over a reasonable span of time. Another source of dissatisfaction, particularly as it applies in this case, is that advisory panels are just that: advisory. Agencies are free to disregard advice they don't agree with or would have a hard time carrying out, and while that may be appropriate in many instances, it is an unpromising approach for managing an extensive, government- and industrywide effort to advance civilian technologies in the national laboratories.

Nonetheless, advisory panels have some attractions. More federal programs now aim at furthering private-sector goals, at least implicitly; without input and feedback from company representatives, it is hard for agencies to execute such responsibilities effectively. Where advisory bodies work well, agencies take seriously the counsel of the panels and yet are not unduly constrained by the wishes of the members, many of whom understand the public missions of the agencies imperfectly, just as federal managers often have a poor understanding of the exigencies of life in the private sector.

A somewhat different approach is being developed in the fall of 1993. Many in both the legislative and executive branches are interested in supporting semiconductor technology development that are broader than SEMATECH or other past programs, and better coordinated than previous federal-private technology development. The defense authorization bill under consideration in the Senate in summer of 1993 contains provisions for the expansion of the Semiconductor Technology Council, intended to foster precompetitive cooperation in technology development among government, industry, and academia, redirect existing federal semiconductor R&D, and evaluate opportunities for new R&D efforts. The Council's functions include:

- advising SEMATECH and the Secretary of Defense on appropriate technology goals for SEMATECH;

- exploring opportunities for improved coordination among industry, government, and academia;

- opening a dialogue on new technology challenges;

- identifying gaps or redundancies in existing public and private R&D programs;

- assessing the progress of existing R&D in terms of the goals of the technology roadmap, and helping to update and implement the roadmap; and

- making recommendations regarding the content and scope of federal semiconductor technology development.

Public officials<sup>22</sup> and representatives of industry and academia<sup>23</sup> would serve on the Council.

<sup>22</sup> These would include the Under Secretary of Defense for Acquisition (co-chairman), the Under Secretary of Energy responsible for science and technology matters (a position that could be created in a couple of different ways in separate legislation), the Under Secretary of Commerce for Technology, the Director of the Office of Science and Technology Policy, the Assistant to the President for Economic Policy, and the Director of the National Science Foundation.

<sup>23</sup> There would be four members prominent in the semiconductor device industry, one of whom would serve, with the Under Secretary of Defense for Acquisition as co-chairman; two members prominent in semiconductor equipment and materials industries; one member from the semiconductor user sector, and one member representing an academic institution.

While its role is nominally advisory, the seriousness with which both Congress and the administration are taking the effort to create it would likely give the group more power than a government advisory panel ordinarily has.

That power could evaporate, however, in an administration with a different outlook and goals. While there have been few precedents, the experience of the National Advisory Committee on Semiconductors (NACS) is instructive. Congress established NACS in 1988<sup>24</sup> "to devise and promulgate a national semiconductor strategy. ' Its powers were confined to evaluation and recommendation of actions on the part of Congress and the President, and like the proposed Semiconductor Technology Council, it had no other control over expenditures or policies. Like the Council, NACS drew membership from industry and government. NACS' policy recommendations were considerably broader than those envisioned for the Council. NACS addressed financial, educational, and trade policies as well as technology development, and it made recommendations regarding intellectual property protection and antitrust law and enforcement. NACS, in the succeeding four years, published several reports, many with strong recommendations for action, which were mostly ignored. In some cases, not acting on the recommendations turned out to have been prudent, or at least fortuitous;<sup>26</sup> in others, it might be that the industry would now be better off had NACS' options been enacted. The lesson is that advisory bodies with no other managerial power rely on goodwill and policy compatibility for their effectiveness, and these change.

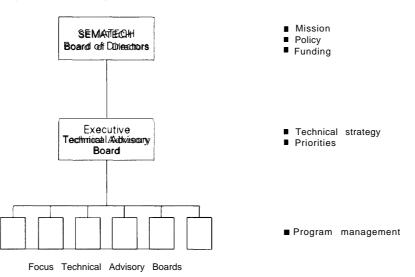

Another management option would therefore be to construct some kind of public/private managerial body with greater power to affect the plans, programs, and fiscal commitments of any cooperative efforts to advance semiconductor technology aimed specifically at following the SIA roadmaps. SEMATECH was set up largely at the urging of the semiconductor industry, and while its funding was half public (through ARPA), the managerial control of the program has been largely in the hands of private-sector managers, though ARPA's influence has always been strong. ARPA has an order in place, in the form of a grant, that references and authorizes SEMA-TECH'S annual plan of work. ARPA has some input to the annual plan, both through SEMA-TECH'S six Focus Technical Advisory Boards (FTABs), which oversee various technology areas, and through a heavy schedule of meetings between SEMATECH and ARPA managers. At the working level, there is little tension between ARPA managers and SEMATECH representatives, but, according to one ARPA representative, there can be tension at the FTAB level, where ARPA sometimes views industry managers as having an excessively short-term outlook, while industry FTAB representatives have the converse view of ARPA managers.

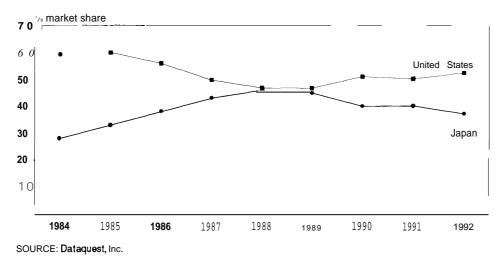

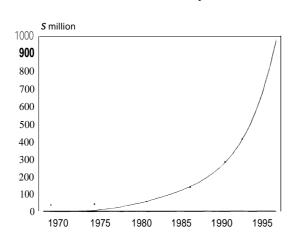

Nevertheless, the process works, though not perfectly; compromises are forged and generally adhered to; moreover, SEMATECH itself has proven effective in helping the U.S. semiconductor industry regain some lost market share and improve the quality and competitiveness in several equipment sectors. Over its frost five years, SEMATECH grew to have closer relationships with ARPA managers, and ARPA representatives frequently attended meetings of SEMATECH's various technical advisory boards (figure 1-2). ARPA is not represented on these boards, but SEMATECH and ARPA planners meet extensively to develop technical plans for SEMA-

U Its organic act wasthe National Advisory Committee on Semiconductor Research and Development Act of 1988 (Public Law 100-410.

<sup>25</sup> National Advisory Committee on Semiconductors, A Strategic Industry At Risk: A Report to the President and Congress From the National Advisory Committee on Semiconductors (Washington DC: November 1989), p. vii.

<sup>26</sup> For example, NACS recommended aggressively pursuing synchrotrons x-ray lithography technology in 1989. In the succeeding few years, other forms of advanced lithography have shown as much or more promise.

#### Figure 1-2—Management and Coordination Structure for SEMATECH

SOURCE: Avtar S. Oberai, "The OTA Report on Federal Labs and the Semiconductor Industry: Partners in Technology," contractor report prepared for OTA, June 1993, p. 67.

TECH's operation. ARPA's opinions are respected at SEMATECH, though its wishes are not always implemented. A prime concern of ARPA, for instance, has been what the agency views as SEMATECH's myopic concentration on nearterm technologies; through years of interaction, ARPA and SEMATECH were able to agree that, beginning in 1994, SEMATECH would devote 20 percent of its funding<sup>27</sup> to longer-term strategic projects with new thrusts (design, test, packaging, and materials).

Using SEMATECH's management structure as a blueprint for management of a public/private research effort aimed at the SIA roadmap probably is both infeasible and impractical. The point of such a research effort is, after all, to develop techniques and technologies that, if they prove feasible, cost-effective, and robust, could be inserted in 5 to 10 years. SEMATECH's concerns are more immediate, and while nearly everyone agrees that SEMATECH is the best vehicle for disseminating technologies that are ready for commercialization, it may not be the best manager for longer-term projects. Moreover, it is very rare for private-sector managers to have as much control over as much public money as SEMA-TECH'S management has had, though the exception has been accepted in SEMATECH's case. For example, one factor that sets SEMATECH apart from a lab-based public/private program is that unlike DOE and NIST, ARPA funds but does not conduct research internally. Whatever the management structure of a civilian semiconductor technology development program, it is unlikely that a wholly or mostly private structure like SEMATECH's would prove acceptable to managers of federal laboratories, or to their agencies. Finally, R&D in the four labs is designed to fulfill both public and private missions. NIST is chartered to do projects aimed frankly at civilian industrial concerns, but even so, there are public missions that NIST must satisfy as well. The DOE weapons labs, in contrast, have until recently aimed almost all their microelectronics work at satisfying defense needs, and while some of it is clearly adaptable to

27 According to a representative of SEMATECH, this means 20 percent of the CONSORTIUM'S total budget, or \$40 million.

civilian concerns, some is not. The end of the Cold War does not mean the end of the DOE labs' responsibilities for defense, and the agency and labs must continue to work on defense electronics. It is unrealistic to expect that DOE, or any other agency whose work could be used in both military and civilian applications, would be willing to turn over significant management of dual-use work to a private-sector team.

The same is true of MST. While NIST has a much longer history of serving civilian needs, some of NIST's work is fundamental science, intended to support the U.S. metrology infrastructure on a time scale beyond industry's immediate needs. NIST managers, along with others in the scientific community, feel strongly the need to protect the agency's freedom to engage in work deemed technically valuable, even if it has no near-term commercial application.

Nevertheless, some private-sector involvement consisting of more than just advice for efforts that are primarily aimed at meeting commercial needs is desirable in this case. Many options are possible, but would mostly be a departure from current practice. If Congress does allocate part of the effort of federal laboratories to cooperative work on the roadmaps as a public mission, some attention to devising such a management structure would be worthwhile. One option is, of course, to channel some responsibility for labs' work pertaining only to the roadmaps through SEMATECH. For example, it might be possible to invest SEMATECH with handling the handoffs of technology from labs (or lab/industry cooperative R&D) to industry when proofs of concept have been established, and the primary need is commercialization. If SEMATECH is to have broader managerial responsibilities, strengthening the influence and power of the federal agencies<sup>28</sup> in the program with SEMATECH might be desirable (though many in SEMATECH

would oppose this). Another would be to put the management of such an effort under the guidance of the STC, or make one of the Council's duties the construction of an appropriate management structure. An intermediate option would be to devise new mechanisms whereby public or company managers could have stronger influence over program planning and funding for the cooperative efforts. Perhaps a public/private/lab management council could be created with a set of duties much like those of the Council, but greater power to influence funding or direction of research programs by voting, after carefully evaluating projects. That, in turn, depends on having a reasonable set of evaluation criteria established in advance, along with appropriate monitoring.

#### Focusing the Efforts of the Laboratories

OTA's panel of experts concurred that there is knowledge and technology in all four labs that could be (and often is) exploited or adapted by the civilian semiconductor industry. What is harder to agree on is how large an effort this should be, or how much of the potential trove of technology to attempt to develop specifically for the needs of the industry. To some extent, the question will answer itself, considering that any company has access to the labs' technologies through several avenues, including contract research, CRADAs, interactions among researchers, site visits, and publications. But that kind of access will not have the same results as a program targeting a few problems that the labs have the best shot at solving. Moreover, the possibilities of redundant projects arising at several labs are greater without an overall strategic focus.

Already, SIA has identified NIST as the primary developer of metrology technologies, and although many other labs can play supporting

<sup>28</sup> This would include all agencies with labs involved in an initiative specifically designed to advance civilian semiconductor technology. For the purpose of this report, those agencies include the Department of Commerce (or at least **NIST**) and DOE.

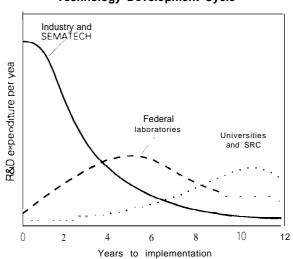

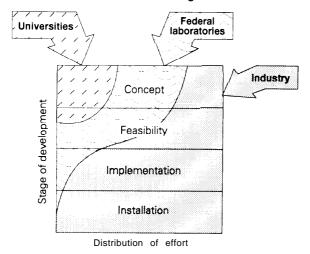

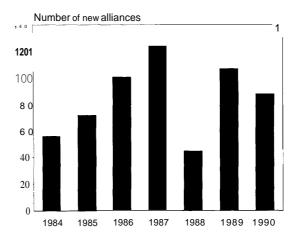

roles,<sup>29</sup> the choice of NIST as lead metrology lab is undisputed. However, there is little consensus now on which of the other laboratories should assume lead roles in other technologies, or even what those technologies should be. There is broad agreement that federal laboratories have a niche in research that is longer-term than industrial R&D and probably not as future-oriented as most academic R&D (figure 1-3), but within this broad framework we have yet to select the handful of initiatives that show the most promise of yielding commercializable results. There is a developing consensus that advanced lithography is an appropriate technology for DOE and other labs to pursue, though no lead lab has been named; a critical mass of opinion is also forming around equipment and manufacturing process modeling, environmentally conscious manufacturing, and cleanup. Again, however, while all the DOE weapons labs are pursuing programs in these areas, no lead responsibilities have been assigned.

If Congress is interested in authorizing a program of shared R&D aimed at furthering civilian semiconductor technology, one option is to select only a few key starting technologies from the plethora of possibilities and devote serious effort to designing appropriate responsibilities and management for them. A modest start might be frustrating to some, but it will be easier to build on a smaller, successful approach and the lessons learned than to make a grand entrance into a new business and risk many failures, always a possibility in a new program and a development almost sure to kill promising approaches as well as false starts.

Another important step is designating lead and supporting responsibilities among laboratories. Many of the talents and resources, particularly in the DOE labs, are complementary, and could be

#### Figure 1-3-Federal Laboratories' Role in the Technology Development Cycle

SOURCE: Avtar S. Oberai, "The OTA Report on Federal Lahs and the Semiconductor Industry: Partners in Technology," contractor report prepared for OTA, June 1993, p. 63.

made to work in a synergistic way if managed properly. DOE headquarters is aware of this, and is trying to formulate appropriate managerial strategies. For example, in August 1993, DP officials were negotiating with SRC to coordinate the labs' work in advanced lithography. DOE is also interested in designating lead labs in technology areas that have garnered a great deal of outside interest. Such efforts are a good beginning, and encouraging them probably is wise. In the absence of higher authorities making some tough decisions about how the labs should coordinate and divide work on civilian technologies, there is a substantial risk that opportunities to capture synergies, or to focus the attention of the labs on the problems they are best able to solve, could be missed. There is competition among the labs, mostly among DOE weapons labs (and sometimes other multiprogram DOE

<sup>&</sup>lt;sup>29</sup>Sandia and NIST are already working together on semiconductor issues under a 1993 Memorandum of Agreement (MOA). Under the MOA, NIST has agreed to develop supporting metrology and associated technology for advanced semiconductor manufacturing tools, assure purity and assess the composition of materials, and assure manufacturing process reliability, Sandia will develop technologies to eliminate contamination, work on developing lithography tools, assist with modeling the next generation of semiconductor products, and provide access to the Center for Microelectronics Technologies (CMT) to serve as a testbed.

labs), but labs affiliated with other agencies are in some cases vying for "their" share of precious budget dollars. Some competition is healthy, but, especially in today's tight fiscal environment, the dangers of unchecked competition probably outweigh the merits.

#### Evaluation Criteria

**Increasing** competition for R&D funding, federal and private, has bolstered the case for development of good performance criteria. R&D is notoriously difficult to evaluate properly. Input measures--e.g. dollars or FTEs<sup>30</sup>--are often the most readily available measures, but they fail to capture the quality or usefulness of the R&D. Output measures, often including data or estimates of the commercial impact of technologies, or return-on-investment calculations, are unalterably judgmental, and are therefore subject to manipulation or bias. Frankly judgmental approaches, such as Delphi techniques, compensate partly by relying on many evaluators, and presumably some of these cancel out; however, research and development communities are still subject to penchants and fashions, despite the reverence of scientists for objectivity. None of this means that thorough, rigorous evaluation of R&D can be avoided; it means that evaluation criteria must be developed carefully, applied rationally, and amended as necessary.

The OTA review panel devised two sets of criteria-one for DOE labs, one for NIST--to use in evaluating whatever R&D programs were undertaken (box 1-C). The panel envisioned a phased approach to the DOE labs' studies aimed at the roadmap. Phase 1 projects include concept or exploratory work, usually averaging \$1 million to \$3 million in size, and aimed at producing technologies whose commercialization could begin 6 or more years in the future. The panel envisioned these as designed to be synergistic with university-based research efforts managed by

SRC, to the extent feasible. Examples might include laser doping, nanometer stage investigation, and low-damage etch processes.

Phase 2 projects would examine technical and commercial feasibility. These projects would average \$3 million to \$10 million, and aim at producing technologies for commercialization three to six years out. Phase 2 projects would be expected to have industry participation (both in conducting and funding the studies), perhaps through SEMATECH. The result of a typical Phase 2 project would be a preproduction prototype technology, such as a lithography tool, a contamination-free manufacturing system, or TCAD (technology computer-aided design) software. The third phase, insertion and implementation, would involve industry much more than labs, both in terms of time and expenditure (see figure 1-4). Phase 3 projects would develop applications of generic skills or capacities to solve identified problems on an as-needed basis. Some of the key evaluation criteria, which the panel called 'return on investment, " address how many projects progress from Phase 1 through 3.

These two sets of criteria were apparently acceptable to OTA's panel, and might serve as interim measures. In OTA's view, however, the two sets of evaluation criteria are mismatched enough that further effort to develop a more consistent set might be warranted. As the lists stand now, DOE's criteria are mainly output- or process-oriented, while NIST's resemble goal or mission statements more than evaluation criteria, with little obvious avenue for feedback other than that provided by MST's ongoing advisory committees. The lack of more explicit measures of performance could be a concern, especially under an expanded, interagency program of cooperative R&D. Conversely, the criteria as written for NIST give it a very tough assignment, one that might not be manageable within the agency's budget in a time of tight fiscal discipline.

<sup>30</sup> Full-time equivalents, a measure of Staff time.

|   | Box I-C—Evaluation Criteria for National Laboratories                                                                                                                                                                                          |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | riteria for DOE Laboratories                                                                                                                                                                                                                   |

|   | <ul> <li>Industry is involved with the labs and vice-versa. Measures could include:         <ul> <li>Number of companies providing resources to the lab programs.</li> </ul> </li> </ul>                                                       |

|   | <ul> <li>-Companies contribute dues (&gt;\$10,000) to acknowledge access to the labs' consulting<br/>capability.</li> </ul>                                                                                                                    |

|   | —Reasonable attendance (>70%) at quarterly update meetings.                                                                                                                                                                                    |

|   | -More than three companies provide significant resources per program.                                                                                                                                                                          |

|   | -Co-principal investigators from the industry.                                                                                                                                                                                                 |

|   | —Significant fraction (>30%) of the work done at industry sites.                                                                                                                                                                               |

|   | . Positive return on investment. Measures could include:                                                                                                                                                                                       |

|   | <ul><li>—&gt;20% of Phase 1 programs move to Phase 2.</li><li>—&gt;25% of Phase 2 programs are commercialized.</li></ul>                                                                                                                       |

|   | —Principal investigators are measured on executing and transfer of technology.                                                                                                                                                                 |

|   | . Mechanisms are established to ensure that programs can be killed if industry doesn't want the technology.                                                                                                                                    |

|   | -Multi-year programs are projected in one-year stages for easy reset.<br>—Industrial partners are signed up within three years.                                                                                                                |

| С | riteria for NIST                                                                                                                                                                                                                               |

|   | <ul> <li>Measurement techniques are provided for all key steps of future semiconductor processin<br/>(examples: gate oxide thickness, photolithography critical dimensions and overlay, contamin<br/>tion levels, device profiles).</li> </ul> |

|   | <ul> <li>Standards and services are provided so that industry can calibrate their measurements wit<br/>NIST.</li> </ul>                                                                                                                        |

|   | . Data are supplied for characterization and validation of the various process, device, and package technology needed to implement the national roadmaps.                                                                                      |

|   | . Where appropriate, NIST provides services to allow the laboratories and industry to do<br>measurements that would allow participants to compare their performance to that of othe<br>participants.                                           |

|   | <ul> <li>Program plans reflect the needs and timing of the national roadmap and are kept up to dat</li> </ul>                                                                                                                                  |

While many of the specific measures suggested for the DOE labs may not be appropriate for NIST, the generalized criteria-significant contact among lab and industry researchers in projects, positive return on investment (not necessarily measured financially), and mechanisms to insure program termination if the technology turns out to be useless to industry--are appropriate as a starting point in developing a more consistent list.<sup>31</sup> It would also be useful to

<sup>&</sup>lt;sup>31</sup> Many lab representatives are, however, concerned about the last criterion (measures to terminate programs when industry is 'ot interested in the technology). Most argue that this provision must be strongly tempered by the labs having flexibility to pursue public missions (including advancement of basic sciences, national defense, energy conservation, and the like) even when industry does not foresee commercial applications. Also, NIST reviewers point out that many of the criteria suggested for DOE labs are already used at NIST, de facto if not formally, There is, according to NIST, already extensive contact between lab and industry scientists and engineers; many NIST projects have been evaluated in terms of return on investment; and mechanisms are in place to assure termination of unuseful programs.

Figure 1-4—Roles of Universities, Federal Laboratories, and Industry in Development of New Technologies

SOURCE: Avtar S. Oberai, "The OTA Report on Federal Labs and the Semiconductor Industry: Partners in Technology," contractor report prepared for OTA, June 1993, p. 59.

consider adding standards for project selection, as well as process and output measures. The task of developing appropriate criteria for anew program of public/private R&D, unusual as such undertakings are, could be daunting, and could require special effort. Several organizations could be directed to look into the matter broadly (e.g., developing criteria for all publicly funded R&D aimed at commercial applications) or narrowly (developing criteria for any special program dedicated to advancing commercial semiconductor technologies). Possibilities include the National Academy of Sciences, creation of a special commission or blue-ribbon panel for the purpose, or (narrowly construed) the Council.

#### Assuring Effective Hand-offs

The success of the whole public-private cooperative R&D effort depends on there being strength on both sides of the relationship. Researchers from labs, industry, and universities must have frequent and close contact, and all parties must work to accommodate everyone's concerns and objectives in program planning and execution. This is less likely to happen if one of the partners is weak.

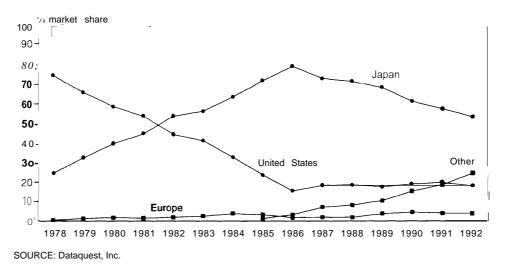

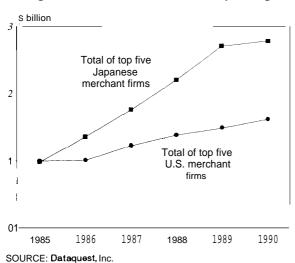

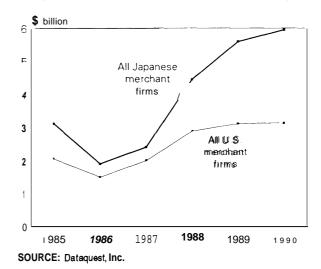

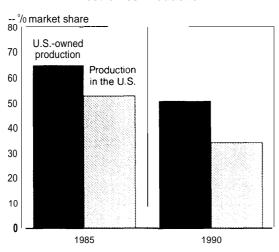

The American semiconductor industry and the materials and equipment industries that support it have had a turbulent decade. Still considered globally dominant in the late 1970s, the industry lost share rapidly in the 1980s in most market segments, mostly to Japanese manufacturers. Since the late 1980s, the industry has revived to some extent, mostly due to private-sector efforts but also due to a couple of government programs, including ARPA's funding half of SEMATECH and (though some would dispute this) the Semiconductor Trade Agreement with Japan (see ch. 3). The improvement can be measured in such terms as the U.S. global share of merchant semiconductor production,<sup>32</sup> which turned up in 1990. Similar upturns occurred in several equipment sectors as well. All analysts caution that some of the upturn in market shares of U.S.-based producers is attributable to the fact that the Japanese market, which Japan-based producers heavily dominate, has undergone a deeper and more protracted recession than the United States in the 1990s. However, there is also a broad consensus that the industry's revival is also due to more sustainable bases, like better technology and greater control and understanding of manufacturing processes.

Several areas remain weak, however. One of the key weaknesses is in lithography equipment.<sup>33</sup> Lithography, according to SIA, is "both the dominant cost factor in wafer processing and the driving technology for increasing chip functionality and, hence, is the primary pacing tech-

<sup>32</sup> Semiconductor sales are commonly measured in terms of merchant and captive sales. Merchant producers are those who sell semiconductors or devices to users, often systems makers; captive production is **intrafirm** production in vertically integrated companies.

<sup>&</sup>lt;sup>33</sup>Lithography is the process by which a pattern is formed in a photosensitive coating that covers a substrate. (SIA,1993, op. cit.) In semiconductor production it is used to pattern the lines connecting various devices on a chip.

nology for industry progress."<sup>34</sup> Yet the U.S. lithography equipment industry has grown weaker over the past decade, going from a 90 percent global market share in 1981 to 10 percent in 1991.35 Concern for maintaining a domestic industry mounted recently as one of the three U.S. companies in the business, GCA, was offered for sale by its parent firm (General Signal) and, when no buyer made an acceptable offer, dissolved. SEMATECH had, for several years, invested millions of dollars in GCA, and SEMATECH experts worked with the company to improve its equipment. Many agree that these efforts met with technical success; GCA's machine, by 1992, was technically comparable to or slightly better than its competition. However, the company still failed.<sup>36</sup>While many in the industry attribute at least some of the failure to management problems at GCA or its parent company, General Signal, it is also true that lithography equipment is a very hard business to stay in, even for a well-managed company. It demands millions of dollars' worth of R&D every year, has a limited market, and is subject to exceptionally fast technological obsolescence. The two Japanese companies that dominate the business, Nikon and Canon, are large,<sup>37</sup> horizontally diversified, and vertically integrated, which means that they can cross-subsidize investmenthungry segments like lithography with the profits from less-demanding segments. Added to that is the fact that, for several decades, capital costs have been lower and investors more patient in Japan than in the United States. Considering too the technical excellence of the Japanese companies, it is easy to see why the lithography equipment business has been so tough for American companies.

There are two left: SVGL (Silicon Valley Group Lithography) and Ultratech Stepper.<sup>38</sup> Ultratech has carved out a market niche in the 1-micron range, which is not state-of-the-art in line width resolution but satisfies the requirements for most of the 25-30 lithography steps currently required in most semiconductor production. The only American company that still is a player on the cutting edge of line-width technology in lithography is SVGL. SVGL resulted from the Silicon Valley Group's purchase of the lithography business of Perkin Elmer, once a prominent manufacturer of lithography equipment. SVGL's new technology, Micrascan, is reportedly very good, and may hold promise for the next generation of semiconductor technology.<sup>39</sup>But SVGL is a small company competing against larger, better-established businesses with deserved reputations for technical excellence and outstanding service. If Micrascan technology does not sell adequately in the next couple of years, SVGL could go the way of Perkin-Elmer and GCA, leaving the world with three stepper companies (Nikon, Canon, and the European company ASM), barring new entrants. SVGL has also received funding and assistance from SEMA-TECH and its members, and the effort, along with SVGL's own expertise, has apparently yielded good interim technical results. But SVGL is in the midst of licensing MicraScan technology to Canon, reportedly in return for licensing fees and some

<sup>34</sup> SIA, op. cit., p. 8.

<sup>35</sup> Semiconductor Industry Association, Semiconductor Technology: Workshop Working Group Reports (San Jose, CA:1993) p. 36.

<sup>36</sup> In 1993, there was som interest in Congress and the Executive branch in mounting a rescue effort for GCA. By this writing, in fall 1993, the company remains defunct, and the passage of time will only increase the difficulty of revival.

<sup>&</sup>lt;sup>37</sup>One company official compared Canon and Nikon to their American competition by saying, "The R&D budget of Nikon is bigger than the annual sales of [the American companies]."

<sup>&</sup>lt;sup>38</sup> There are also several companies exploring advanced lithography, but SVGL and Ultratech are the only producers of optical lithography equipment in the United States.

<sup>&</sup>lt;sup>39</sup>The current generation of leading-edge lithography technology makes line-widths as small as ().35 microns; the next generation, expected to come on line in the late 1990s, is expected to be 0.25 microns.

help from Canon with manufacturing technology.<sup>40</sup> With the disparity in the size, market power, and experience of the two fins, many knowledgeable observers are concerned that SVGL may not survive more than a few years.

In many equipment industries-for example, many segments of the textile equipment industryloss of domestic suppliers has not proven much of a competitive handicap for American firms. In others, the loss of competence and market share in equipment has cost downstream manufacturers dearly. Semiconductor equipment is probably one of the latter. Semiconductor technologies change rapidly, and close relationships with equipment manufacturers are important considering that a few months' lead in installing, debugging, and producing using new equipment can mean a significant edge in market share. Many American equipment suppliers once maintained close relationship with semiconductor and systems producers, relying on customer feedback to help design new equipment and develop new technologies, but as competitive pressures took a toll, many of these ties were frayed. SEMATECH, and its close partnership with the equipment suppliers association (SEMI), helped to restore the productive ties of equipment and chip manufacturers, even in lithography equipment. But unlike in other segments, the efforts in lithography missed the mark. Many reasons for that miss have been advanced; some say that GCA's machines were too late, becoming available later than promised and after major semiconductor manufacturers had made purchasing commitments for the current generation of technology. Some regard GCA's business plans as weak and the fact that CGA's new machines failed to find enough buyers is attributable to a lack of confidence in the company's longevity (if true, of course, this amounted to a self-fulfilling prophecy). Canon and Nikon, in

contrast, are regarded as reliable, competent companies. Whatever the reason, GCA's failure and SVGL's modest position in the market mean that the American stepper industry is still weak, even after a great deal of public and private effort has been devoted to strengthen it.

There is, as usual, a wide range of opinion on what to do. Some would do nothing, assuming that foreign suppliers will go on being as competent and reliable as they have been. But to others, the issue of relying heavily (perhaps exclusively, depending on ASM's performance in the next few years) on two suppliers, and Japanese suppliers in particular, is worrisome. While European semiconductor manufacture has struggled for years to gain a larger toehold on global markets, Japanese competition in semiconductors has improved at an impressive pace. Japanese merchant semiconductor manufacturers held a larger share of the global market than American merchant producers until 1992, and the gap has been narrow in the last couple of years. Canon and Nikon are often reported to have closer relationships with their Japanese customers than with most of their American customers, for obvious historic, geographic, and cultural reasons. Some openly doubt that American firms get equipment as early, or can command the responsiveness to technical adjustments, that their Japanese customers get from Nikon and Canon. Mostly because of the uniquely interconnected networks of businesses that characterize much of Japan's economy, some worry that dependence on Japanese suppliers in particular, and especially in so important a sector as lithography equipment, could be a significant competitive disadvantage.

Public policy has seldom dealt with such issues particularly well. No government department can wield the kind of influence over ongoing business plans and decisions that Japan's Ministry of

<sup>40</sup> The licensing agreement between Canon and SVGL is under review at SEMATECH, and not publicly available as this report is being written. The terms of the agreement as written above arc what many knowledgeable observers believe to be contained in the agreement. According to one source, not only Micrascan technology but the 193-nanometer process, which has even freer resolution and was originally developed at Lincoln Laboratories, is also part of the agreement.

International Trade and Industry (MITI) could when the Japanese semiconductor industry and its attendant equipment sectors were weak. Even if it were possible, differences in situation and environment between the United States now and Japan in the 1960s and 1970s probably make the actual public policy decisions of Japan a poor guide. If, as much of the industry's own analysis indicates, lithography equipment is a key sector in which to maintain strength, it would be prudent to consider all the steps necessary to build that strength. Technology policy is almost never enough, by itself. Though it is not the purpose of this report to examine all the policy choices with respect to key, but weak, sectors, this consideration should be prominent in decisions regarding how the labs can contribute to lithography, and other sectors like it. In short, Congress might wish to consider creating a commission of experts drawn from academia, industry, and government, to analyze key factors that account for the decline of the stepper manufacturing sector in the United States, and to list attendant policy recommendations. This option becomes even more important if the United States continues to support development of advanced lithography technologies, as it has done for many years,

Several agencies have lithography R&D efforts underway. ARPA has supported advanced lithography to the tune of \$75 million in earmarked funds in FY 1993, plus SEMATECH's expenditures on lithography; DOE weapons labs have R&D efforts underway to support their own missions, and NIST has programs designed to permit the domestic semiconductor industry to use lithographic equipment effectively. While most of the work done in the past was in optical lithography, SIA expects some radical shifts in lithography over the next decade or so; examining new approaches to lithography will certainly require tens of millions of dollars (and maybe more) annually for several years, Some of the needed R&D in advanced lithography will be carried on by industry,<sup>41</sup> but exploration of new concepts in lithography (advanced optical, projection and proximity x-ray, e-beam, ion projection, and massively parallel direct write) will not be supported by the private sector at a level sufficient to have any assurance of strength in lithography by the turn of the century.